VDMOS device manufacturing method and VDMOS device

A manufacturing method and device technology, applied in semiconductor/solid-state device manufacturing, semiconductor devices, electrical components, etc., can solve problems affecting the dynamic characteristics of VDMOS devices, and achieve the effect of solving dynamic characteristics and avoiding gate-to-drain capacitance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0056] In order to make the technical problems, technical solutions and advantages to be solved by the present invention clearer, the following will describe in detail with reference to the drawings and specific embodiments.

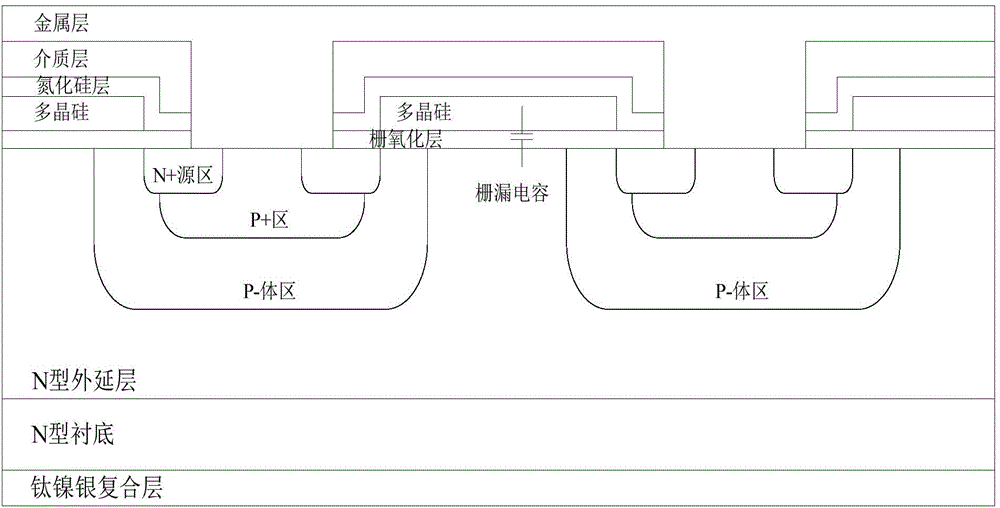

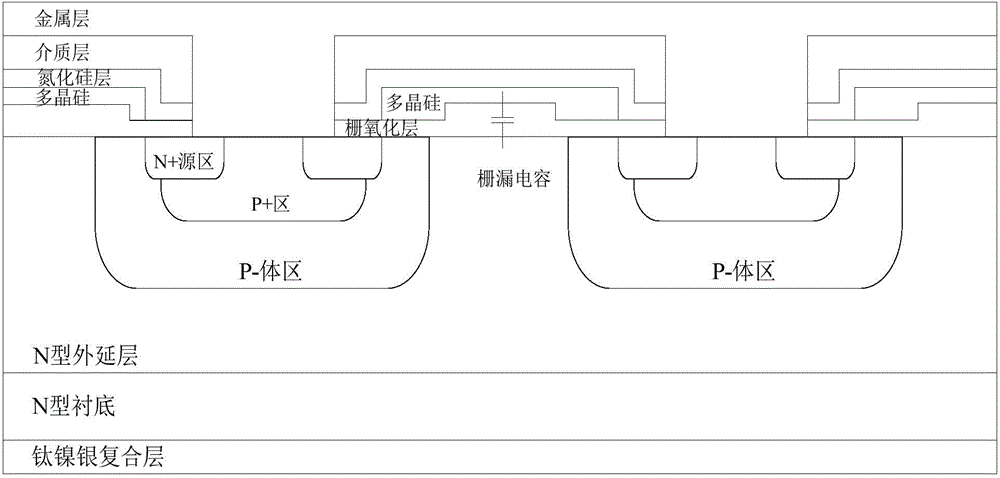

[0057] The present invention aims at the problem that the capacitance between the gate and the drain in the structure of the planar VDMOS device in the prior art affects the dynamic characteristics of the VDMOS device, and provides a method for manufacturing the VDMOS device, such as Figure 3 to Figure 11 shown, including the following steps:

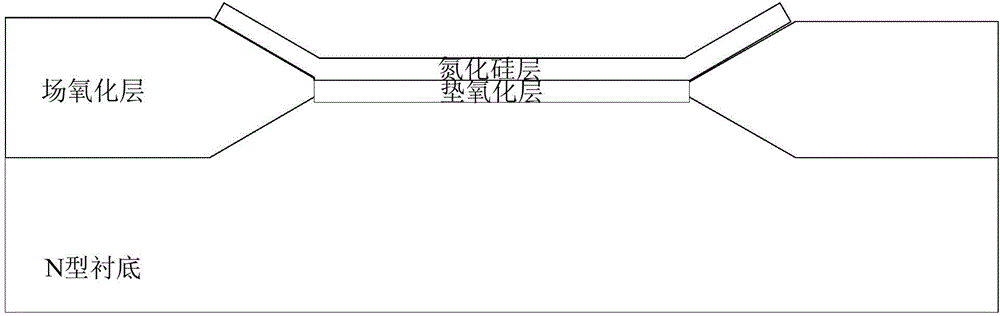

[0058] generating field oxide layers on opposite sides of the first surface of the N-type substrate;

[0059] forming a P-type body region between the field oxide layers on the first surface;

[0060] forming an N-type source region on the P-type body region;

[0061] Etching the field oxide layer to expose the P-type body region;

[0062] forming a gate oxide layer on the basis of the N-type source region;

[...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Thickness | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More