Page or word-erasable composite non-volatile memory

一种存储器、存储器单元的技术,应用在静态存储器、只读存储器、信息存储等方向,能够解决字线和列译码器复杂等问题

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

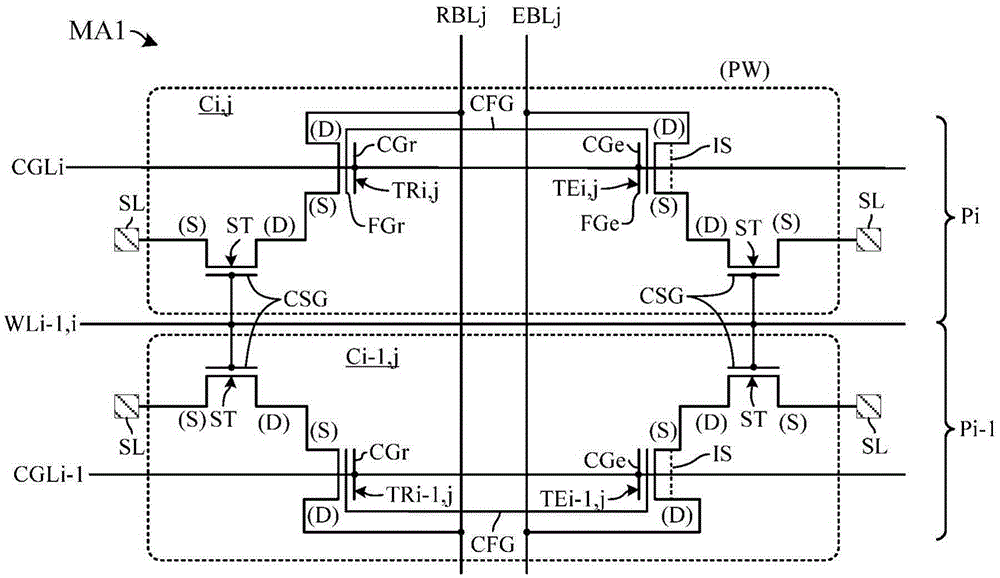

[0044] figure 2 are two memory cells C according to the present disclosure i,j 、C i-1,j and a layout diagram of one embodiment of memory array MA1, derived from figure 1 of memory arrays and memory cell structures in

[0045] Via the first bit line RBL j , the second bit line EBL j , word line WL i-1,i and two control gate lines CGL i 、CGL i-1 , the memory cells are read-accessible, programmable-accessible, and erasable-accessible. memory cell C i,j A physical page P belonging to the memory array i and memory cell C i-1,j belongs to adjacent page P i-1 . Page P i ,P i-1 Various other memory cells may be included and the memory array MA1 may include various other pages.

[0046] memory cell C i,j consists of two floating gate transistors TR i,j 、TE i,j , their floating gates FGr and FGe are interconnected, and the floating gate transistor TR i,j dedicated to read transistor memory cells and the floating gate transistor TE i,j Dedicated to erasing memory cel...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com