Combination readout circuit structure and signal processing readout method of cmos image sensor

An image sensor and readout circuit technology, applied in the field of image sensors, can solve the problems of inability to reduce the speed of the analog output port of the detector, inability to realize pixel merging, limited improvement of the signal-to-noise ratio, etc., so as to avoid the loss of the signal-to-noise ratio and alleviate the Rate pressure, the effect of increasing the working frame rate

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

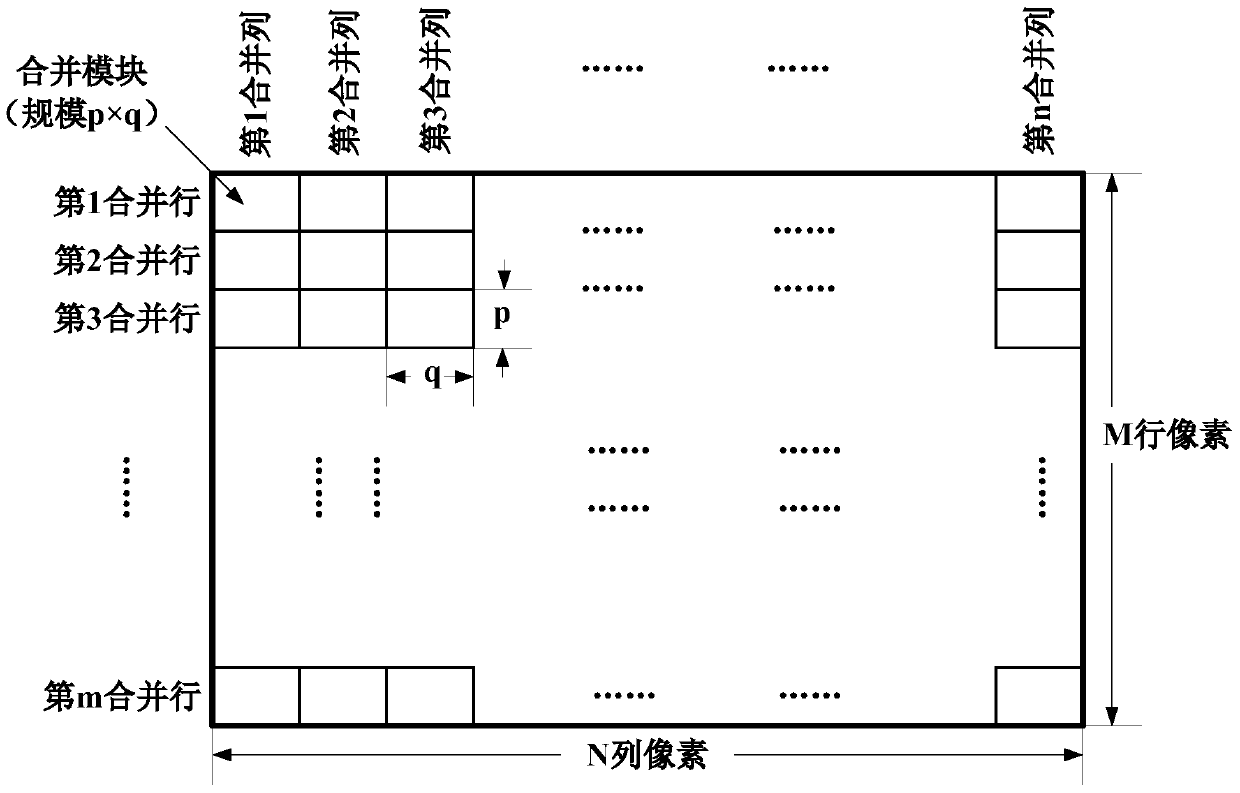

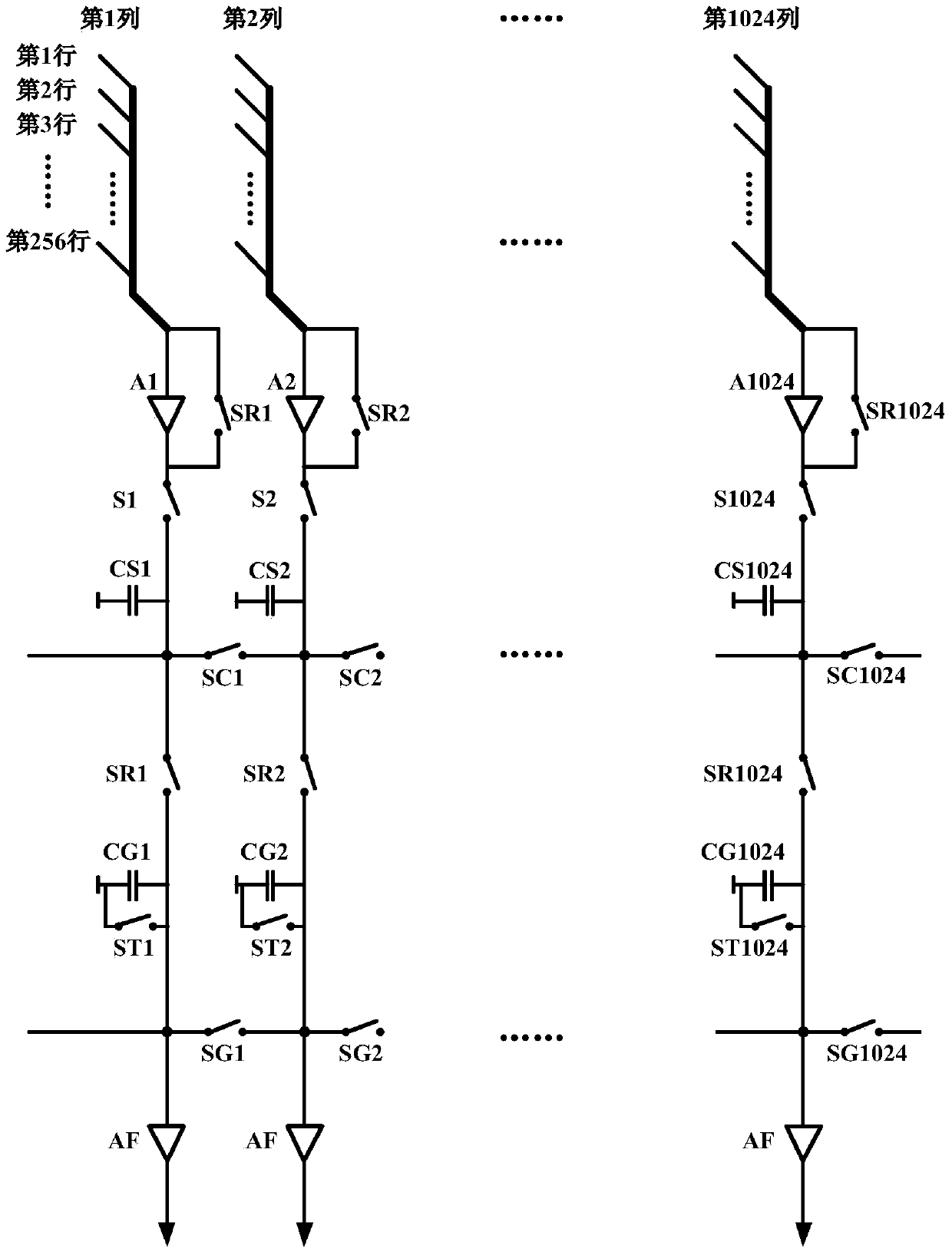

[0026] According to the content of the invention, this embodiment constructs a CMOS detector pixel combination readout structure, the pixel size of the image sensor is 1024×256, 2×2 pixel combination is performed, and the final output size is 512×128.

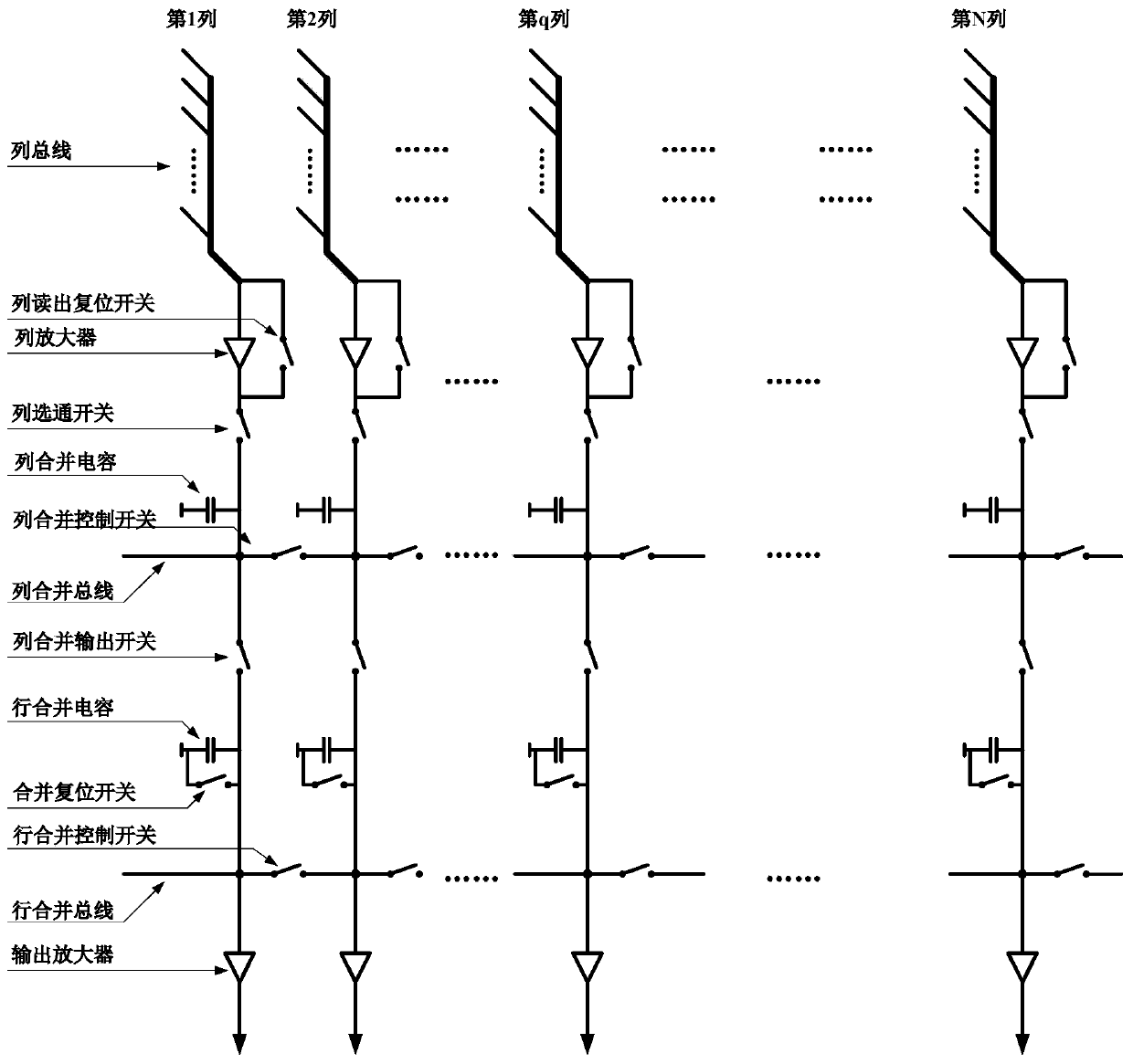

[0027] as attached image 3 As shown, there are 256 rows of detectors in total, and the readout structure includes 1024 column buses, and each column includes column amplifiers (A1~A1024), column gating switches (S1-S1024), column combining capacitors (CS1~CS1024), and column combining Control switch (SC1~SC1024), column merge output switch (SR1~SR1024), row merge capacitor (CG1-CG1024), reset switch (ST1~ST1024), row merge control switch (SG1~SG1024), output amplifier (SG1~ SG1024).

[0028] When the readout structure is changed, the row of the pixels to be merged is sequentially selected by the column bus, and the row and column pixel merge operation is completed through the column merge control switch (SC1~SC1024) and the r...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More