An Optimization Method for Optical Proximity Correction Model

A technology for optical proximity correction and optimization methods, which is applied in optics, originals for opto-mechanical processing, and photoengraving processes for patterned surfaces, and can solve problems such as manufacturing technology failures and distortions.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

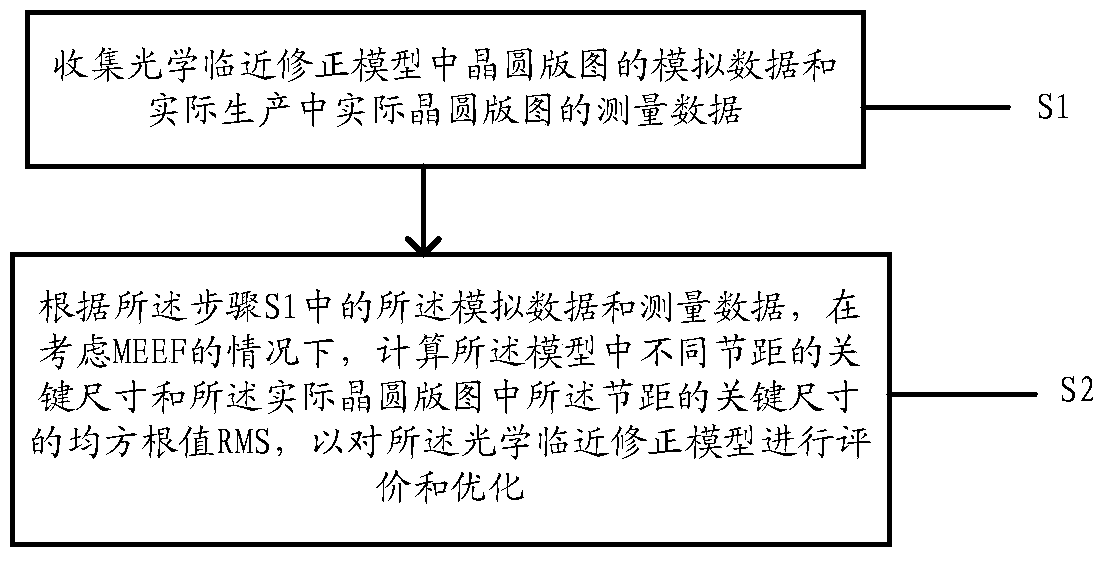

[0049] The method of the present invention will be described in further detail below through an embodiment of the present invention.

[0050] The method described in this embodiment comprises the following steps:

[0051] (1) Carry out the actual production of the wafer, obtain the physical wafer, measure the key dimensions of the corresponding features in the simulation process, and obtain the CD i(测量) ;

[0052] (2) Measure the value of MEEF in the physical wafer to obtain MEEF i ;

[0053] (3) Establish an OPC model according to the target pattern and the measurement results on the actual wafer, select the OPC model for simulation, and measure the key dimensions of different features to obtain CD i(模拟) ;

[0054] (4) select formula 1 to evaluate described simulation result, so that described simulation structure is detected, make OPC final result more reasonable;

[0055]

[0056] Specifically, in step (1), the actual production of the wafer is first carried out to ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More