Fault detection method and apparatus

A fault detection and to-be-detected technology, applied in the field of communications, can solve problems such as detection lines, inability to use walking methods, etc., to achieve the effect of reducing fault detection time and high fault location accuracy

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

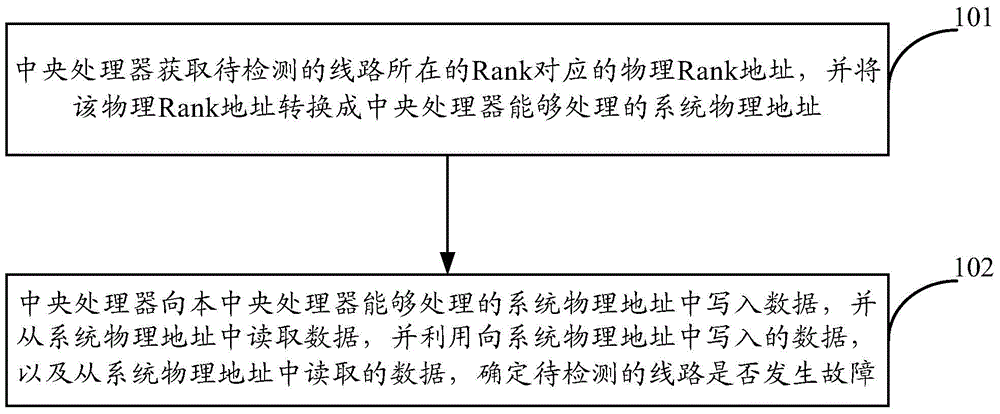

[0034] In order to improve memory access bandwidth, continuous physical address blocks are usually allocated alternately to different Ranks. This allocation process is called interleaving. Rank refers to a group of DRAM (Dynamic Random Access Memory, dynamic random access memory) chips that are connected to gate lines of the same chip and can operate synchronously. The data bit width of one Rank can be 64 bits. When consecutive physical address blocks are allocated to different Ranks alternately, there are three types of addresses. 1. System physical address, that is, the physical address that the CPU can handle; 2. Memory channel address, that is, the address in the memory channel (Channel) of the CPU; 3. Physical Rank address, that is, the address on a single Rank of the memory.

[0035] In the above application scenarios, the address that needs to be detected by the walking method is the physical Rank address, and the address that the CPU can perform write and read operatio...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com