A Method for Simplifying the Realization of Verification Model in Chip Verification

A verification model and chip technology, applied in the field of communication, can solve the problems of consuming a lot of energy, increasing the difficulty of error detection, complex verification model implementation, etc., to achieve the effect of facilitating error detection, simplifying implementation, and saving verification time

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0015] The technical solutions of the embodiments of the present invention will be clearly and completely described below in conjunction with the accompanying drawings of the present invention.

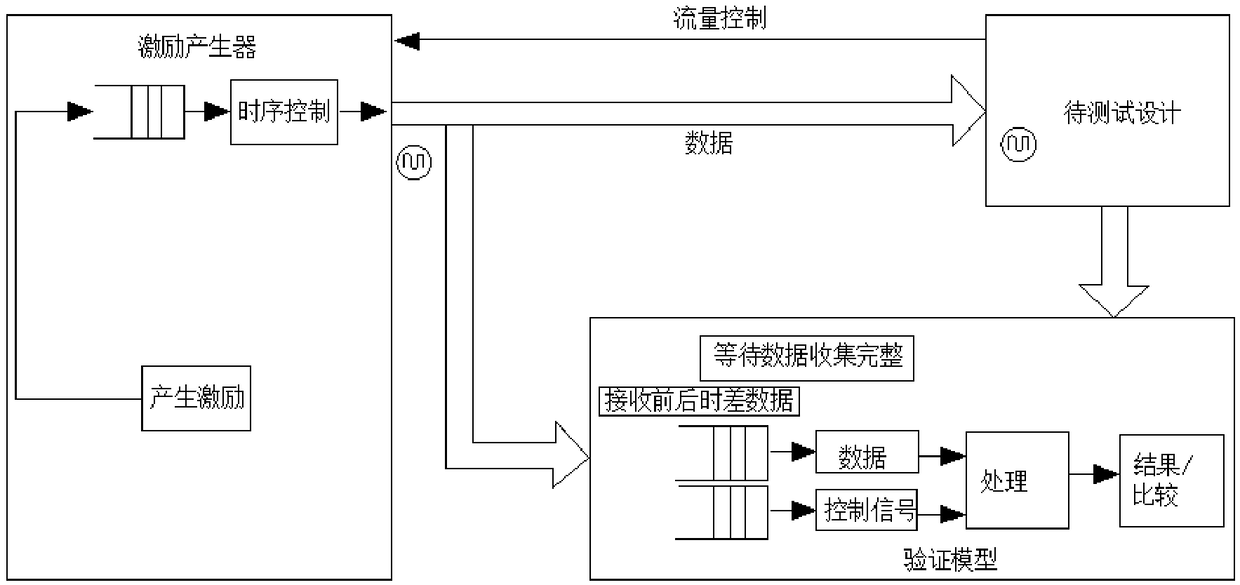

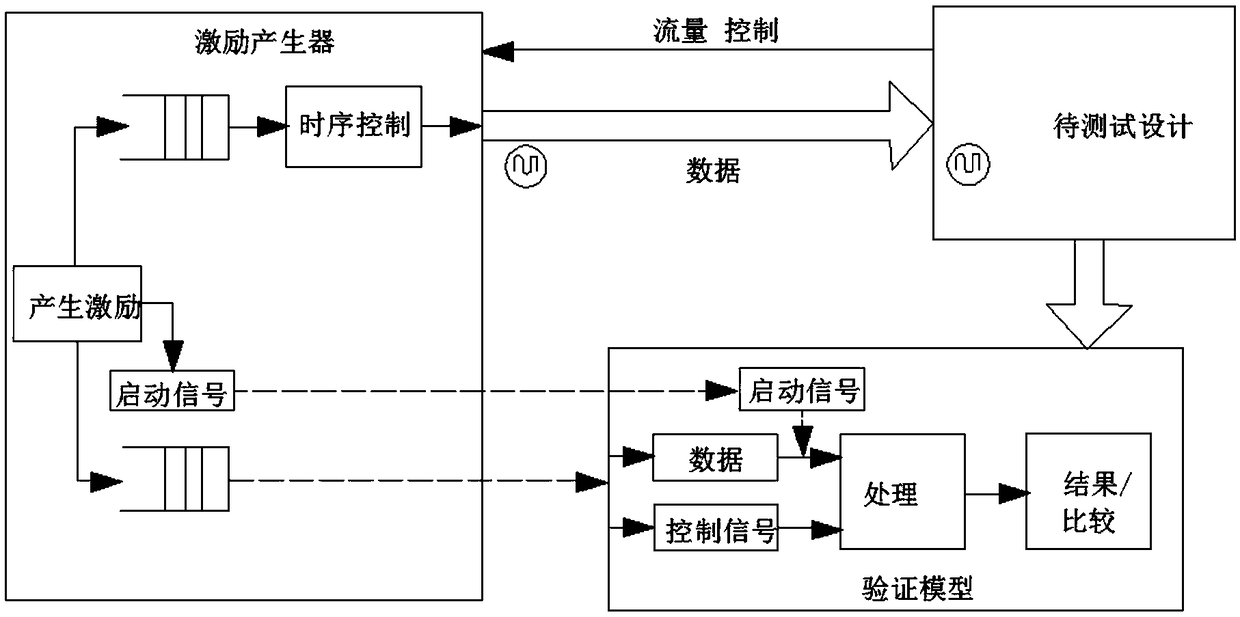

[0016] A method for realizing a simplified verification model in chip verification disclosed by the present invention, the core of which is that the stimulus generator and the verification model work simultaneously at the same time, and after the verification model receives the message data, it can process all The data is then stored in the queue, waiting for data comparison when the output of the design under test is valid.

[0017] Now take the message processing module as an example, such as figure 2 shown, including the following steps:

[0018] First of all, at a certain moment, the stimulus generator generates the start signal, the entire message and the corresponding control signals required to process the message. These message data and signals are stored in two queues insid...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More