A method for manufacturing a deep-groove type super junction device

A manufacturing method and super junction technology, which can be used in semiconductor devices, electrical components, circuits, etc., can solve the problems of substrate doping and external expansion, and achieve the effect of improving reverse breakdown voltage.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

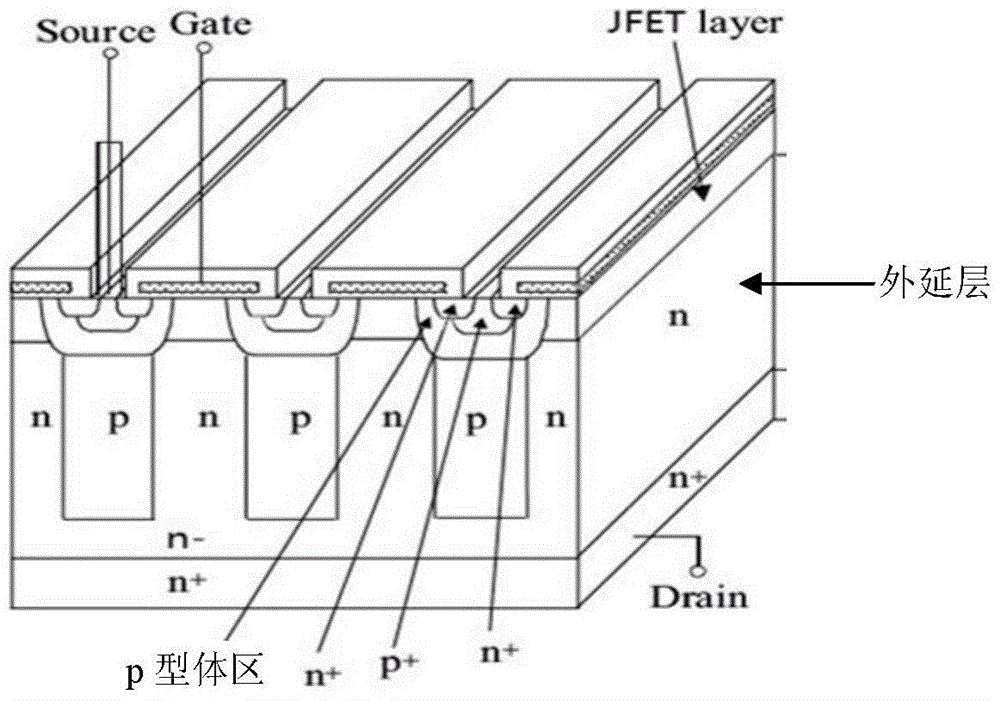

[0048] A method for manufacturing a deep trench type super junction device, comprising the following steps:

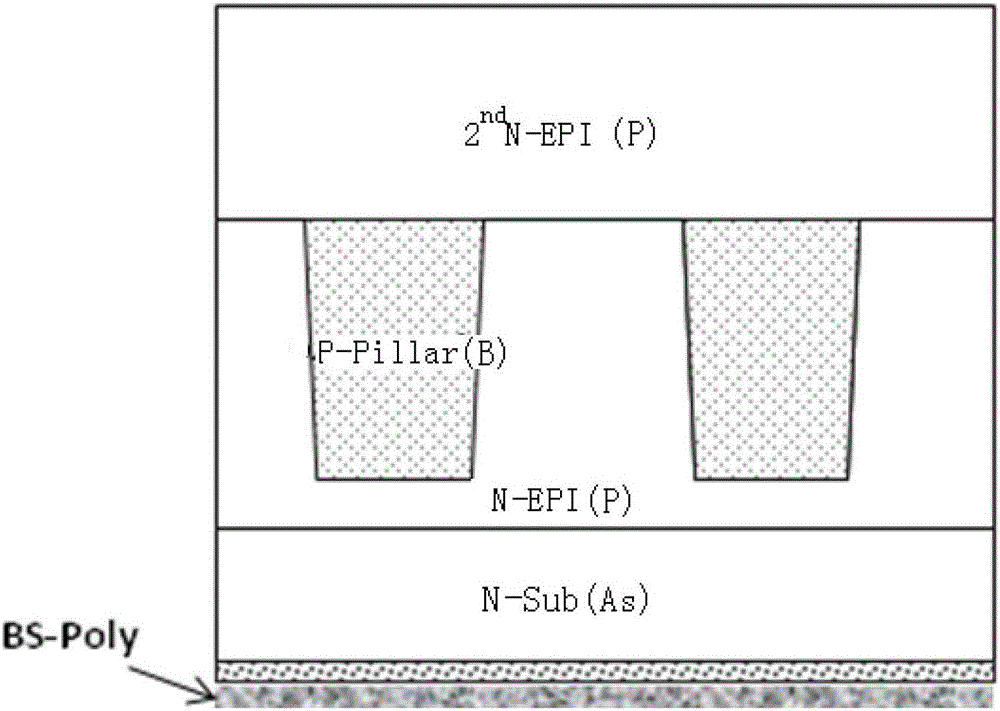

[0049]1. Form a first ONO (Oxide-Nitride-Oxide, oxide layer-nitride layer-oxide layer) dielectric layer 12 on the surface of the first N-type epitaxial layer (1stNEPI) 11 of the wafer (wafer), and the first ONO The dielectric layer 12 is respectively the third silicon oxide, the second silicon nitride, and the first silicon oxide from top to bottom, and the N-type heavily doped substrate (N-SUB) 10 under the first N-type epitaxial layer (NEPI) 11 , under the N-type heavily doped substrate 10 is a low temperature oxide (LTO) 13, under the low temperature oxide (LTO) 13 is a polysilicon layer (Poly) 14, and the low temperature oxide (LTO) 13 and the polysilicon layer (Poly) 14 are back seal, such as Figure 5 shown;

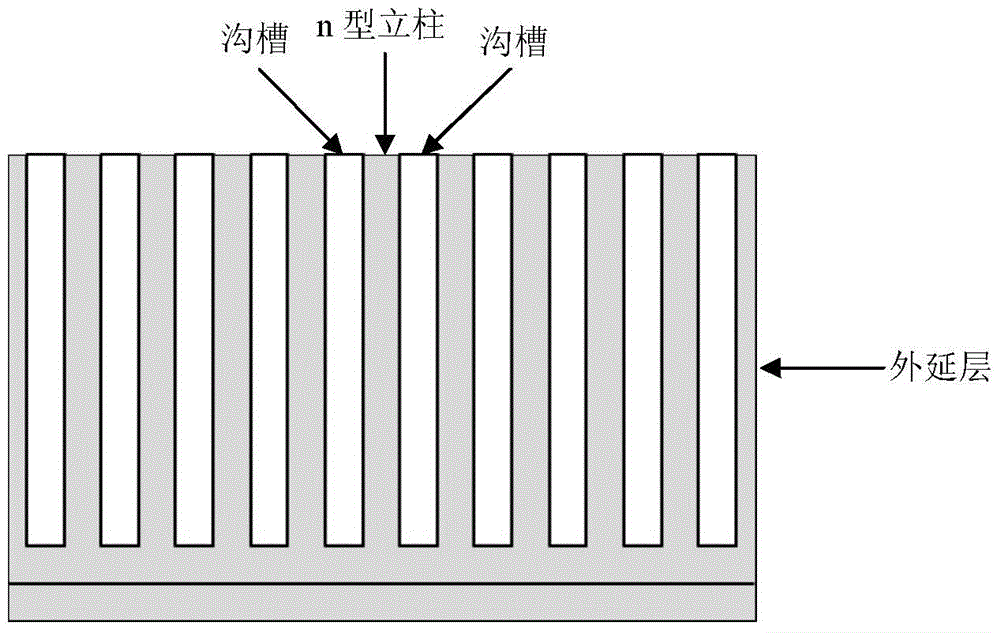

[0050] Two. Adopt the photolithography process to define the pattern of the first layer trench (Trench) on the first ONO dielectric layer 12 with photore...

Embodiment 2

[0062] Based on the manufacturing method of the deep trench super junction device in the first embodiment, the thickness of the low temperature oxide (LTO) in the back seal is about 1000 angstroms to 20000 angstroms, with a typical value of 5000 angstroms.

[0063] The thickness of the polysilicon layer (Poly) in the back seal is about 1000 angstroms to 20000 angstroms, with a typical value of 5000 angstroms.

Embodiment 3

[0065] Based on the manufacturing method of the deep trench type super junction device of the first embodiment, the typical ranges of the thicknesses of the first ONO dielectric layer and the second ONO dielectric layer: the thickness of the third silicon oxide is about 0.5-3um, and the thickness of the second nitride oxide is about 0.5-3um. The thickness of the silicon is about 100-1500 angstroms, and the thickness of the first silicon oxide is about 100-2000 angstroms, which can be increased or decreased according to actual needs.

PUM

| Property | Measurement | Unit |

|---|---|---|

| Thickness | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More