Low-power consumption and accurate sleep timer circuit and method

A low-power, timer technology, applied in electrical components, electronic switches, pulse technology, etc., can solve the problems of processor power consumption, inaccuracy of sleep timing, etc., to improve reliability, reduce processor resource overhead, simple structure

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment

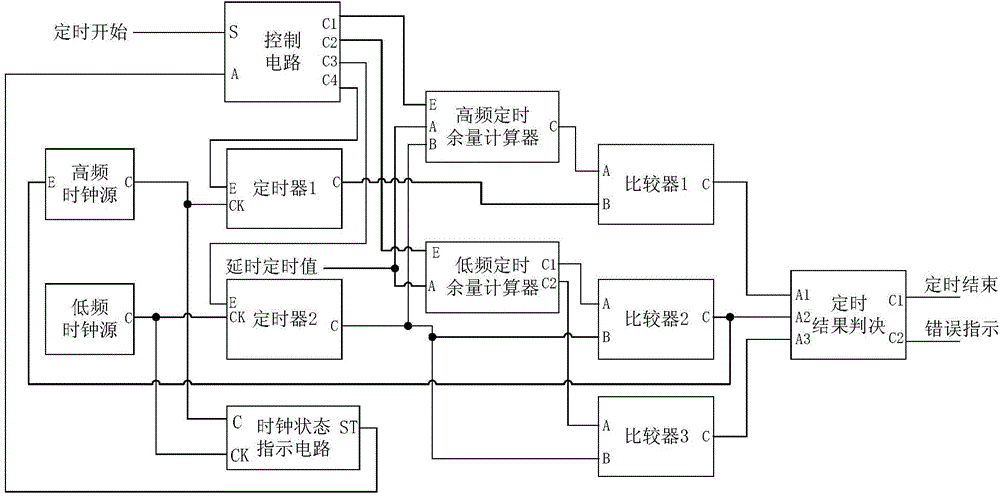

[0149] This embodiment is a way to realize the clock state indication circuit described in this patent, and adopts a relatively simple circuit structure, wherein the value of N in the clock frequency division circuit is 2, that is, adopts 2-equal duty frequency division, shifting The bit register uses a 3-bit register shift register circuit.

[0150] For specific examples, please refer to Figure 4 As shown, a clock state indicating circuit structurally includes a clock frequency division circuit, an edge detection circuit, an edge correction circuit and a shift register circuit; the external port includes an output port reference clock and a clock to be tested, and the output port clock state.

[0151] The specific connection relationship is that the reference clock signal is connected to the clock port CK of the clock frequency division circuit, and the clock output port Q of the clock frequency division circuit generates a frequency-divided clock signal C1; the clock signal...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More