Memory compiler timing sequence simulation method

A simulation method and memory technology, applied in memory systems, software simulation/interpretation/simulation, instruments, etc., can solve problems such as inaccurate timing and achieve the effect of reducing consumption

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0037] The present invention will be further described below in conjunction with the accompanying drawings and specific embodiments, but not as a limitation of the present invention.

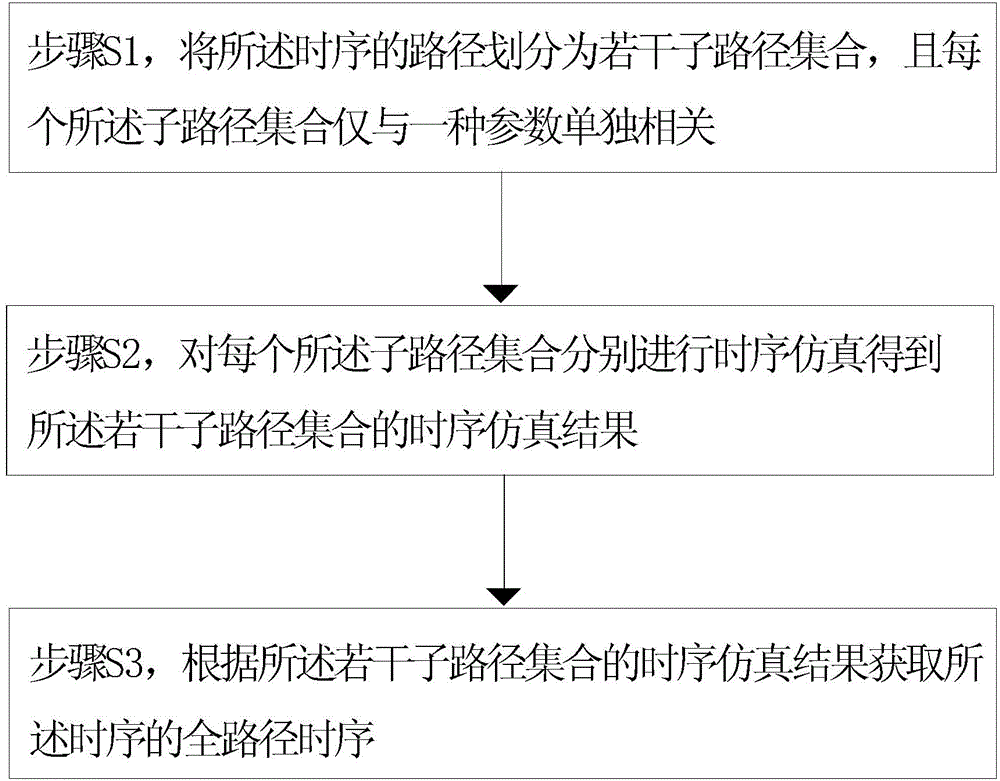

[0038] like image 3 and Figure 4 As shown, the present invention discloses a memory compiler timing simulation method, which is applied to simulate the timing of memory instances generated by the memory compiler. The method specifically includes the following steps:

[0039] Step S1, divide the time-series path into several sub-path sets, and each sub-path set is only related to one kind of parameter.

[0040] In a preferred embodiment of the present invention, the types of the parameters include clock slope, input slope, output load and memory instance capacity, that is to say, the timing path can be divided into clock A set of ramp-dependent subpaths (i.e., a set of subpaths related to the clock ramp) and / or a set of ramp-dependent subpaths at the input (i.e., a set of subpaths related to ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More