Memory access processing method and device

A memory access and processing method technology, applied in the field of memory access processing methods and devices, can solve the problems of reduced memory access performance and high occupancy rate, and achieve the effects of reducing the probability of occurrence of exceptions, reducing occupancy rate, and improving memory access performance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0045] It should be understood that the specific embodiments described here are only used to explain the present invention, not to limit the present invention.

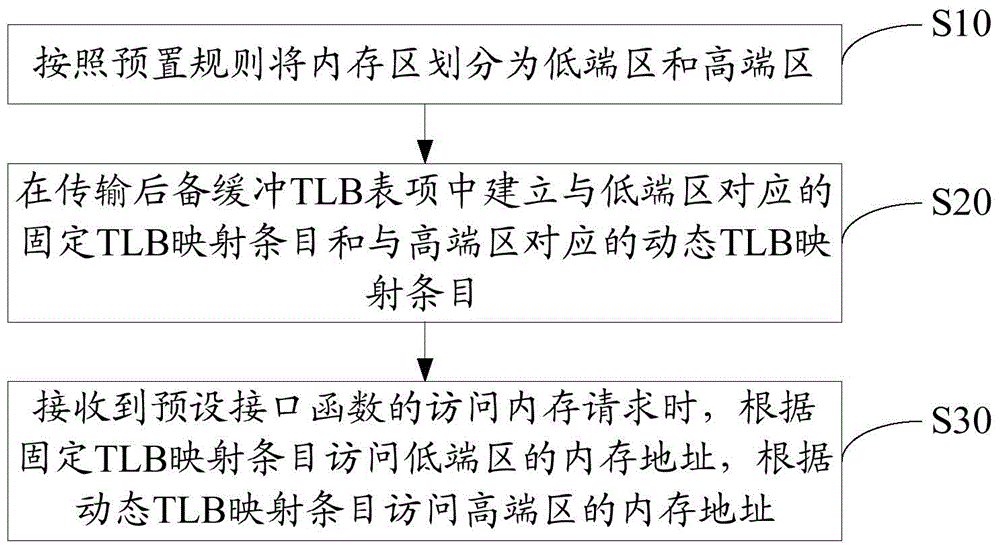

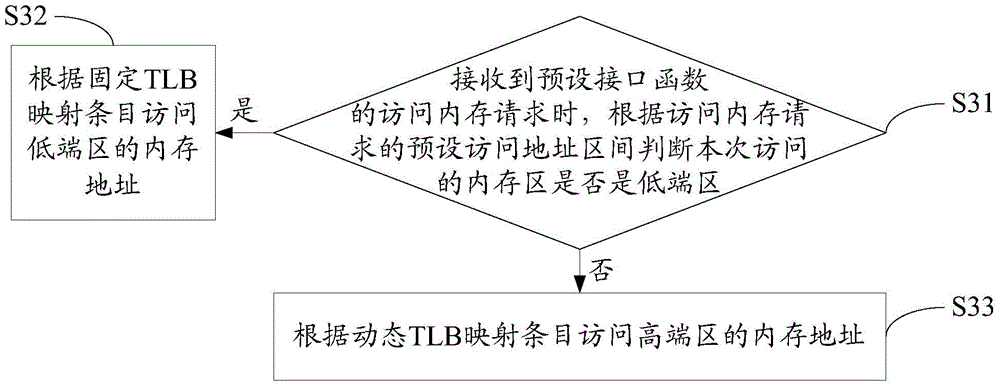

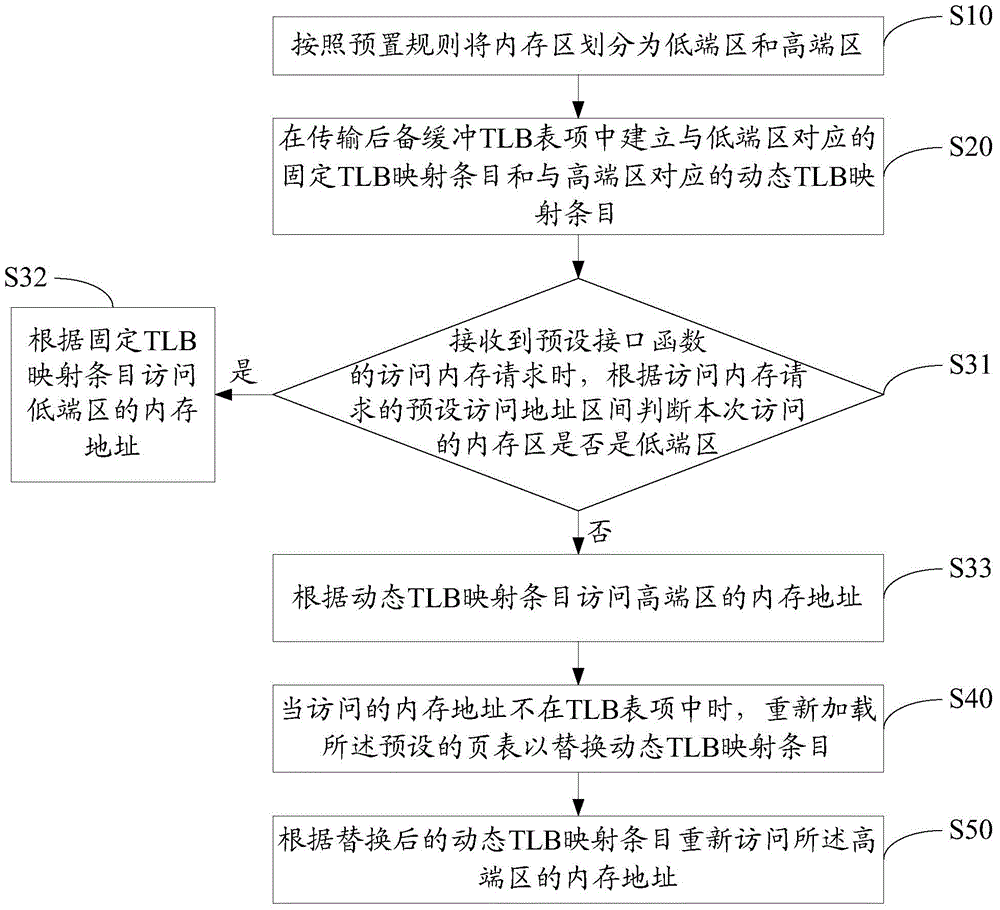

[0046] The present invention provides a memory access processing method, referring to figure 1 , in the first embodiment of the memory access processing method of the present invention, the memory access processing method includes the following steps:

[0047] Step S10, dividing the memory area into a low-end area and a high-end area according to preset rules;

[0048] The memory access processing method provided by the embodiment of the present invention is mainly applied in a computer system to control memory address access. Specifically, the above-mentioned memory division method can be set according to actual needs. In a LINUX system, it is usually divided into a low-end area (LOW area) and a high-end area (HIGH area) according to addresses. For example, when the system memory is initialized, a part of the prese...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More