Method for preventing wafer map from shifting

A wafer and wafer testing technology, applied in the direction of electronic circuit testing, etc., can solve problems such as deviation and misjudgment of qualified chips.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0014] Hereinafter, the present invention will be further described in detail in conjunction with the accompanying drawings: Here, the schematic embodiments of the present invention and their descriptions are used for explanation, but not as a limitation of the present invention.

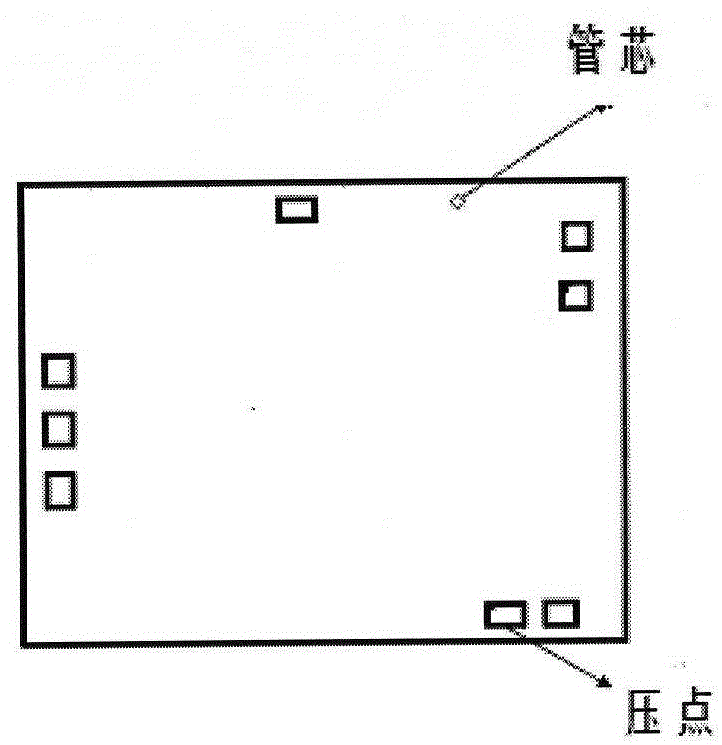

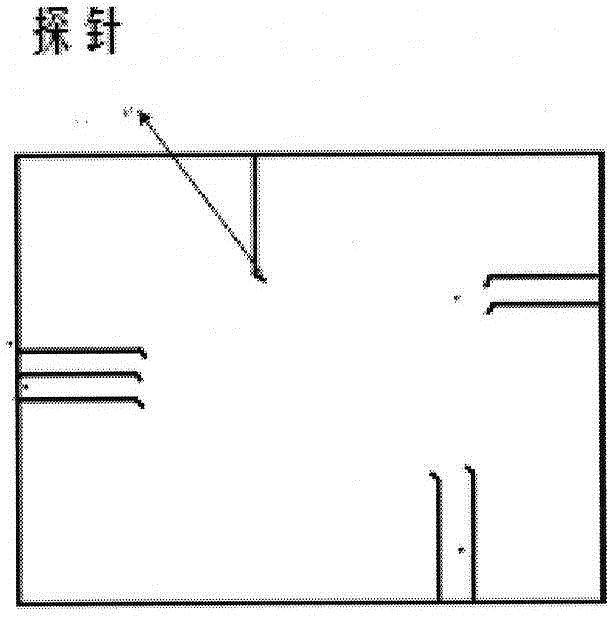

[0015] Take the security chip 16site parallel test as an example, chip pressure points and probes such as figure 1 , 2 shown

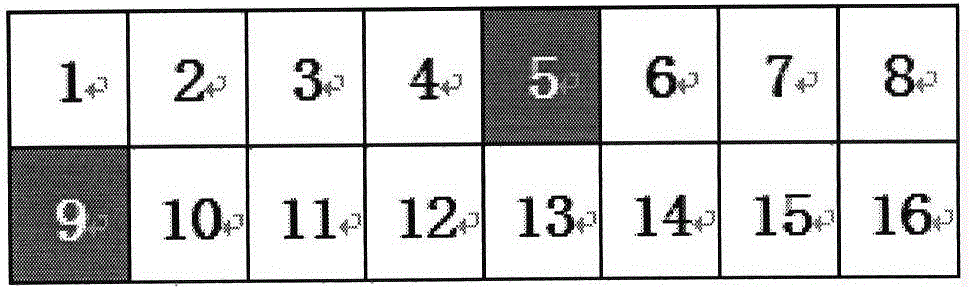

[0016] 1. The arrangement of probe cards is 8x2, such as image 3 shown;

[0017] 2. When performing PTPA, set the absolute position of each needle on the probe card when establishing the program. The position of each needle is determined according to the pressure point on a single chip, so as to ensure that each needle will fall on the chip when testing Corresponding pressure point in the middle.

[0018] 3. The default method of detecting cards and needles of the device is AUTO SELECT (automatic selection mode), and the program will automatically set two positioning si...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More