The Implementation Method of Instruction Cache Consistency Based on Position Correspondence

A technology of corresponding relationship and implementation method, applied in memory systems, instruments, computing, etc., can solve problems affecting performance, low efficiency, lack of I-Cache, etc., and achieve the effect of improving performance and requiring less mutual constraints

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0036] Below in conjunction with specific embodiment, further illustrate the present invention. It should be understood that these examples are only used to illustrate the present invention and are not intended to limit the scope of the present invention. In addition, it should be understood that after reading the teachings of the present invention, those skilled in the art can make various changes or modifications to the present invention, and these equivalent forms also fall within the scope defined by the appended claims of the present application.

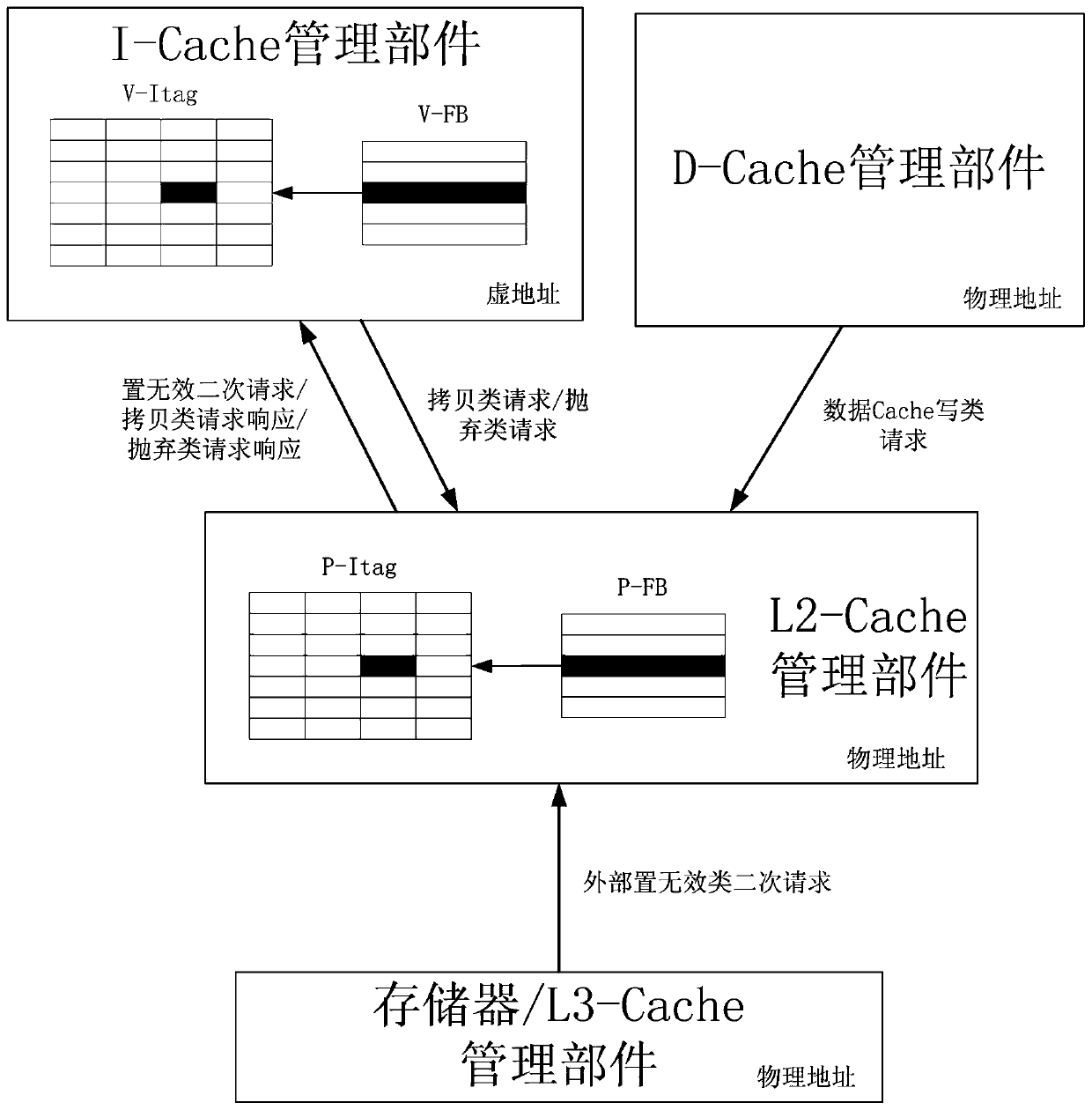

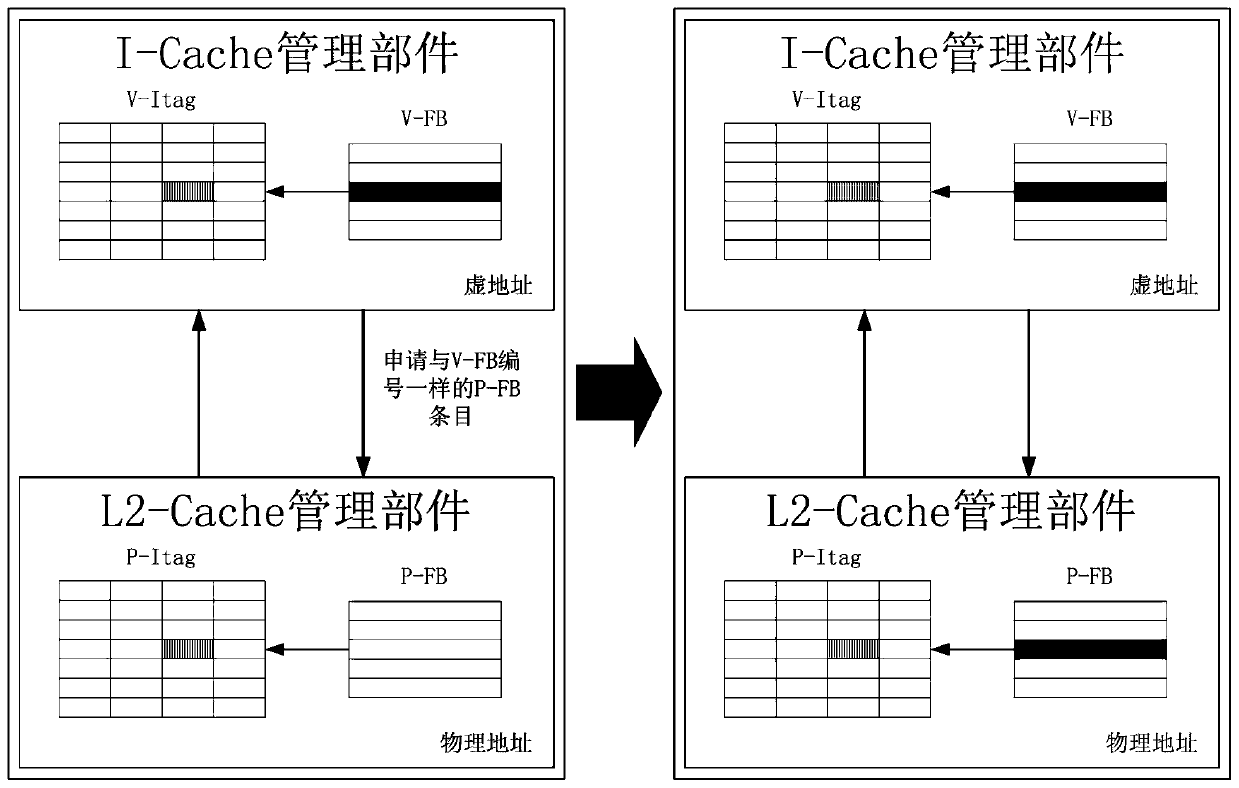

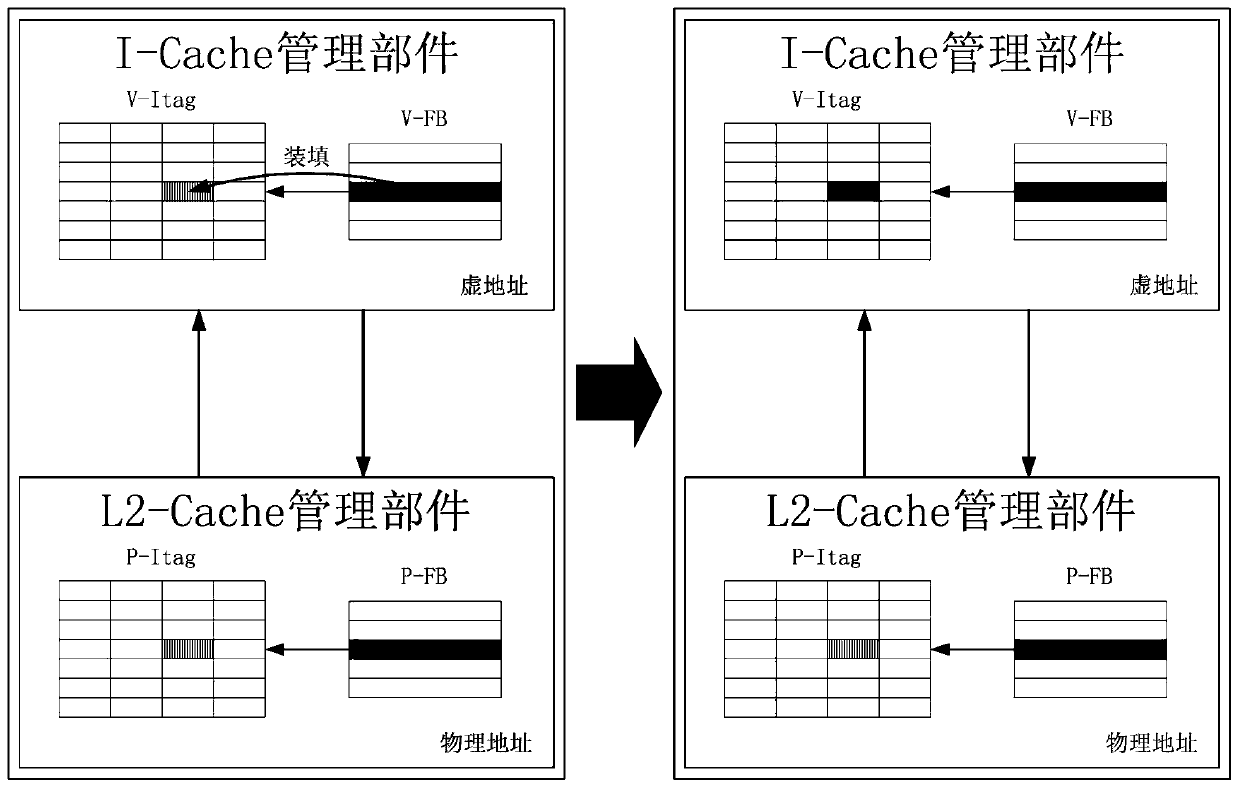

[0037] Embodiments of the present invention relate to a method for implementing instruction Cache coherence based on location correspondence, and the memory hierarchy involved in the present invention is as follows: figure 1 As shown, it includes structures such as I-Cache management unit, D-Cache management unit, L2-Cache management unit, L3-Cache management unit, and memory, and the same organizational structure is set in the...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com