Three-valued 4-81 line address decoder realized by utilizing CNFET

A technology of address decoder and inverter, which is applied in the field of 4-81 line address decoder, can solve problems such as gate delay and interconnection crosstalk

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

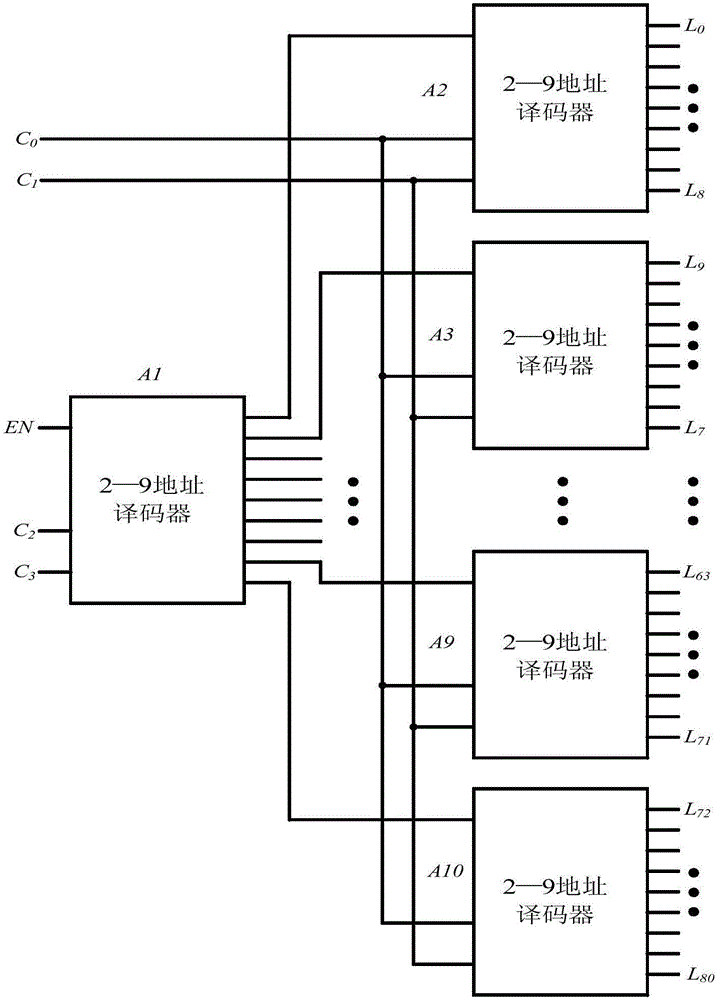

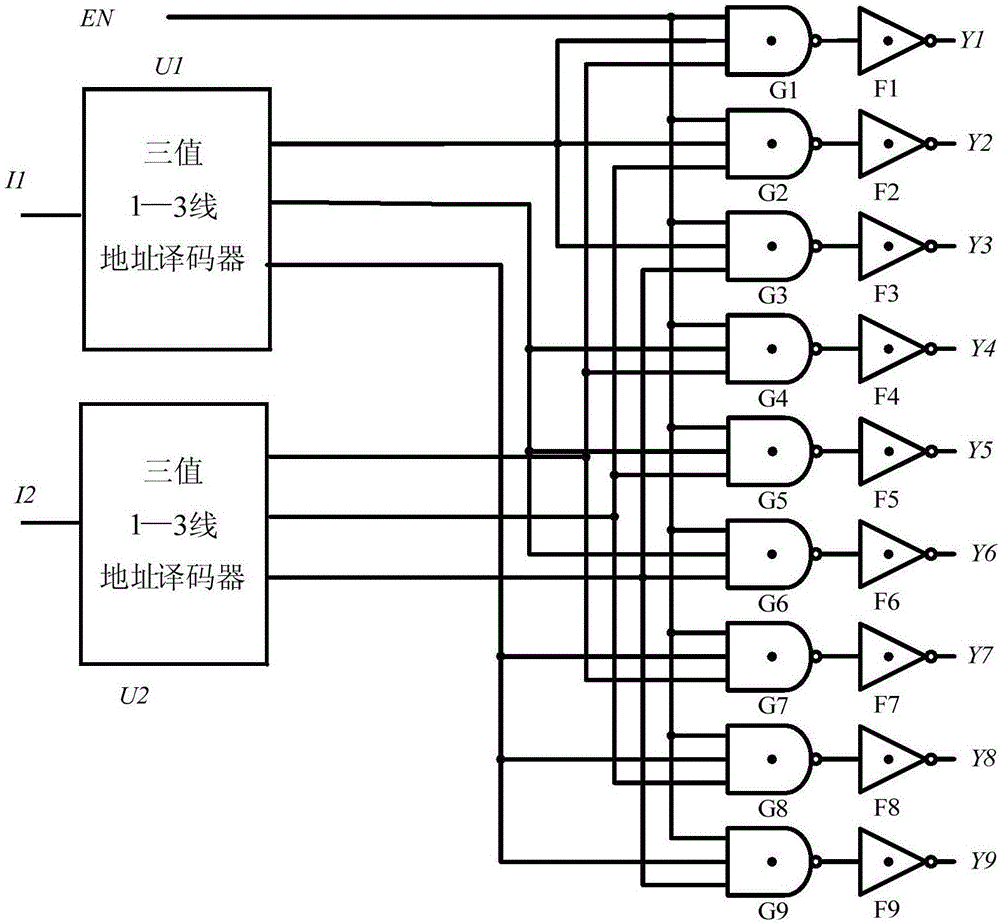

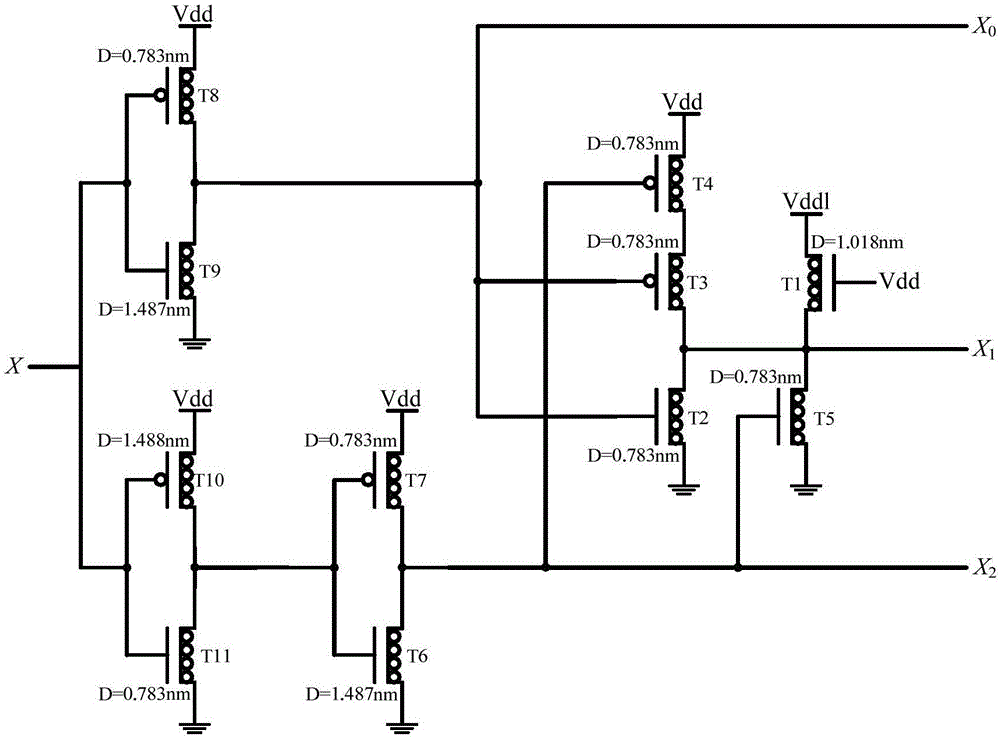

[0025] Embodiment one: if figure 1 , figure 2 and image 3As shown, a three-valued 4-81 line address decoder realized by CNFET includes ten three-valued 2-9 line address decoders, and the three-valued 2-9 line address decoder has an enabling terminal, a first An input terminal, a second input terminal, a first output terminal, a second output terminal, a third output terminal, a fourth output terminal, a fifth output terminal, a sixth output terminal, a seventh output terminal, an eighth output terminal and a Nine output terminals; ten three-value 2-9 line address decoders are respectively the first three-value 2-9 line address decoder A1, the second three-value 2-9 line address decoder A2, and the third three-value 2-9 line address decoder A3, the fourth three-value 2-9 line address decoder A4, the fifth three-value 2-9 line address decoder A5, the sixth three-value 2-9 line address decoder A6, the seventh three-value 2-9 line address decoder A7, the eighth three-value 2-...

Embodiment 2

[0026] Embodiment two: if figure 1 , figure 2 and image 3As shown, a three-valued 4-81 line address decoder realized by CNFET includes ten three-valued 2-9 line address decoders, and the three-valued 2-9 line address decoder has an enabling terminal, a first An input terminal, a second input terminal, a first output terminal, a second output terminal, a third output terminal, a fourth output terminal, a fifth output terminal, a sixth output terminal, a seventh output terminal, an eighth output terminal and a Nine output terminals; ten three-value 2-9 line address decoders are respectively the first three-value 2-9 line address decoder A1, the second three-value 2-9 line address decoder A2, and the third three-value 2-9 line address decoder A3, the fourth three-value 2-9 line address decoder A4, the fifth three-value 2-9 line address decoder A5, the sixth three-value 2-9 line address decoder A6, the seventh three-value 2-9 line address decoder A7, the eighth three-value 2-...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Diameter | aaaaa | aaaaa |

| Diameter | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More