Configuration code stream-based FPGA fault injection complex model

A fault injection and composite model technology, applied in faulty hardware testing methods, faulty computer hardware, instruments, etc. Can not be ignored, to achieve the effect of flexible use, expanding the scope of research, and improving pertinence

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

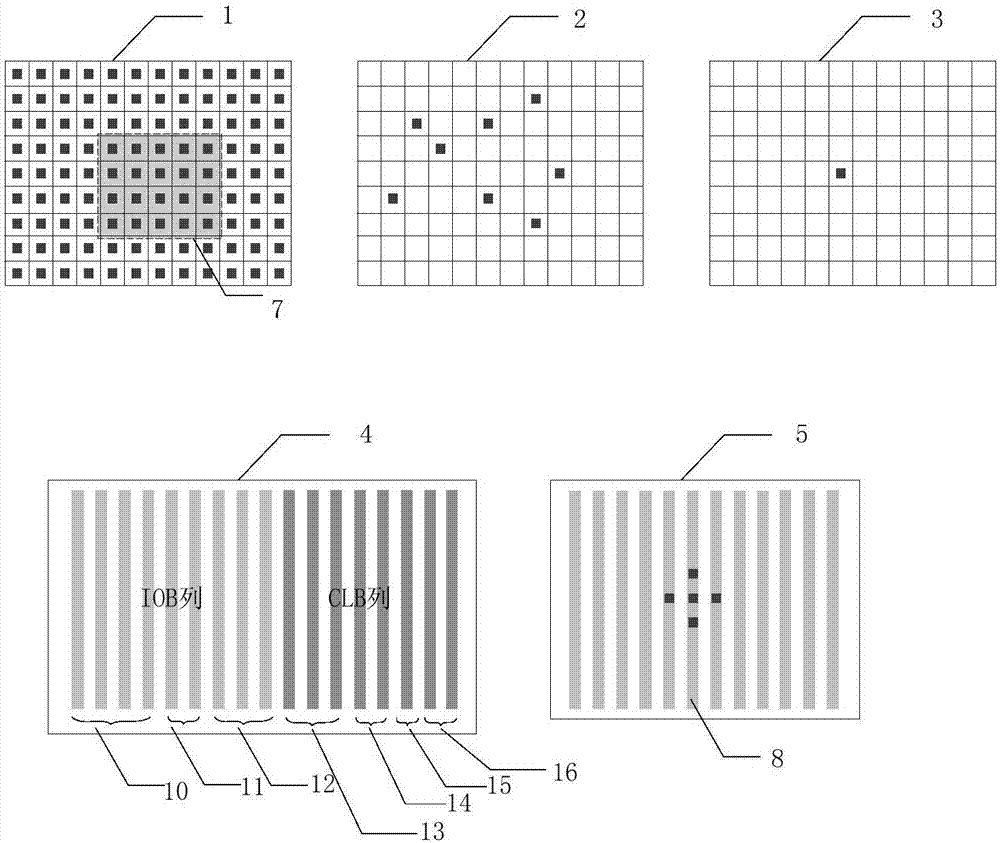

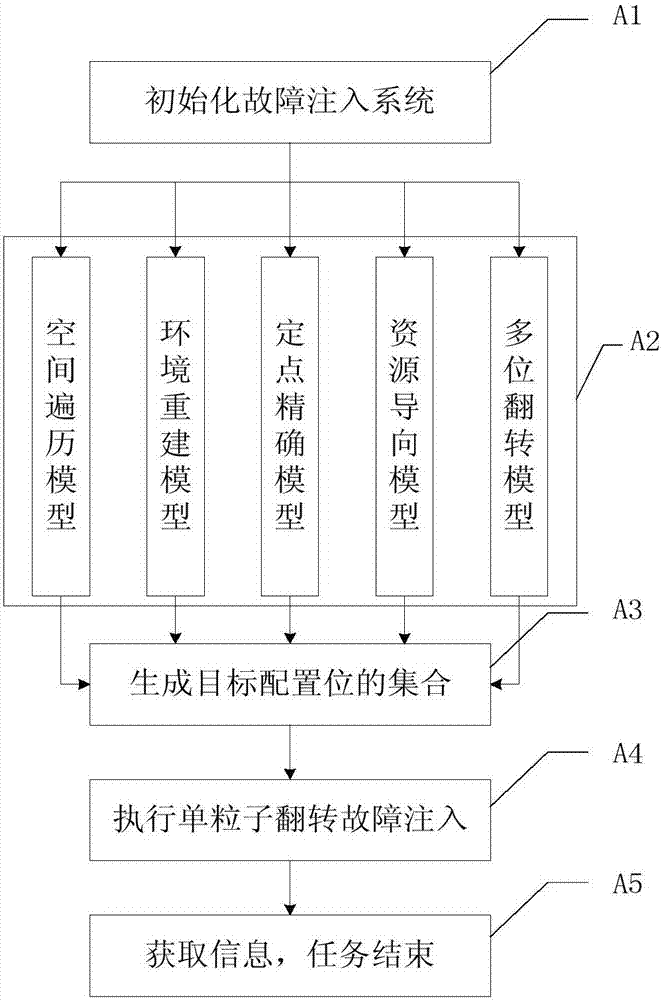

[0035] Such as figure 1 As shown, a composite model of FPGA fault injection based on configuration code stream proposed by the present invention includes space traversal model 1, environment reconstruction model 2, fixed-point precision model 3, resource-oriented model 4 and multi-bit inversion model 5. The functions of each model are as follows:

[0036] (1) Space traversal model: According to user requirements and circuit scale, the entire configuration storage space 1 or part of the configuration storage space 7 (space selected by the user) can be selected as the target of single event flip fault injection. Once the size of the space is determined, the space can be The accessed configuration bits are flipped bit by bit; the frame address and bit offset of the configuration bits in all spaces generally start from 0, the initial frame address is 00000000 (hexadecimal), the initial bit offset is 0, and the traversal range is the same as the device model Related; the starting ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More