Method and system for predicting junction temperature of power device

A technology for predicting power and devices under test, applied in instruments, special data processing applications, electrical digital data processing, etc. Effect of predicting junction temperature, ease of implementation and rollout

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

[0061] like image 3 As shown, a method to predict the junction temperature of a power device includes:

[0062] Step 11: Obtain the integral structure function curve of the device under test;

[0063] Step 12: Determine the first chip layer of the device under test according to the packaging form of the device under test, the packaging material, and the starting point of the integral structure function curve;

[0064] Step 13: layering the first chip layer according to the slope of the curve segment corresponding to the first chip layer in the integral structure function curve, to obtain each thermal equivalent layer and the corresponding thermal resistance value;

[0065] Step 14: Establishing a thermal equivalent layering model of the chip layer of the device under test according to each thermal equivalent layer and the corresponding thermal resistance value, so as to predict the junction temperature of the device under test.

[0066] Preferably, before performing step 13...

Embodiment 2

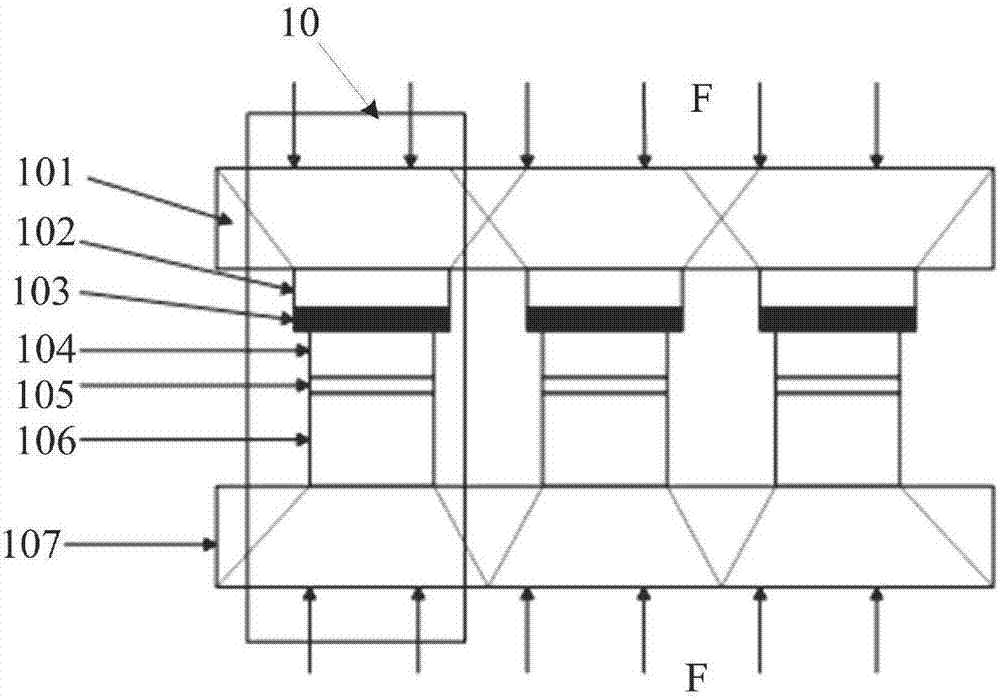

[0078] like Figure 4 As shown, a system for predicting the junction temperature of a power device includes:

[0079] Integral curve acquisition module 21, used to acquire the integral structure function curve of the device under test;

[0080] The first chip layer determination module 22 is connected to the integral curve acquisition module, and is used to determine the first chip of the device under test according to the packaging form of the device under test, the packaging material, and the starting point of the integral structure function curve layer;

[0081] The stratification module 23 is connected to the integral curve acquisition module and the first chip layer determination module respectively, and is used to calculate the first chip layer according to the slope of the curve segment corresponding to the first chip layer in the integral structure function curve. A chip layer is layered to obtain each thermal equivalent layer and the corresponding thermal resistance...

Embodiment 3

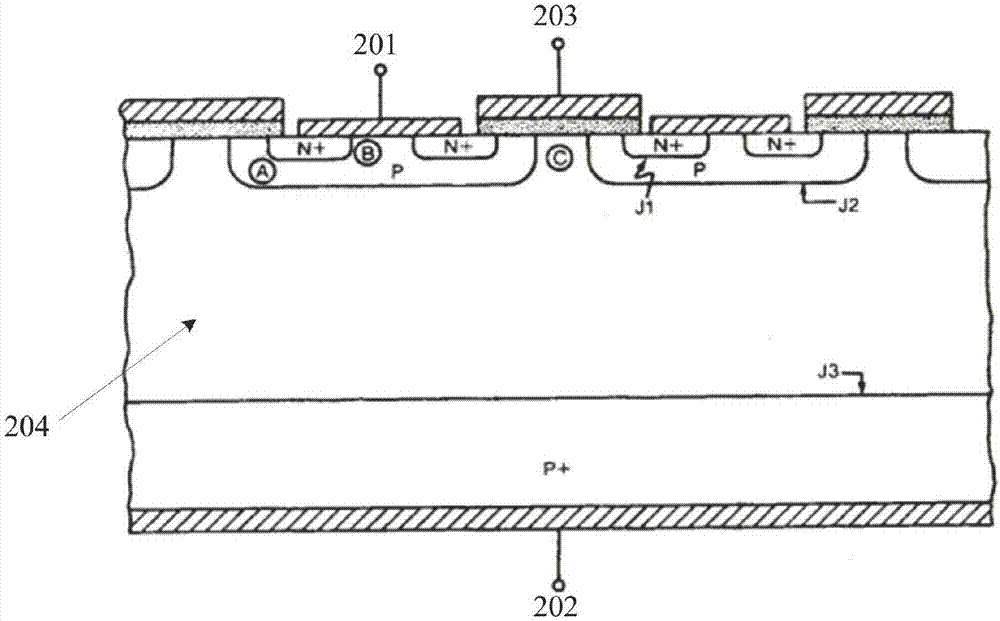

[0095] The application condition of the DC circuit breaker is that the crimping type IGBT device needs to turn off a large current within 3ms, and the heat generated in such a short time is difficult to dissipate through the external radiator, and the heat is mainly concentrated inside the chip, so the chip The modeling of the internal equivalent thermal network is very important for the prediction of junction temperature. In view of the limitations of current chip junction temperature prediction and simulation models in power semiconductor devices, combined with the transient junction temperature prediction requirements of DC circuit breaker application conditions, a method for predicting the junction temperature of power devices provided in this embodiment includes:

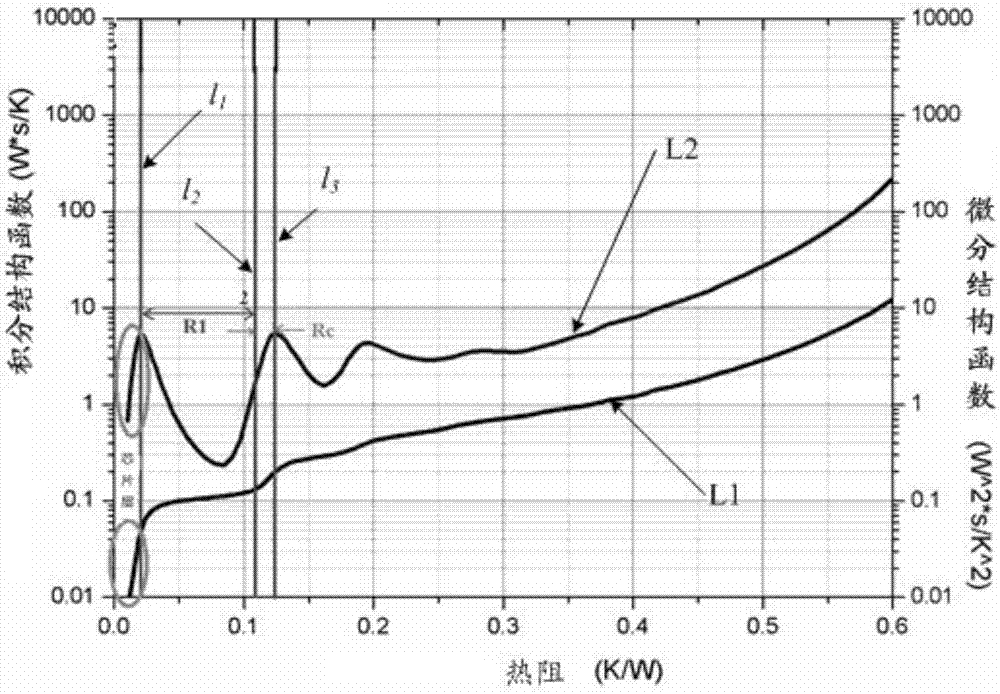

[0096] Step 31: Obtain the integral structure function curve and the differential structure function curve of the device under test;

[0097] Step 311: Measure the electrical parameters of the device under test...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More