Rate switching method of M.2 PCIe testing fixture

A technology of rate switching and test fixtures, which is applied in faulty hardware testing methods, faulty computer hardware detection, error detection/correction, etc. It can solve the problems of unable to switch speeds, unable to test PCIeGen2 and Gen3 signals, etc., to save resources and time, easy to operate and practical, and the effect of improving work efficiency

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0019] The content of the present invention is described in more detail below:

[0020] The rates for each version of the PCIe signal include:

[0021] 1. PCIe 1.0 (i.e. PCIe Gen1), the rate is 2.5Gb / s;

[0022] 2. PCIe 2.0 (that is, PCIeGen2), the rate is 5Gb / s, including Gen2 -3.5dB and -6dB two kinds of emphasis;

[0023] 3. PCIe 3.0 (that is, PCIe Gen3), the rate is 8Gb / s, including P0, P1, ..., P10.

[0024] The goal of this invention is to test PCIe Gen1, Gen2 -3.5dB and -6dB and Gen3 P7.

[0025] The implementation steps of this method are as follows:

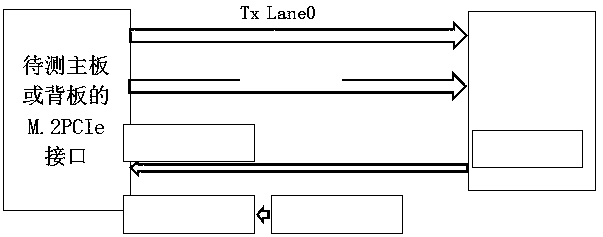

[0026] 1) M of the main board or backplane to be tested. The 2PCIe interface is connected to the test fixture. The signal lines P and N of Tx lane0 of the test fixture are respectively connected to CH3 and CH4 of the oscilloscope through the SMA-SMA cable, and the P and N of the clock signal are respectively connected to CH1 and CH2 of the oscilloscope. The two groups are the signals to be tested. like figure 1 sh...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com