A device, method and instruction mapping method for executing instruction selection

A technology for executing instructions and instructions, which is applied in the field of instruction mapping of computers with data flow architecture, can solve problems such as low computing efficiency, and achieve the effect of improving computing efficiency and improving space-time utilization

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

[0077] When the present invention studies the optimization of the instruction mapping algorithm on the multi-context data flow architecture computer, it is found that the defect of the prior art is caused by the blockage of the context pipeline during the execution of the data flow graph. As long as the blockage of the context is reduced, the The computing unit is effectively used in the subsequent execution, thereby improving the utilization rate of the computing unit and the throughput of the pipeline, and improving the computing efficiency. However, the random execution instruction selection method makes the instruction execution difficult to predict, and it is difficult to analyze and optimize the pipeline throughput.

[0078] If a fixed strategy can be adopted to select and execute instructions when the instruction is issued and selected, the behavior of the pipeline can be predicted, and then the pipeline can be analyzed and optimized.

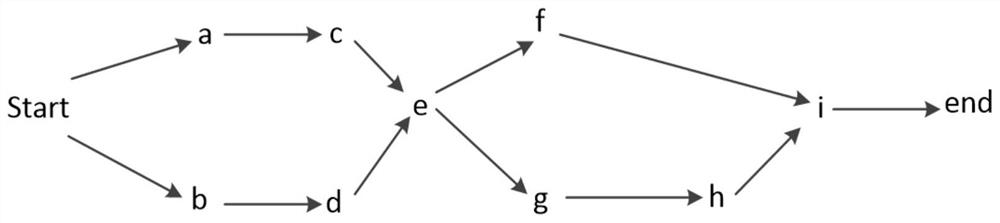

[0079] In order to improve the ut...

Embodiment 2

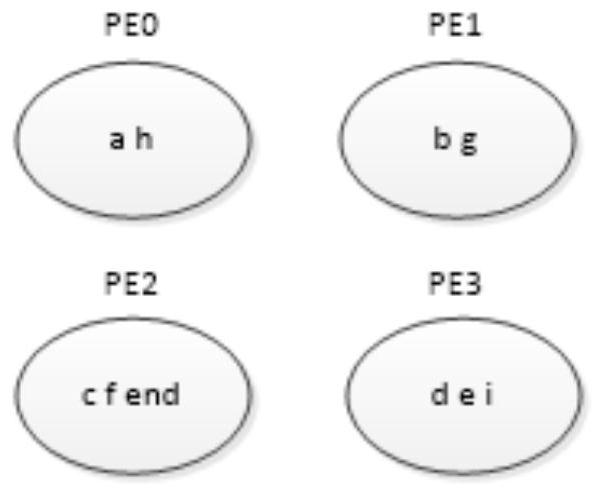

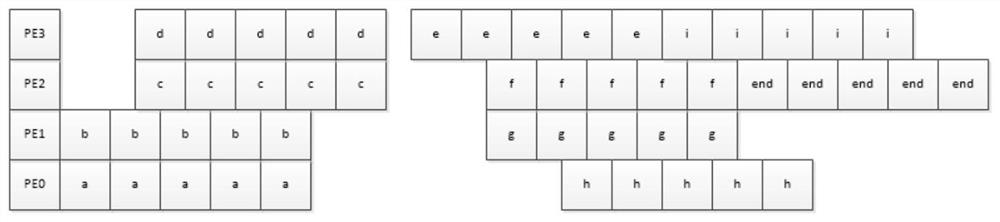

[0149] In another specific embodiment, the present invention also provides a device for executing instruction selection, such as Figure 7 As shown, the device is composed of four instruction control cache components, several four-to-one selectors, and several judging components. Each instruction cache (that is, the instruction control cache component) stores the executable status of several instructions. The executable information of the same instruction in the four instruction caches is connected to the same 4-to-1 selector, and the 4-to-1 selector selects an executable instruction therefrom. Every four 4-to-1 selectors are sequentially connected to the four ports of a judging unit according to the order of the instructions, and the judging unit judges to select an executable command from the four 4-to-1 logics currently connected and execute it. It is sent to the output component, and the output signal terminates the operation of the subsequent components. If the instructi...

Embodiment 3

[0153] In another embodiment, the present invention also provides an instruction mapping method based on the earliest executable time, the flow chart of the method is as follows Figure 12 , the steps are as follows:

[0154] (1) Initialize the final execution time of all computing units to 0, and initialize the executable time of all macro instructions to 0;

[0155] (2) Sort all instructions according to the depth, and the instruction depth refers to the longest path length from the current instruction to the root node (start node);

[0156] (3) In order of depth, the instructions are mapped sequentially. For each instruction, traverse all computing units;

[0157] (4) For each computing unit, calculate the executable time of the current instruction mapped on the computing unit. In a specific implementation, the calculation method is: calculate the sum of the completion time of the first instruction of all predecessor macro-instructions of the current instruction and the ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More