Testing method and device of memory

A test method and memory technology, applied in static memory, instruments, etc., can solve the problems of single test process, cumbersome operation process, incomplete test, etc., and achieve the effect of improving accuracy and efficiency and ensuring comprehensiveness

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

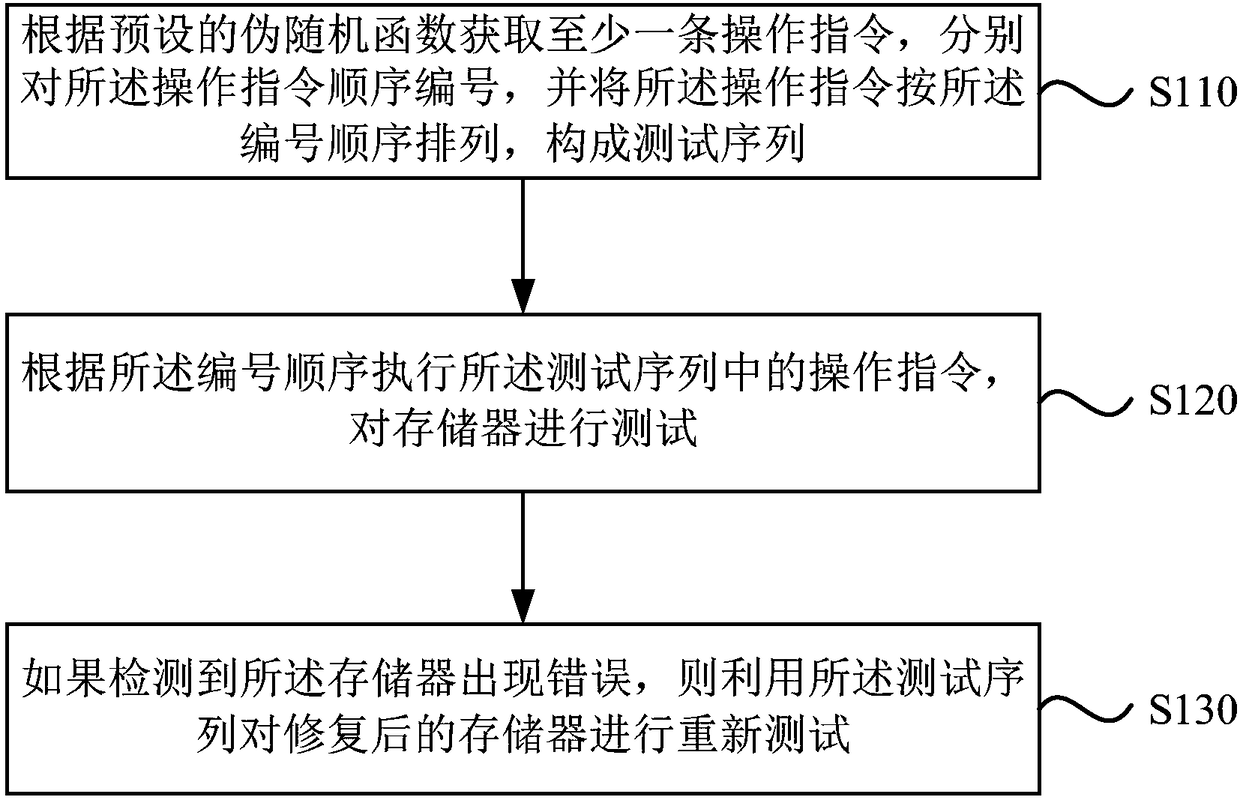

[0053] figure 1 It is a flow chart of a memory testing method provided by Embodiment 1 of the present invention. The method is applicable to the case of performing a function test on the memory, and the method can be executed by a memory testing device, and the device can be realized by software and / or hardware. The method specifically includes:

[0054] S110. Obtain at least one operation instruction according to a preset pseudo-random function, respectively number the operation instructions in sequence, and arrange the operation instructions in the order of the numbers to form a test sequence.

[0055]Specifically, a pseudo-random function is a type of function. A function describes the correspondence between each input value and a unique output value. The pseudo-random function is used to generate a pseudo-random number. The random function is a function that generates numbers, and it is an important random function in Excel worksheets and C language. The most important ...

Embodiment 2

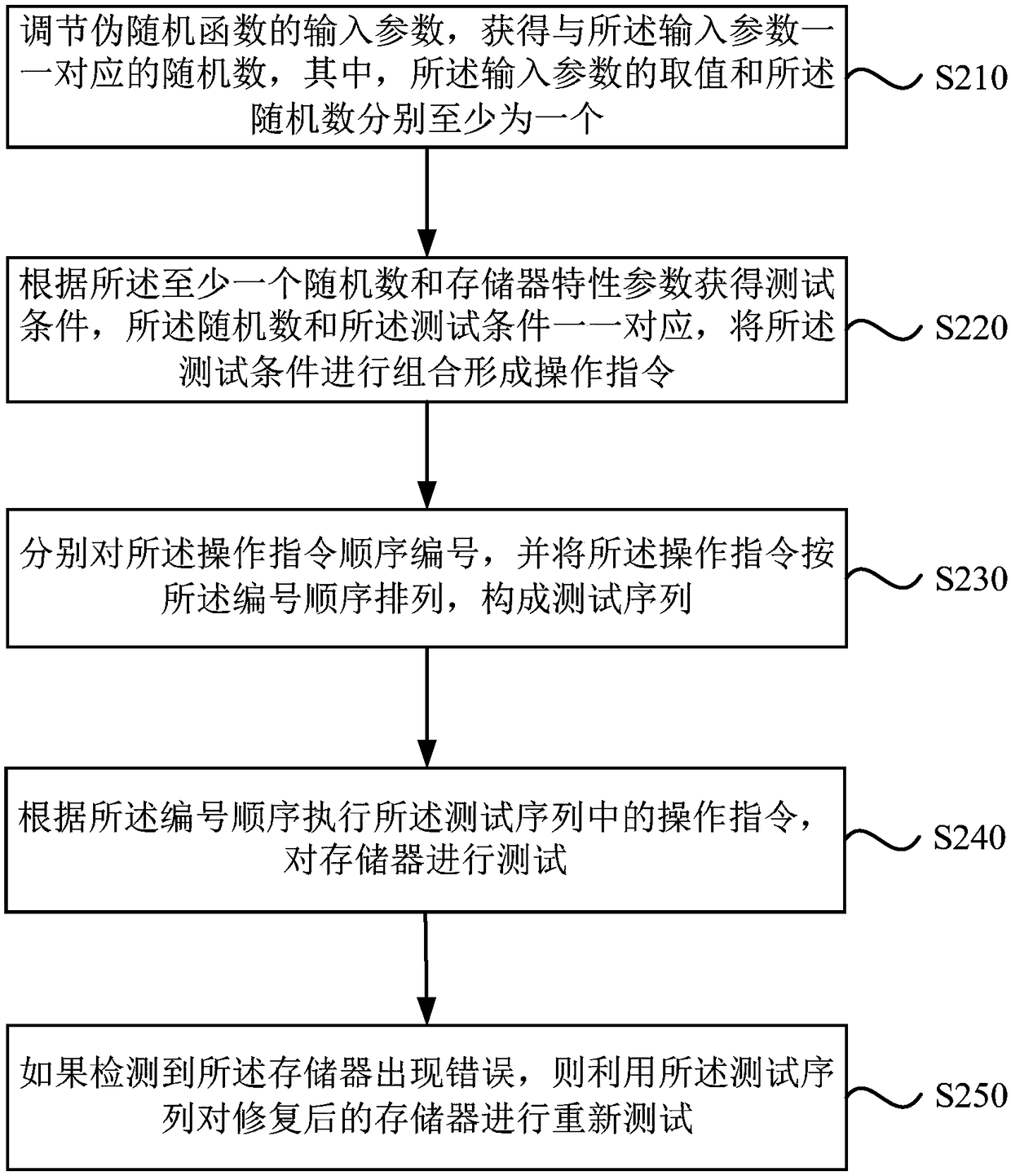

[0064] figure 2 It is a flow chart of a memory testing method provided by Embodiment 2 of the present invention. This embodiment is optimized on the basis of the above embodiments, and optimizes "obtaining at least one operation instruction according to a preset pseudo-random function" , including the following steps:

[0065] S210. Adjust an input parameter of the pseudo-random function to obtain a random number corresponding to the input parameter one by one, wherein the value of the input parameter and the random number are at least one.

[0066] Specifically, there may be two input parameters of the pseudo-random function, denoted as A and B, and A and B may each have at least one value, and the generated pseudo-random number is Y. Among them, A is used to provide seeds, and B is used to generate random numbers. Different seeds will generate different random numbers. The same seed and different input parameters B will generate different random numbers. A and B can take ...

Embodiment 3

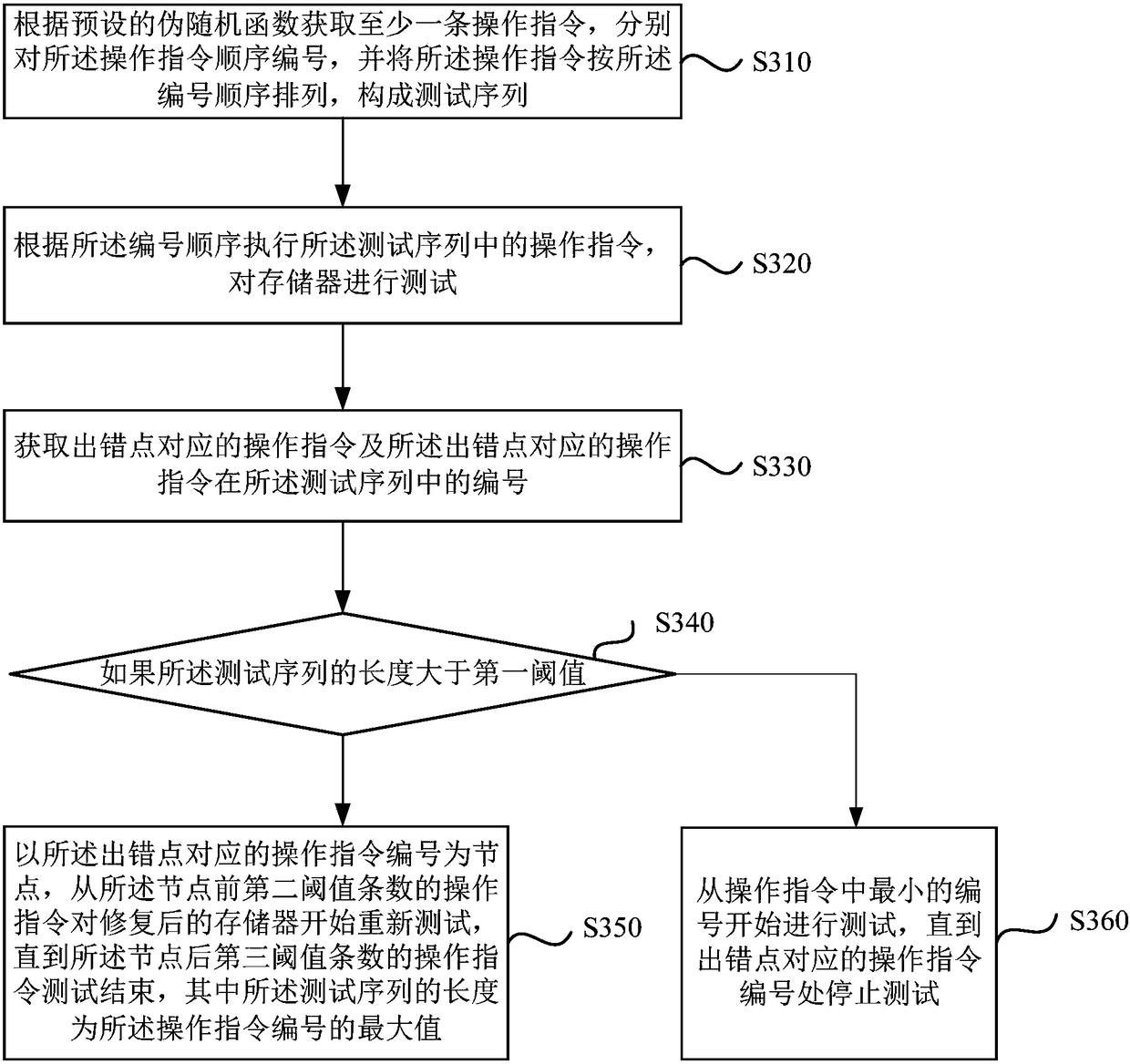

[0088] image 3 It is a flowchart of a fault detection method for a downhole control system provided by Embodiment 3 of the present invention. This embodiment is optimized on the basis of the above embodiments. For "if an error is detected in the memory, use the The test sequence "retest the repaired memory" has been optimized, which includes the following steps:

[0089] S310. Obtain at least one operation instruction according to a preset pseudo-random function, respectively number the operation instructions in sequence, and arrange the operation instructions in the sequence of numbers to form a test sequence.

[0090] S320. Execute the operation instructions in the test sequence according to the numbering order to test the memory.

[0091] S330. Obtain the operation instruction corresponding to the error point and the serial number of the operation instruction corresponding to the error point in the test sequence.

[0092] S340. If the length of the test sequence is great...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More