Verification platform of system-on-chip and verification method thereof

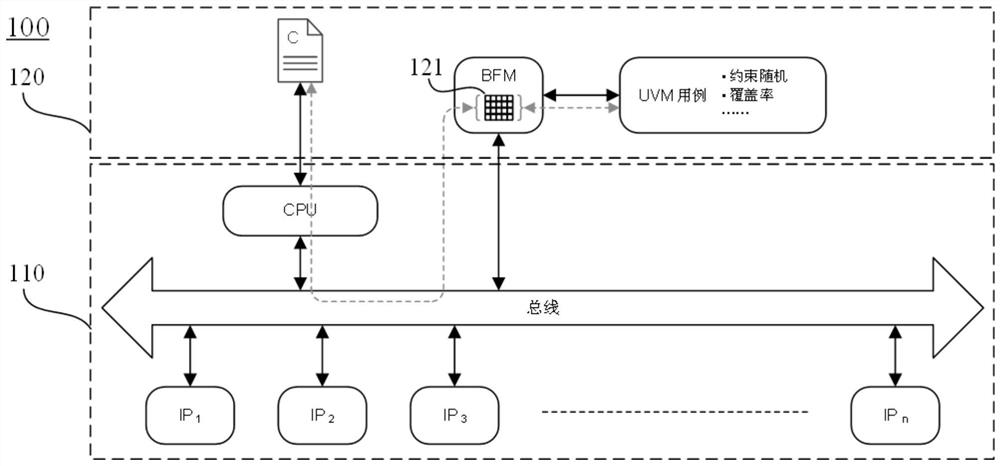

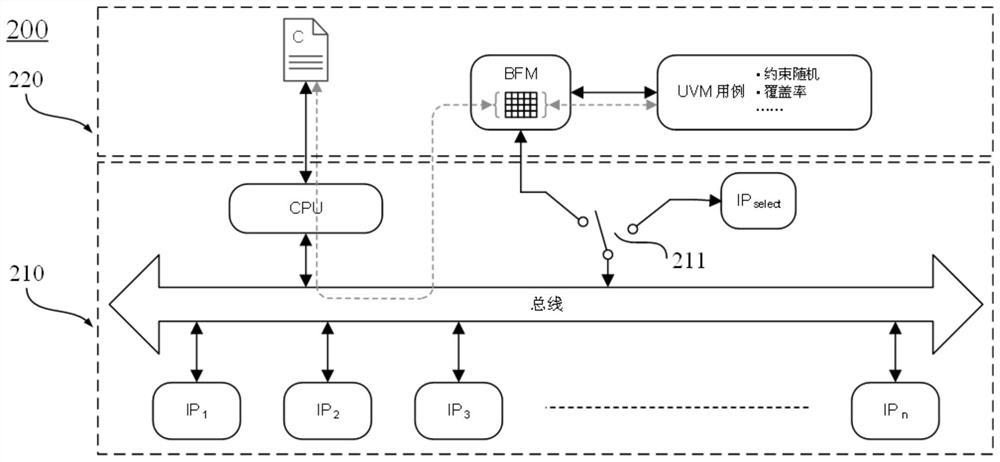

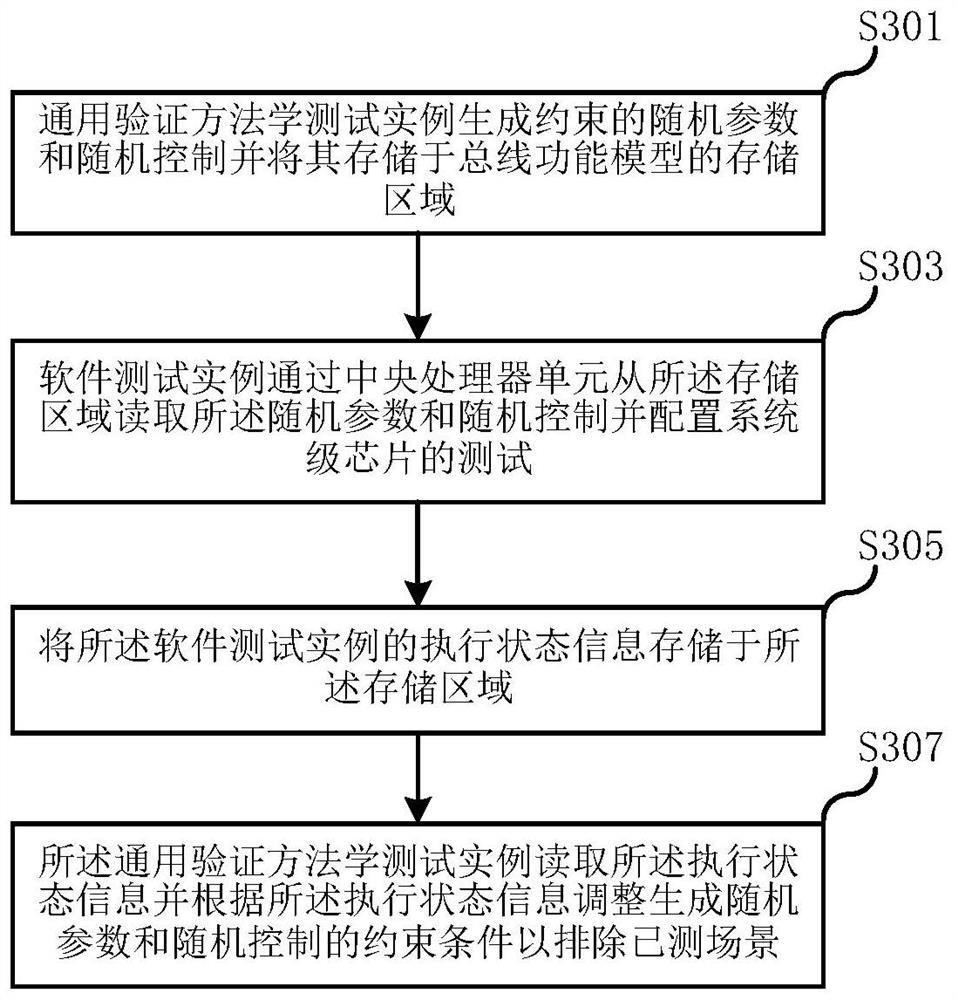

A system-level chip and verification platform technology, which is applied to the verification platform of the system-level chip and its verification field, can solve the problems of affecting the test coverage rate, affecting the simulation progress, and the difficulty of direct testing, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0022] Various aspects and examples of the application will now be described. The following description provides specific details for a thorough understanding and enabling description of these examples. However, it will be understood by those skilled in the art that this application may be practiced without many of these details.

[0023] Also, some well-known structures or functions may not be shown or described in detail for the sake of brevity and to avoid unnecessarily obscuring the related description.

[0024] Explanation of some concepts:

[0025] IP core module: IP (Intellectual Property) core module is a pre-designed or even verified component with certain functions, which can be integrated and selected by chip designers. Generally, there are multiple IP core modules integrated in SoC.

[0026] Coverage: Coverage is a measure of test integrity and a measure of test effectiveness. Coverage is equal to the number of items executed at least once / total number of items....

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More