Improved cache pseudo-least recently used data replacement method

A cache, the least recent technology, applied in the direction of memory address/allocation/relocation, etc., can solve problems such as high overhead

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

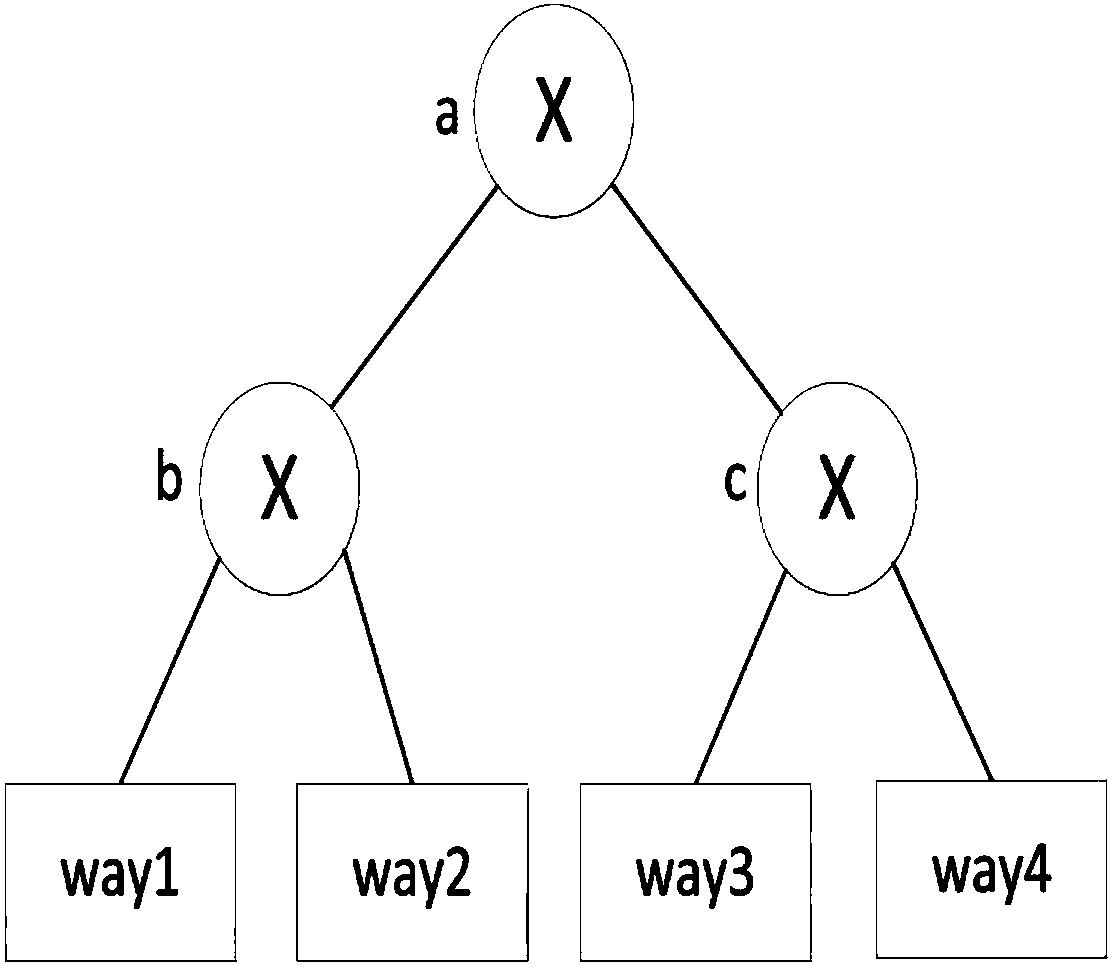

[0014] In a tree control structure, each leaf node (identifying a certain way of the cache) contains 1 to 2 flag bits, that is, each way has one or two flag bits. If there is only one bit, the value of the flag bit is 0 or 1, and if there are two bits, the values of the two flag bits are 0 and 1, respectively. This is because the flag bits of different error-introducing nodes are not necessarily the same.

[0015] The flag bits are named as follows: take the analyzed error-introduced node as the root node, all paths in its left subtree have flag bits 0 for it, and all paths in its right subtree have In other words, the flag bits are all 1. In this way, except that way 1 and way N only contain one flag bit of 0 and 1 respectively, the other ways all contain two flag bits of 0 and 1, which are respectively aimed at different error introduction nodes. The flag bits of the same path for the same error-introducing node may also be the same as the flag bits of this path for othe...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More