A Segmented Programmable Clock Network Architecture Based on Clock Regions

A network structure and segmented technology, applied in the field of clock region support segmented programmable clock network structure, clock network structure, can solve problems such as limiting clock operating frequency, clock skew accumulation, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0019] Embodiments of the invention are described in detail below, examples of which are illustrated in the accompanying drawings. The embodiments described below by referring to the figures are exemplary only for explaining the present invention and should not be construed as limiting the present invention.

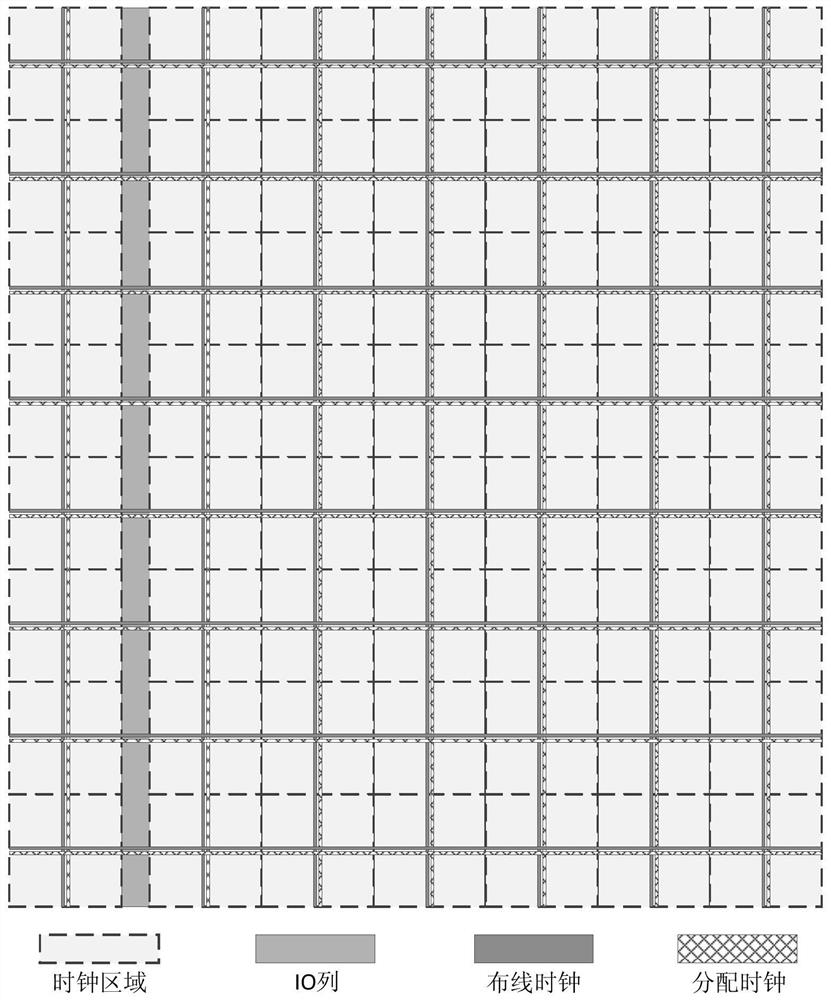

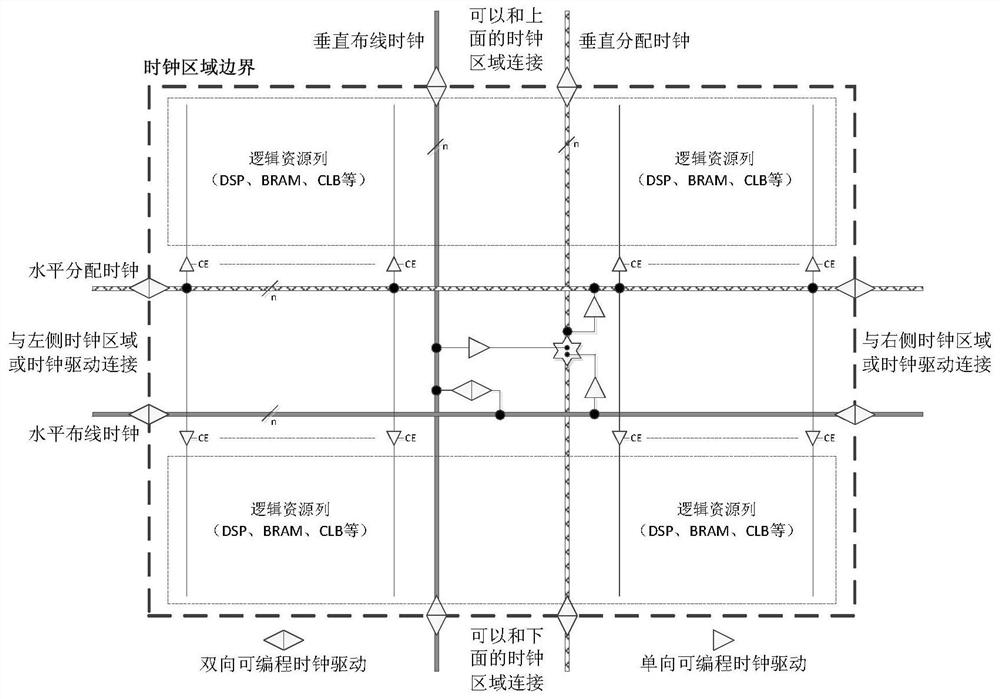

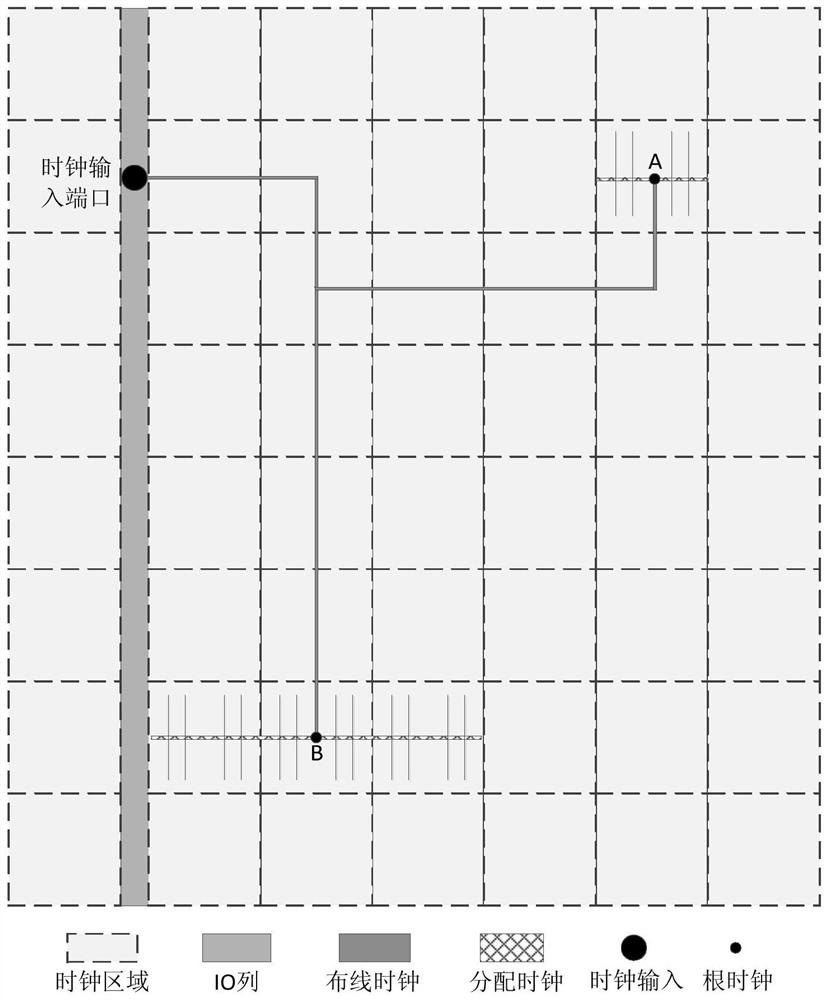

[0020] Such as figure 1 As shown, a segmented programmable clock network structure based on clock regions is suitable for large-scale FPGAs and can provide low-skew high-performance clock signals to meet the needs of large-scale FPGA chips for high-performance clocks . The clock network structure proposes the concept of clock regions. The FPGA structure using this clock network is composed of clock regions. The two-dimensional splicing of the clock regions in the plane forms rows and columns, and the entire FPGA structure is composed of IO columns and configuration columns. Each clock region contains logic resources common in FPGAs such as DSP, BRAM, and CLB. These log...

PUM

Login to view more

Login to view more Abstract

Description

Claims

Application Information

Login to view more

Login to view more - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap