Homologous timing adaptation method, device and chip

An adaptive and timing technology, applied in the electronic field, can solve the problems of occupying PCB area, wasting PCB space, increasing costs, etc., and achieve the effects of saving occupied area, simplifying wiring complexity, and reducing costs

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

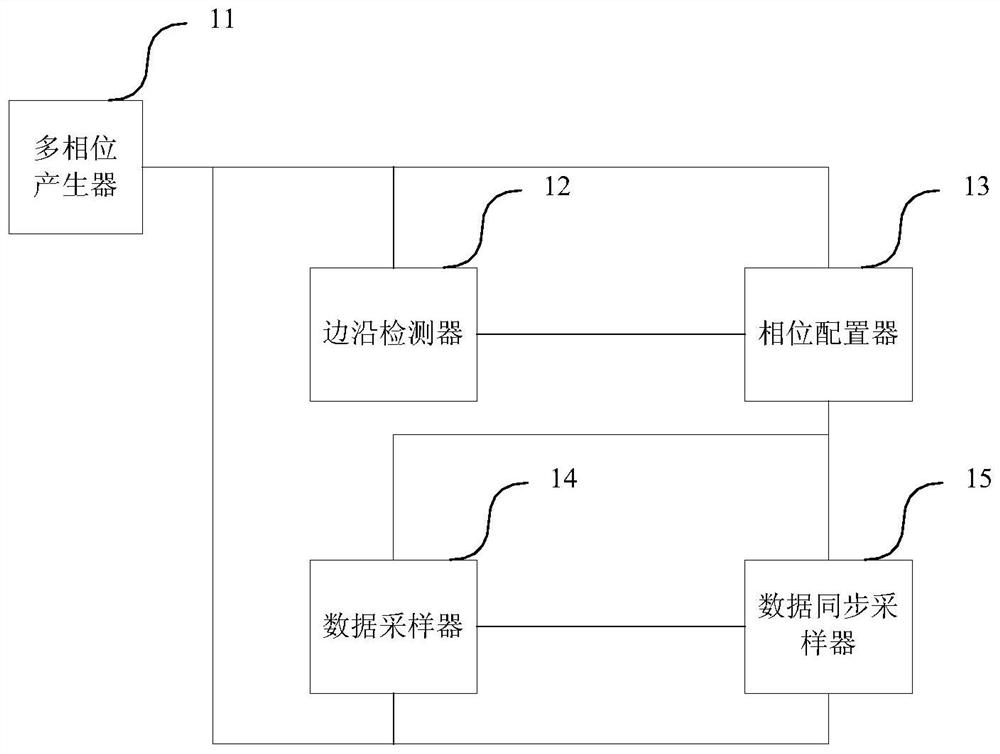

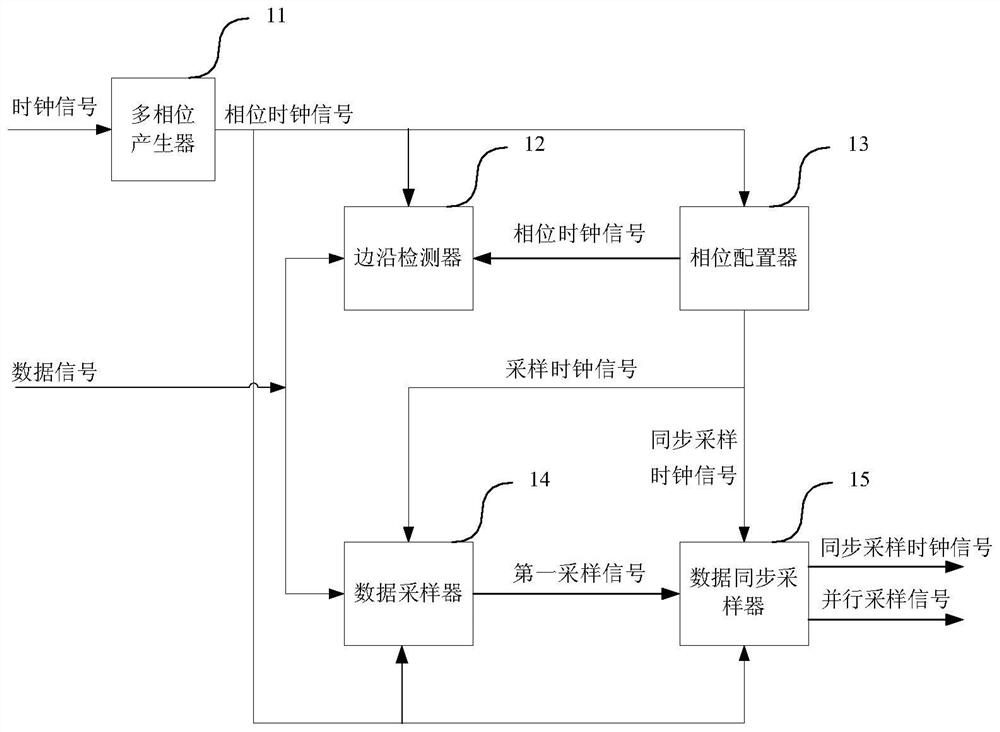

[0038] figure 2 It is a schematic structural diagram of the homologous timing adaptive device provided in the embodiment of the present application, image 3 It is a signal flow diagram of the homologous timing adaptive device provided in the embodiment of the present application. The homologous timing adaptive device provided in the embodiment of the present application can be applied to a chip, and the chip can be used as a receiving end chip in an inter-chip communication scenario. Such as figure 2 and image 3 As shown, the homologous timing adaptive device provided in the embodiment of the present application may include: a multi-phase generator 11 , an edge detector 12 , a phase configurator 13 and a data sampler 14 .

[0039] The multiphase generator 11 is electrically connected to the edge detector 12 , the phase configurator 13 and the data sampler 14 respectively, and the phase configurator 13 is electrically connected to the edge detector 12 and the data sample...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More