OPC verification method for gate region

A verification method and area technology, applied in the photoengraving process of the pattern surface, the original for opto-mechanical processing, optics, etc., can solve the problems of OPC verification efficiency, no inspection-free area in the gate area, and false alarms.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0029] The specific implementation manner of the present invention will be described in more detail below with reference to schematic diagrams. The advantages and features of the present invention will be more apparent from the following description. It should be noted that all the drawings are in a very simplified form and use imprecise scales, and are only used to facilitate and clearly assist the purpose of illustrating the embodiments of the present invention.

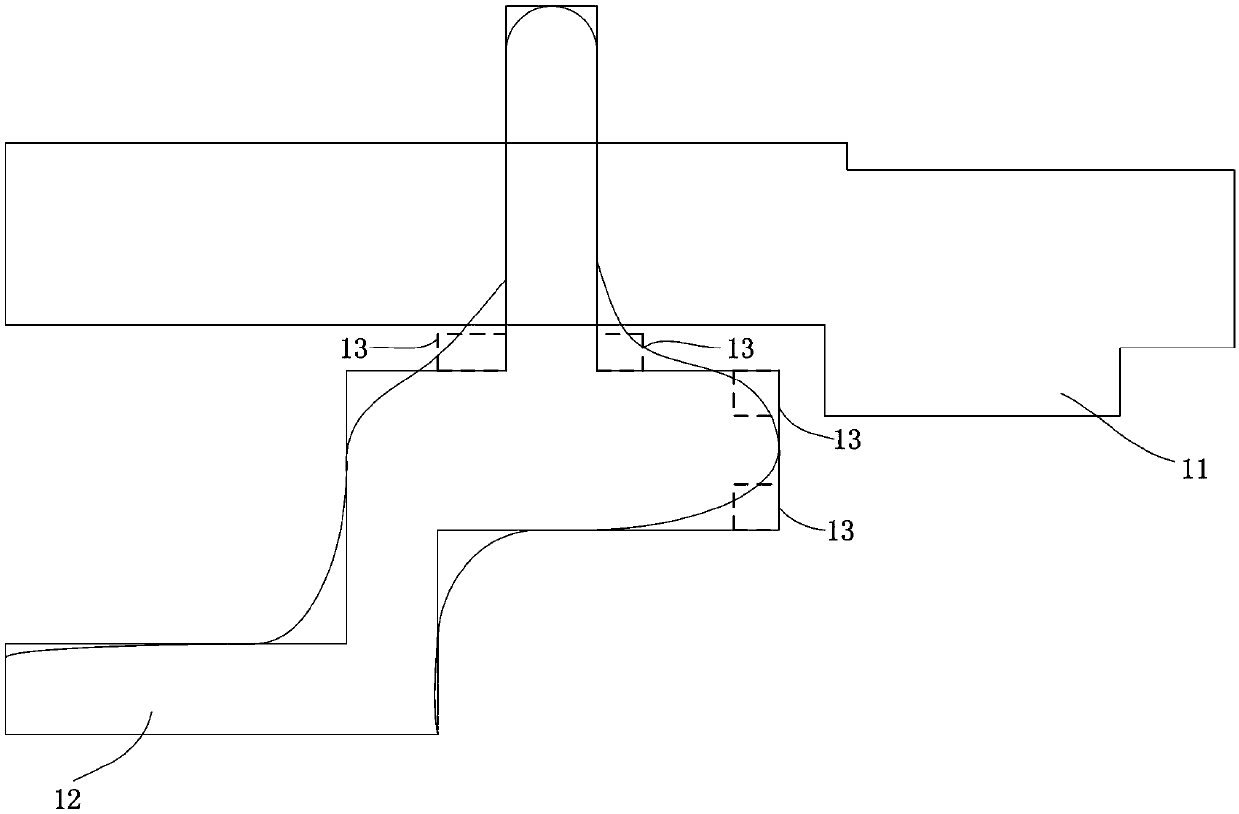

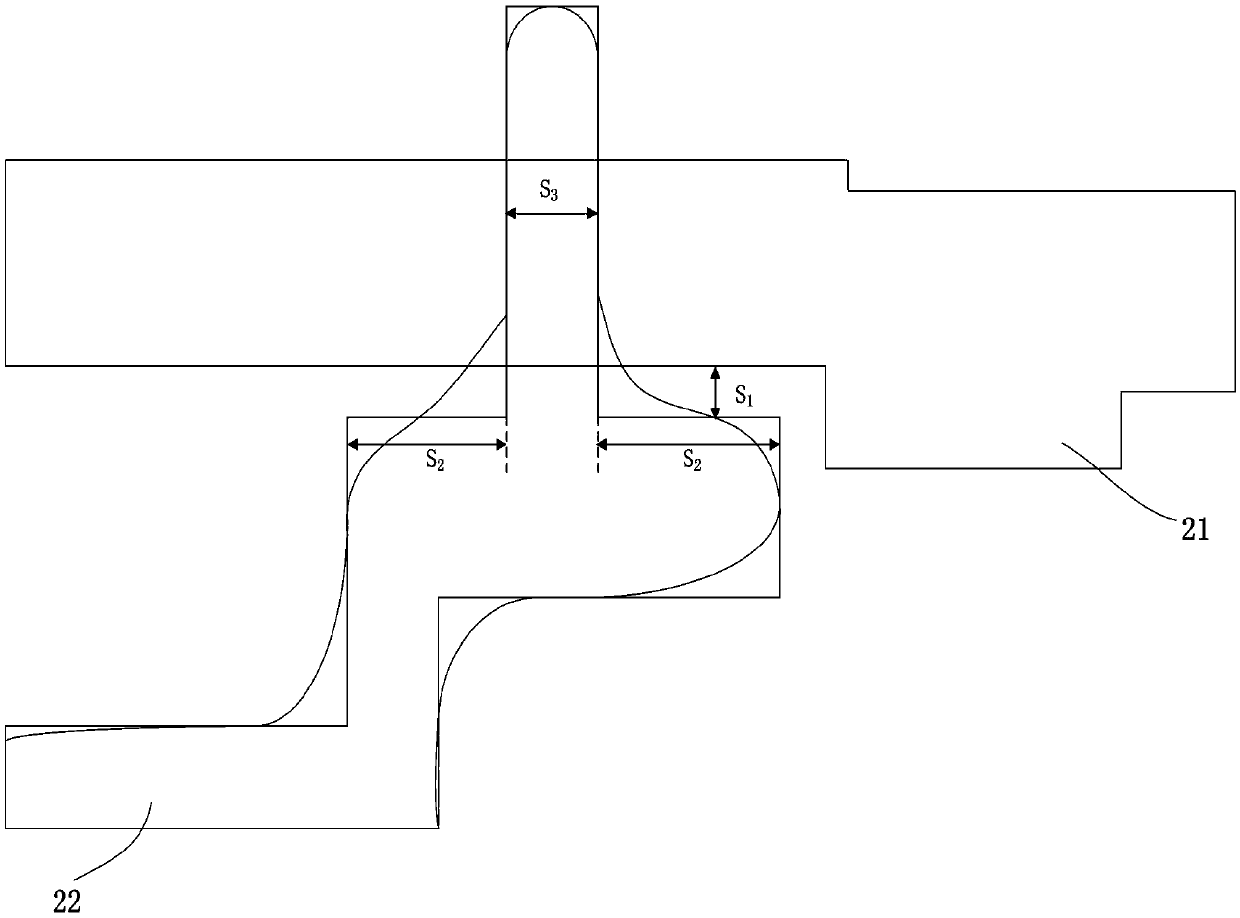

[0030] As mentioned in the background technology, when the optical proximity correction (OPC) method is used to correct the pattern on the mask, due to the existence of rounded corners in the pattern, the existing OPC verification inspection will set an exemption for this phenomenon. region to reduce false positives. Such as figure 1 As shown, in the OPC model, an inspection-free region 13 is provided on the polysilicon layer 12 above the active region layer 11 . However, when inspecting the gate area in the pol...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More