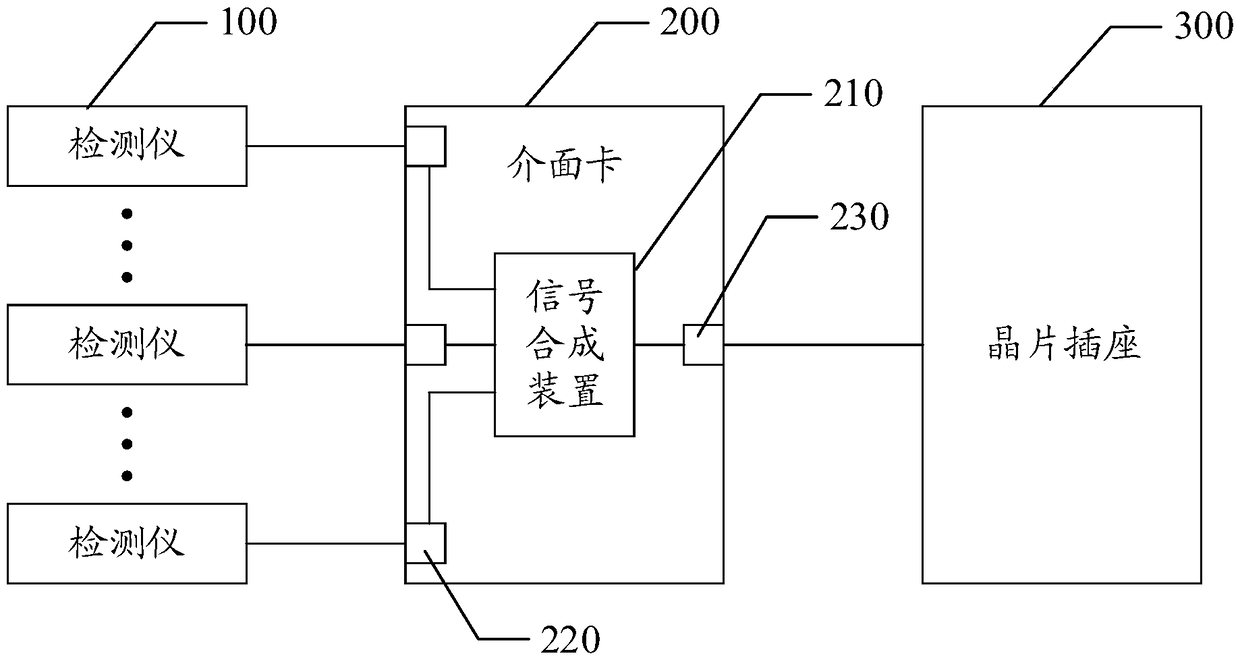

Wafer test device and method

A chip testing, chip technology, applied in the direction of measuring devices, electronic circuit testing, measuring electricity, etc., can solve the problems of low tester frequency and inability to test high-frequency chips, and achieve the effect of saving testing costs

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

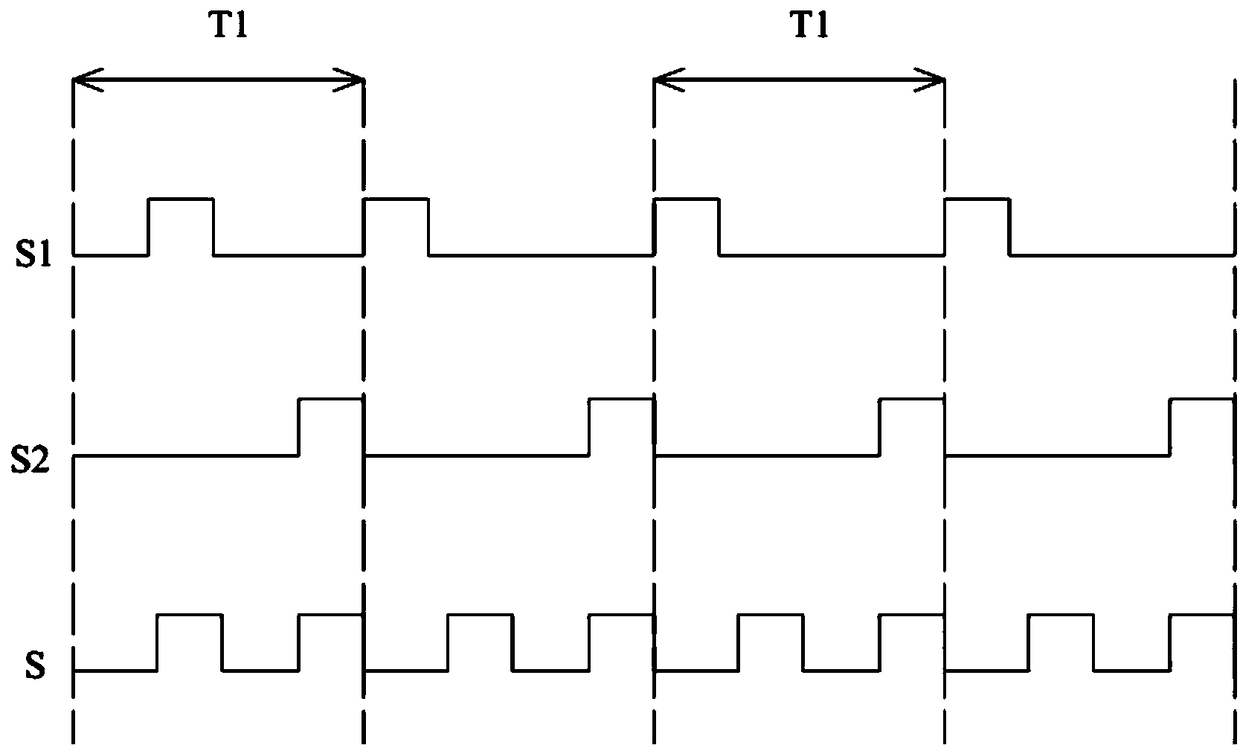

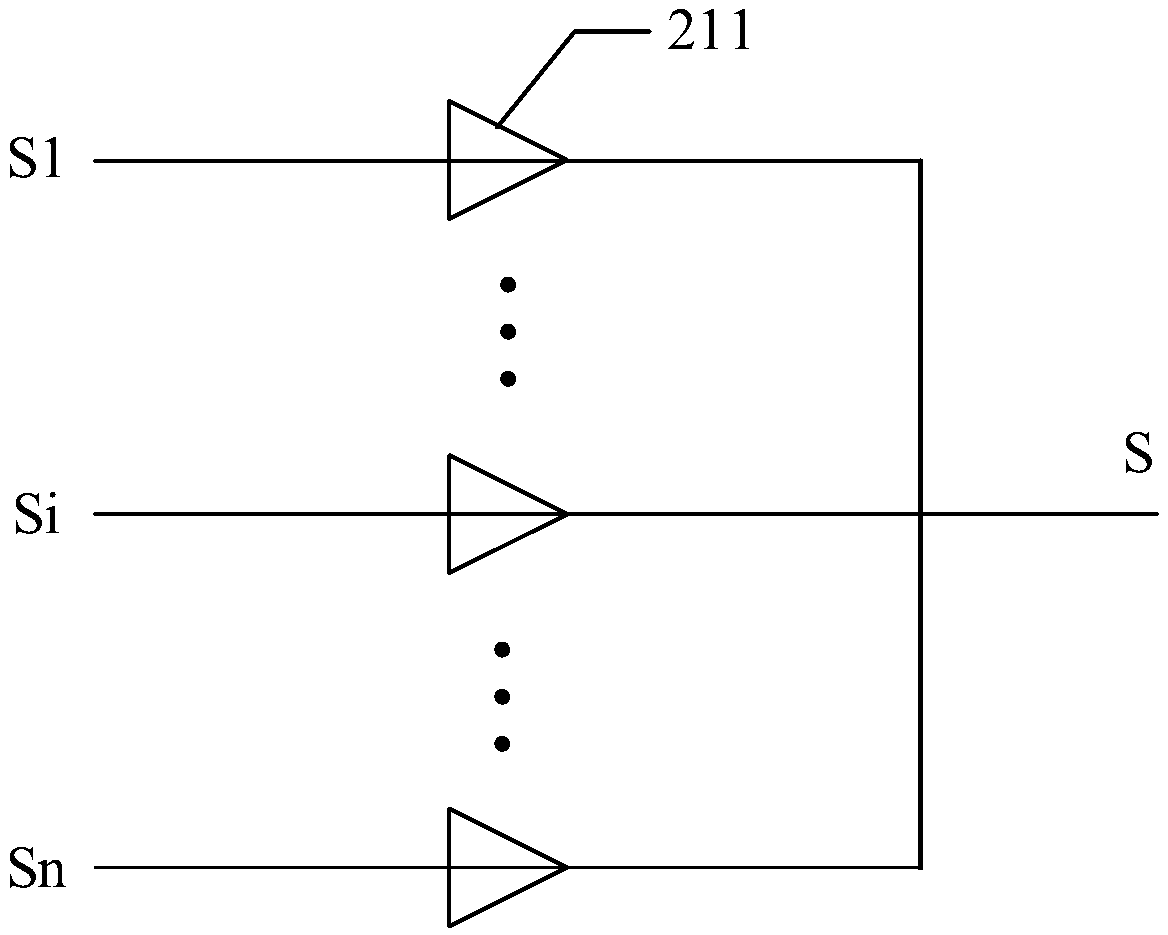

Method used

Image

Examples

Embodiment Construction

[0045] Example embodiments will now be described more fully with reference to the accompanying drawings. Example embodiments may, however, be embodied in many forms and should not be construed as limited to the embodiments set forth herein; rather, these embodiments are provided so that this disclosure will be thorough and complete, and will fully convey the concept of example embodiments to those skilled in the art. The same reference numerals in the drawings denote the same or similar structures, and thus their detailed descriptions will be omitted.

[0046] Although relative terms such as "upper" and "lower" are used in this specification to describe the relative relationship of one component of an icon to another component, these terms are used in this specification only for convenience, for example, according to the description in the accompanying drawings directions for the example described above. It will be appreciated that if the illustrated device is turned over so...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com