A PCIE bus speed measurement system and method based on Shenwei platform

A bus and platform technology, applied in the field of PCIE bus speed measurement system based on Shenwei platform, to achieve the effect of outstanding substantive characteristics, convenient use and easy implementation

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

specific Embodiment approach 1

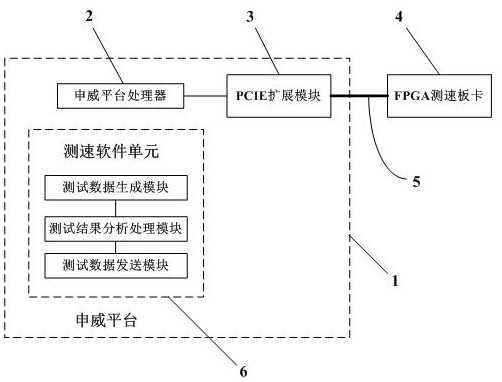

[0046] see figure 1 . figure 1 It is a specific implementation of the PCIE bus speed measurement system based on the Shenwei platform in the present invention. In this embodiment, the PCIE bus speed measurement system based on the Shenwei platform includes the PCIE bus 5 to be tested, the Shenwei platform 1 and the test data for receiving the Shenwei platform 1 and for recording and feeding back the current test. The FPGA speed measuring plate card 4 of the used time length t of data transmission; Described test data has specific size; The PCIE bus line of Shen Wei platform processor 2 is connected with PCIE expansion module 3, and PCIE expansion module 3 passes through to-be-tested PCIE bus line 5 and The FPGA speed measuring board 4 is connected; the Shenwei platform 1 is equipped with a speed measuring software unit 6 for cooperating with the FPGA speed measuring board 4 for detecting the transmission rate of the above-mentioned PCIE bus 5 to be tested.

[0047] In this emb...

specific Embodiment approach 2

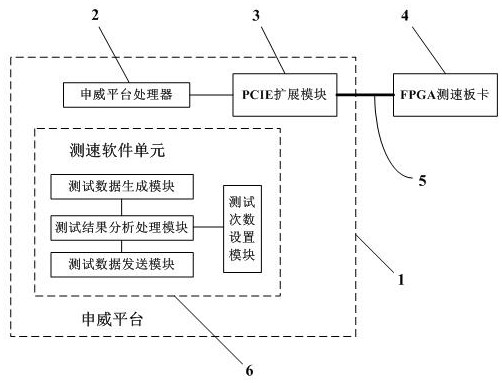

[0073] see image 3 . image 3 It is another specific implementation of the PCIE bus speed measurement system based on the Shenwei platform of the present invention. Compared with the above-mentioned specific embodiment 1, this embodiment 2 is different in that the PCIE bus speed measurement system based on the Shenwei platform, its speed measurement software unit 6 also includes a test number of times setting module, which is the same as the described number of tests setting module The test result analysis and processing modules are connected to each other, and are used to set the detection times of the above-mentioned PCIE bus 5 transmission rate test to be tested. In addition, in this embodiment 2, this PCIE bus speed measurement system based on the Shenwei platform, the test result analysis processing module of its speed measurement software unit 6, is also used for when the number of detections input by the test times setting module is greater than 1, call The test data...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More