A parallel automated verification method for a processor instruction set

An automatic verification and processor instruction technology, applied in the direction of concurrent instruction execution, machine execution device, etc., can solve the problems of few operable methods and no instruction verification method, and achieve high reusability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0034] Below in conjunction with accompanying drawing, the present invention is described in further detail:

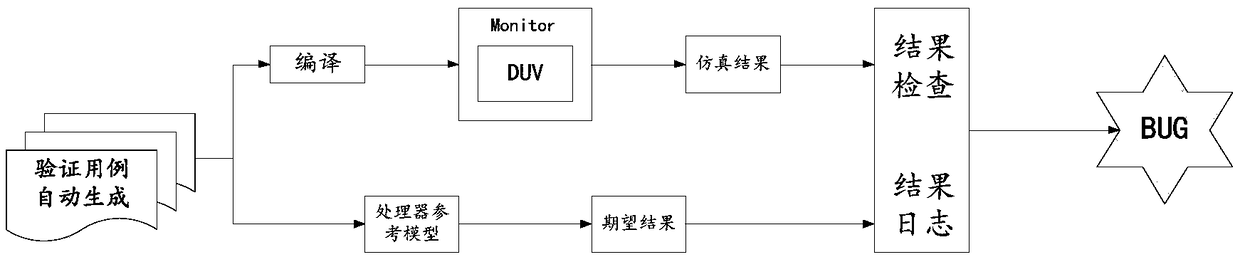

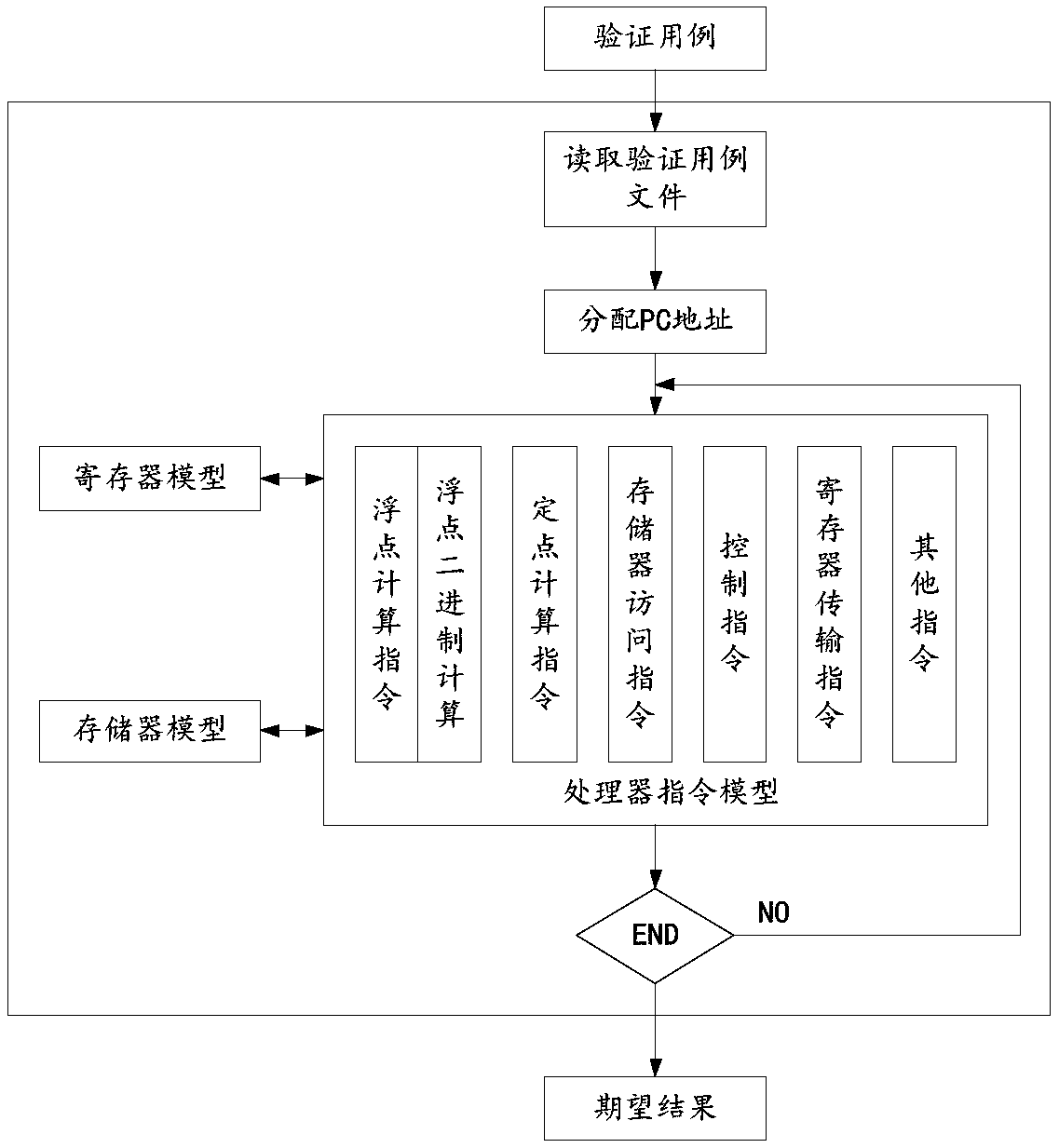

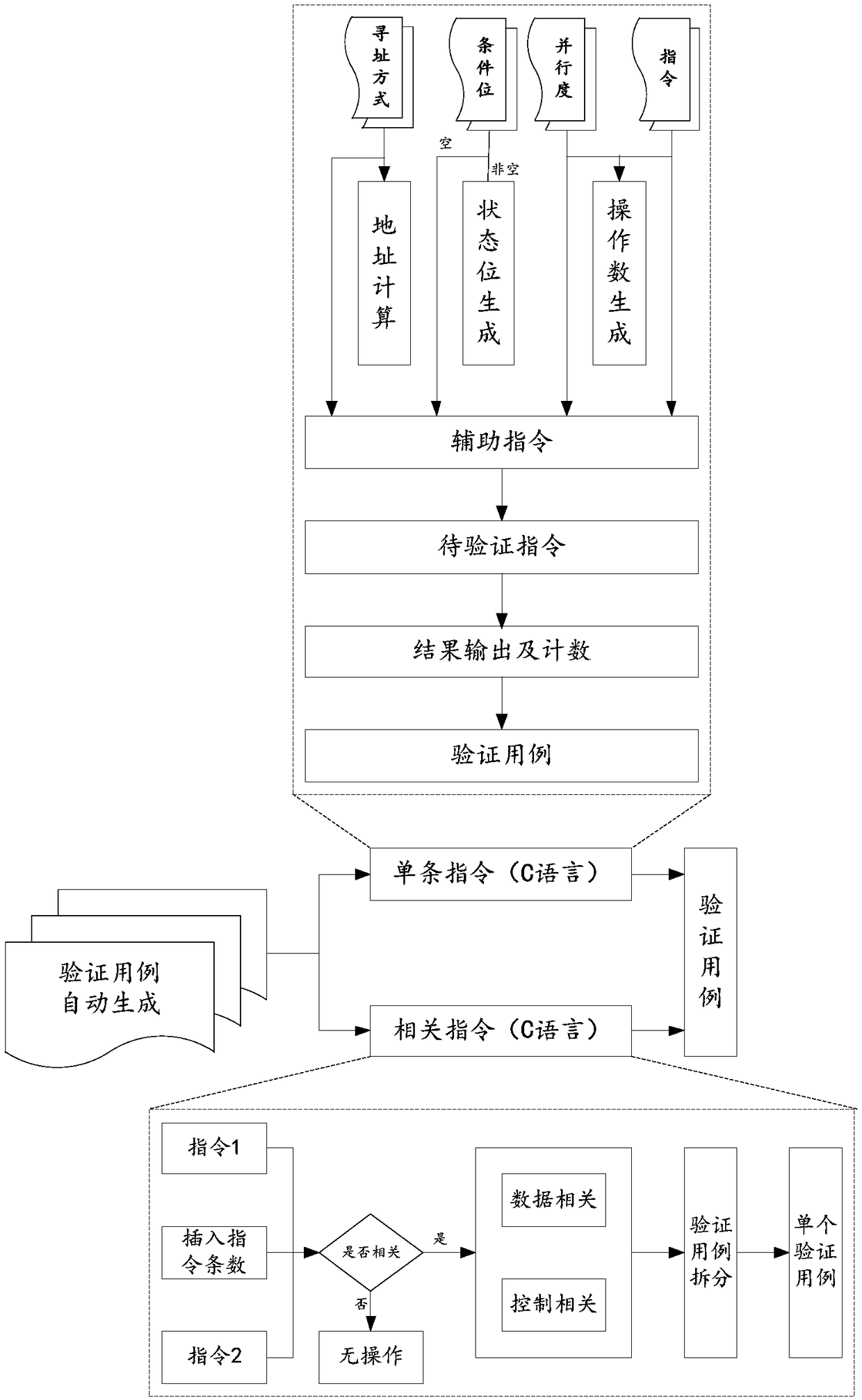

[0035] Aiming at the problem of huge processor verification space, the proposed processor instruction verification method can automatically generate a large number of single and cross instruction verification cases; it can truly simulate the operation of the processor, automatically identify instructions, and automatically generate expected results , which solves the problems of difficult control and query of the destination address of the jump instruction, and the expected result cannot be automatically calculated; it can also realize batch parallel simulation and automatic inspection of simulation results, and generate result log files at the same time, which is convenient for quick location and analysis of problems, and improves verification. Simulation coverage and efficiency.

[0036] In the most ideal situation, the method can traverse each instruction, each reg...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More