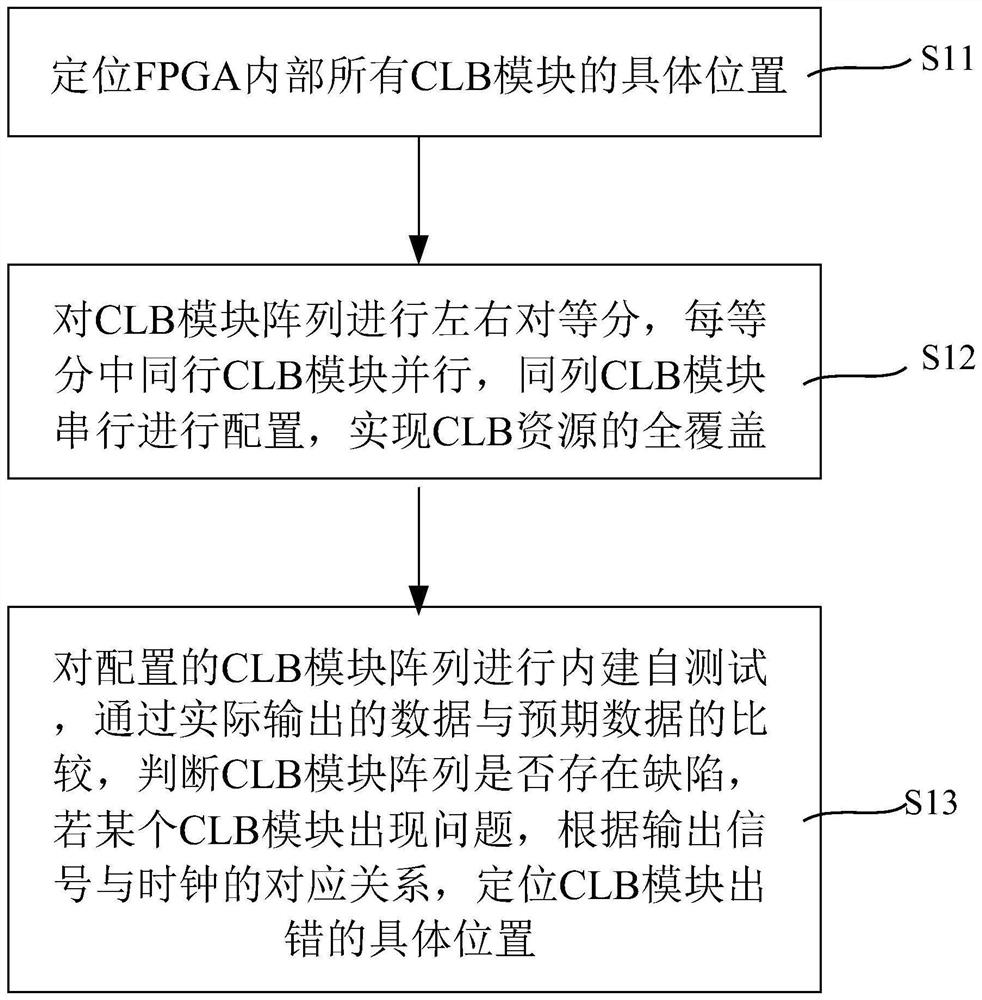

K series fpga internal clb module positioning and general configuration test method

A configuration testing and universal technology, applied in the field of FPGA testing, can solve the problems of complicated configuration program design, difficult to locate CLB array, poor configuration program portability, etc. Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

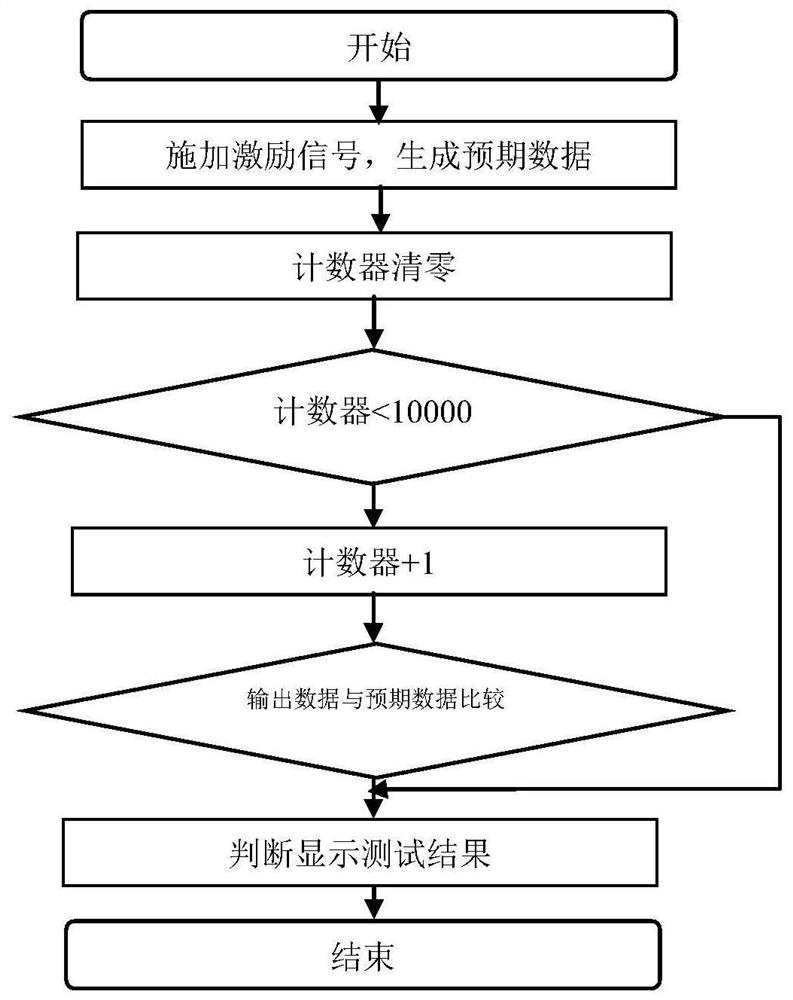

[0020] Taking the 7K410T-1FFG9000 (a high-end FPGA product produced by Xilinx) with a wide range of applications as an example, the specific design and built-in self-test are carried out. The specific steps are as follows.

[0021] Step 1, CLB module array positioning.

[0022] Find the specific location of the hole, for example, the first hole on the left is: SLICE_X24Y100-SLICE_X24Y199, SLICE_X35Y100-SLICE_X35Y199.

[0023] Because the address of the "hole" array is less, the design of inverting the address of the hole array is adopted to optimize the program. For the convenience of understanding, define X LL Y LL It is the position of the lower left corner of the first hole array, that is, SLICE_X24Y100, and other positions are the same as X LL The operation is similar.

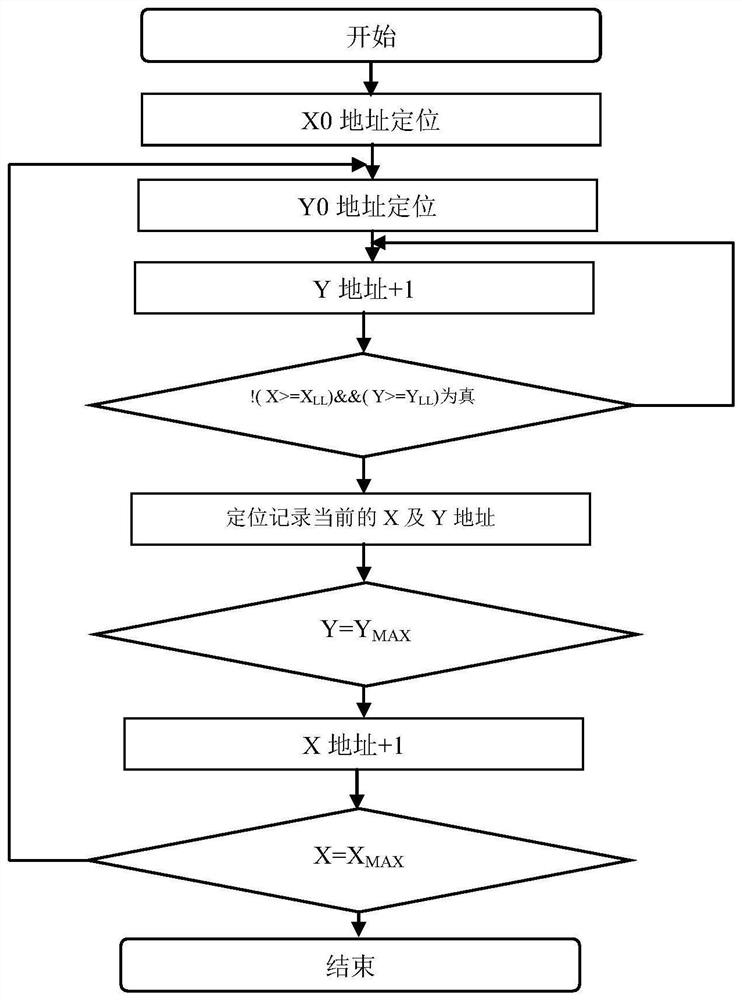

[0024] figure 2 It is a schematic flowchart of a CLB module positioning program provided by Embodiment 1 of the present invention. refer to figure 2 ,

[0025] a. First locate the X0 and Y0 addres...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com