A video chaotic secure communication device and method

A technology of secure communication and chaotic encryption, which is applied in the directions of secure communication devices, image communication, digital transmission systems, etc., can solve problems such as difficult processing and difficult Ethernet transmission design, and achieve the effect of improving computing speed

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

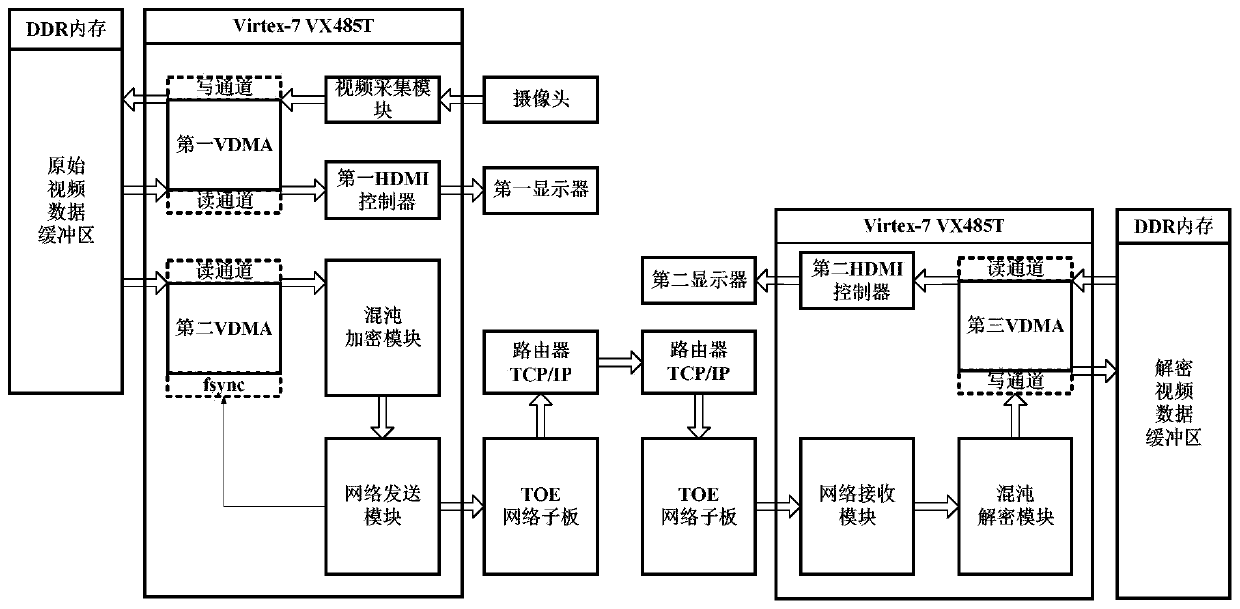

[0069] figure 1 It is a schematic structural diagram of a video chaos secure communication device provided in Embodiment 1 of the present invention. Such as figure 1 As shown, the embodiment of the present invention provides a video chaos secure communication device, which includes:

[0070] Video sending end and video receiving end, described video sending end comprises the first FPGA chip, raw video data buffer, data sending device, camera and first display, described video receiving end comprises the second FPGA chip, deciphered video data buffer area, a data receiving device and a second display;

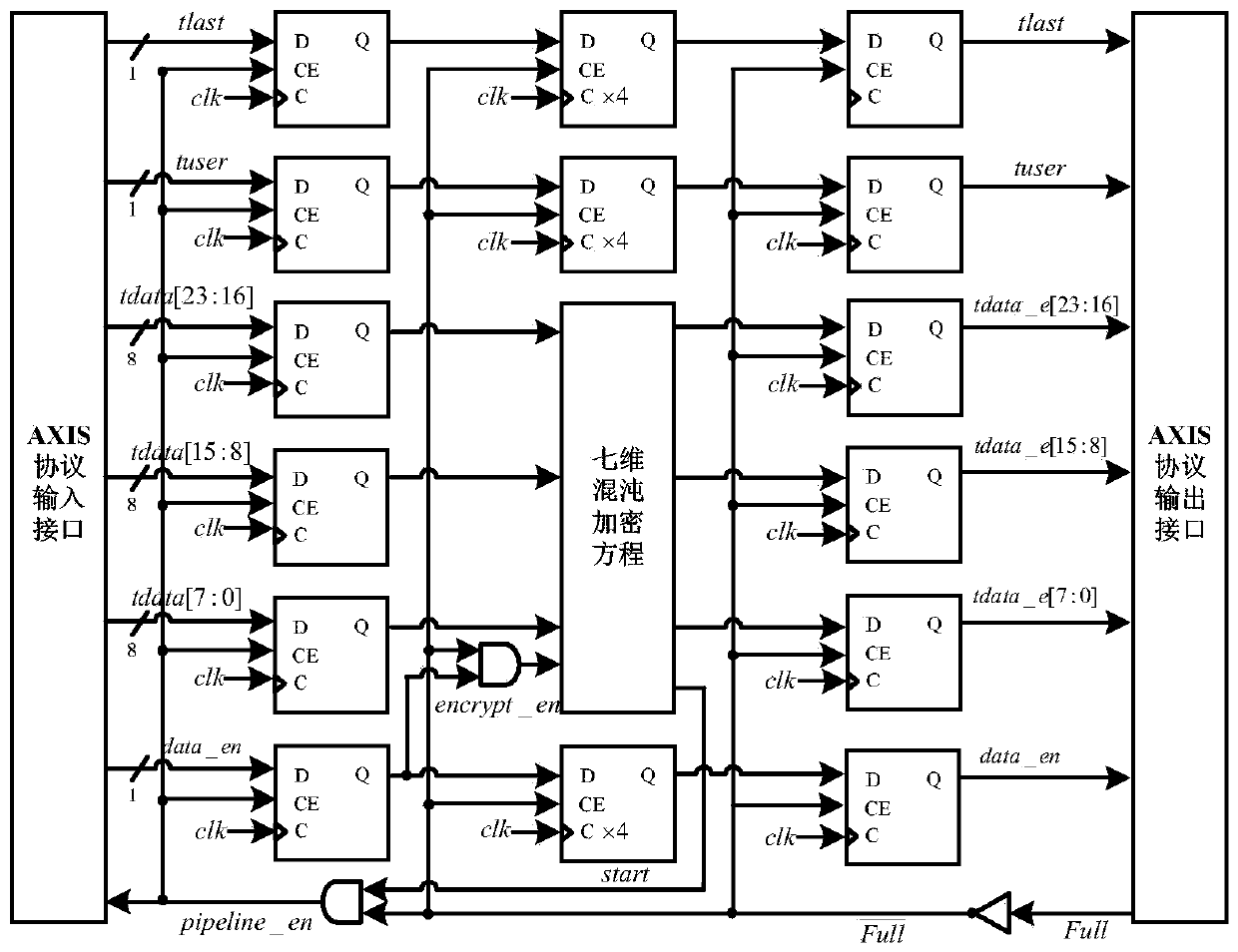

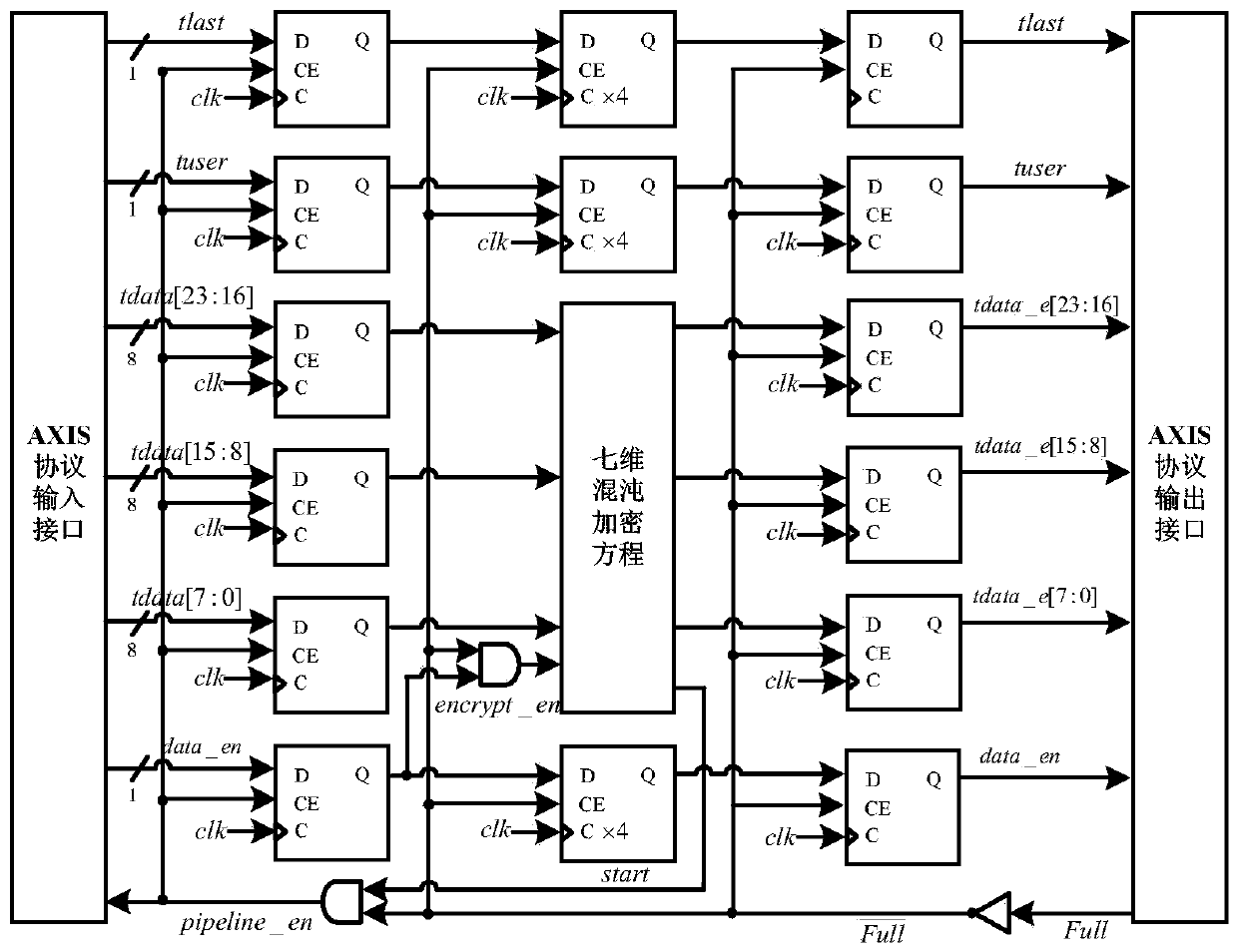

[0071] The first FPGA chip includes a video acquisition module, a first HDMI controller, a first VDMA, a second VDMA, a chaotic encryption module and a network sending module;

[0072] The video acquisition module is used to control the camera to collect video data, and save it to the original video data buffer through the first VDMA;

[0073] The first HDMI controller is co...

Embodiment 2

[0138] Embodiment 2 of the present invention provides a video chaos secure communication method. The method is performed by the video chaos secure communication device provided by the embodiment of the present invention, the video chaos secure communication device includes a video sending end and a video receiving end, and the video sending end includes a first FPGA chip, an original video data buffer, a data Sending device, camera and first display, described video receiving terminal comprises second FPGA chip, deciphered video data buffer, data receiving device and second display; Described first FPGA chip comprises video capture module, first HDMI controller , the first VDMA, the second VDMA, a chaotic encryption module and a network sending module; the second FPGA chip includes a second HDMI controller, the third VDMA, a chaotic decryption module and a network receiving module; the method includes:

[0139] The video acquisition module controls the camera to collect video ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More