Transmitting circuit based on DDR writing channel

A technology for transmitting circuits and channels, applied in electrical digital data processing, instruments, etc., can solve the problems of difficult timing convergence and high timing requirements, and achieve the effect of solving timing convergence

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

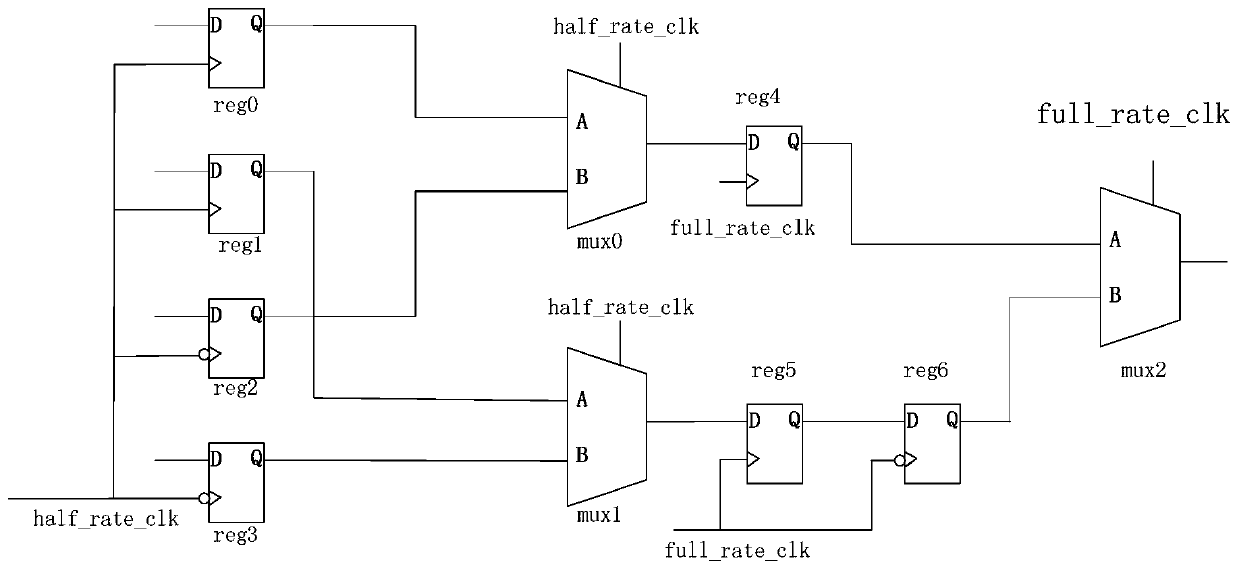

[0021] The present invention will be further described below in conjunction with accompanying drawing.

[0022] see figure 1 , the transmitting circuit based on the DDR write channel of the present invention includes first to seventh registers reg0-reg6, and first to third clock selectors mux0-mux2. In this embodiment, the first to seventh registers reg0-reg6 are all single-bit registers. The first to third clock selectors mux0-mux2 are all clock selectors that choose one of the two.

[0023] The respective clk terminals of the first to fourth registers reg0-reg3 receive a half_rate_clk frequency-divided clock signal of a DDR clock signal of the same frequency.

[0024] Respective output terminals of the first register reg0 and the third register reg2 are respectively connected to two input terminals of the first clock selector mux0 . Respective output terminals of the second register reg1 and the fourth register reg3 are connected to two input terminals of the second clock...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More