System for increasing number of valid display bits

A technology of bits and data, applied in the field of new systems that increase the number of effective display bits, and can solve problems such as difficult to achieve, high grayscale value accuracy, and noise easily generated by analog signals.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

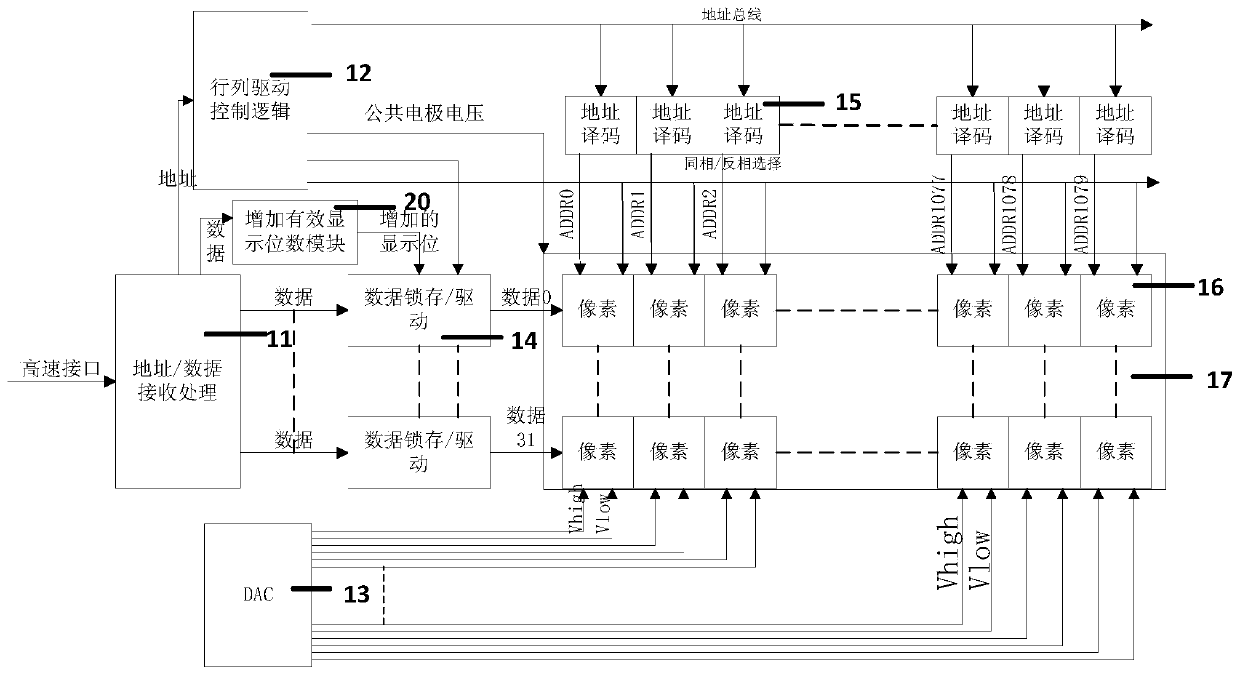

[0047] Embodiment 1 is a micro-display chip driven by digital pixels based on LCOS (liquid crystal on silicon), the pixel resolution is 1920*1080, and the color rendering method is sequential color.

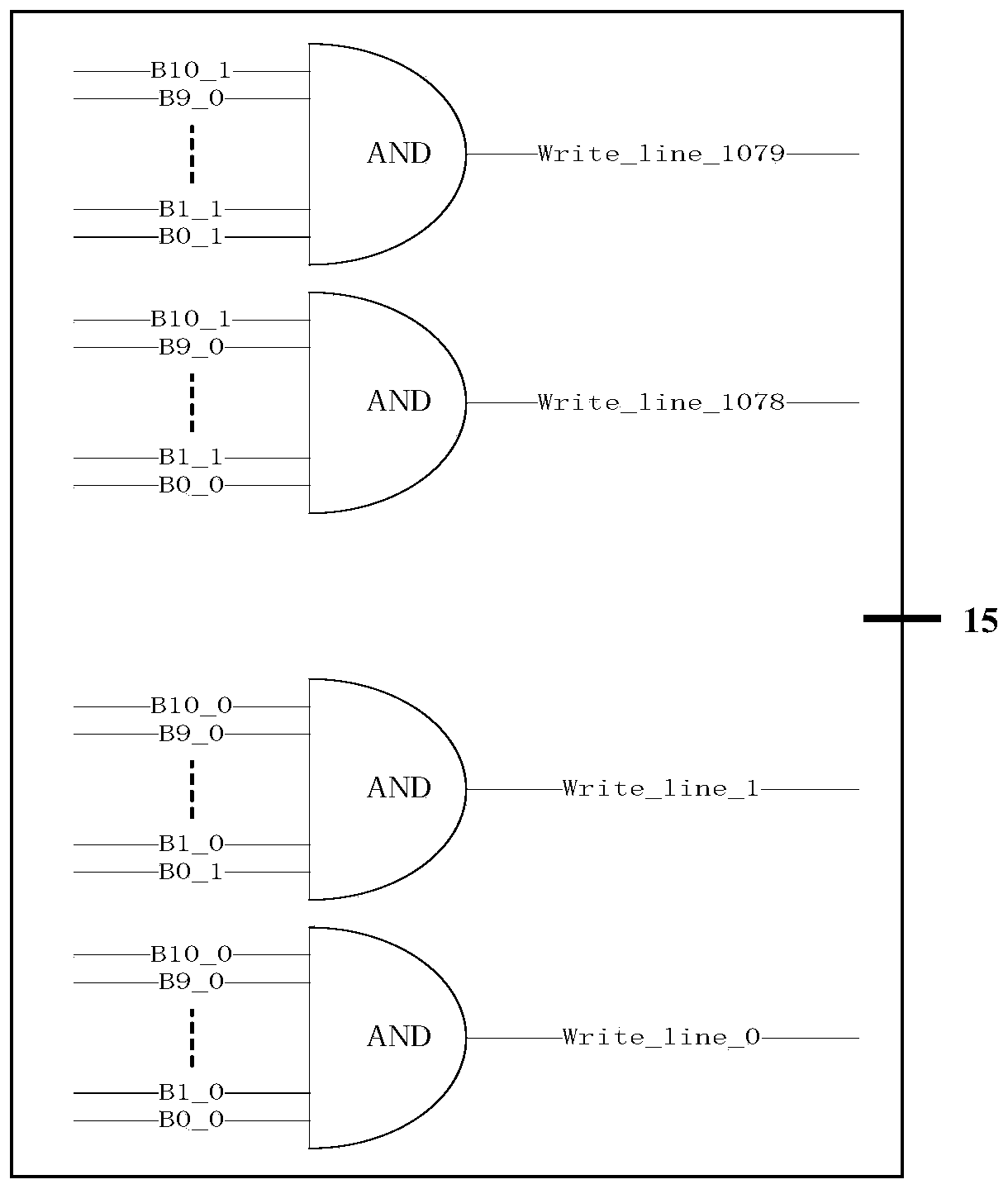

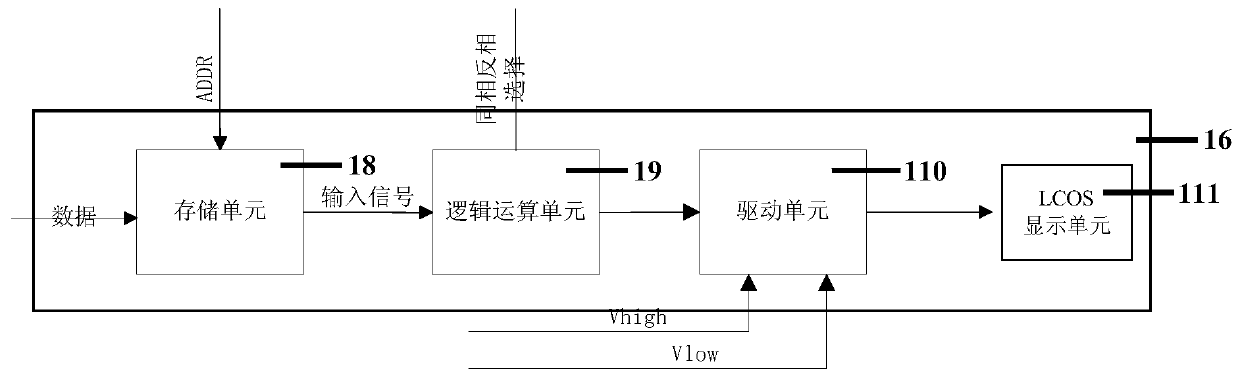

[0048] Such as figure 1 As shown, the micro-display chip system based on LCOS digital pixel drive mainly includes an address / data receiving and processing module 11, a row and column drive control logic module 12, a DAC module 13, a data latch / drive module 14, an address decoding module 15, and a pixel unit 16. The common electrode 17 and the module 20 for increasing the number of effective display digits.

[0049] The high-speed interface can use mipi interface or lvds interface, etc., and each time the row address and the data of the corresponding row are sent. The address / data receiving and processing module 11 receives one end connected to the high-speed interface, receives the address and data signals transmitted by the high-speed interface, the address / data receiving and p...

Embodiment 2

[0063] Embodiment 2 is a micro-display chip driven by OLED digital pixels. The resolution of the pixels is 1280*540*RGB.

[0064] Such as Figure 9 As shown, the micro-display chip system based on OLED digital pixel drive mainly includes an address / data receiving and processing module 21, a row and column drive control logic module 22, a DAC module 23, a data latch / drive module 24, an address decoding module 25, and a pixel unit 26. A common electrode 27 and a module 28 for increasing effective display digits.

[0065] The high-speed interface can use mipi interface or lvds interface, etc., and each time the row address and the data of the corresponding row are sent. The address / data receiving and processing module 21 receives one end connected to the high-speed interface, receives the address and data signals transmitted by the high-speed interface, and the address / data receiving and processing module 21 extracts the received address and data signals, and extracts the addres...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More