Test system and test method

A technology for testing systems and devices under test, applied in software testing/debugging, error detection/correction, instruments, etc., can solve problems such as low board-level testing efficiency, achieve high testing efficiency, and improve testing efficiency

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

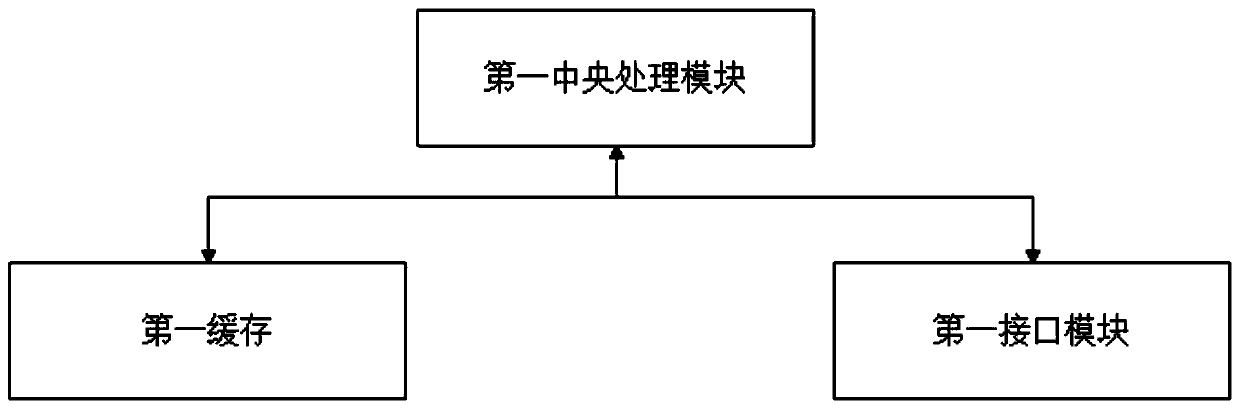

[0020] figure 1 It is a schematic structural diagram of a test system provided by an embodiment of the present invention. Such as figure 1 As shown, the test system includes:

[0021] A first central processing module, a first cache, and a first interface module connected to each other; the first interface module is connected to the device under test;

[0022] The first interface module is configured to read the first data to be tested from the first buffer and send it to the device under test, and receive the second data to be tested from the device under test and cache it in the first cache;

[0023] The first central processing module is configured to determine that the data transmission test of the device under test is successful when the first data to be tested and the second data to be tested meet a preset condition.

[0024] in,

[0025] The device under test is configured to cache the first data to be tested in a local second cache when receiving the first data to...

Embodiment 2

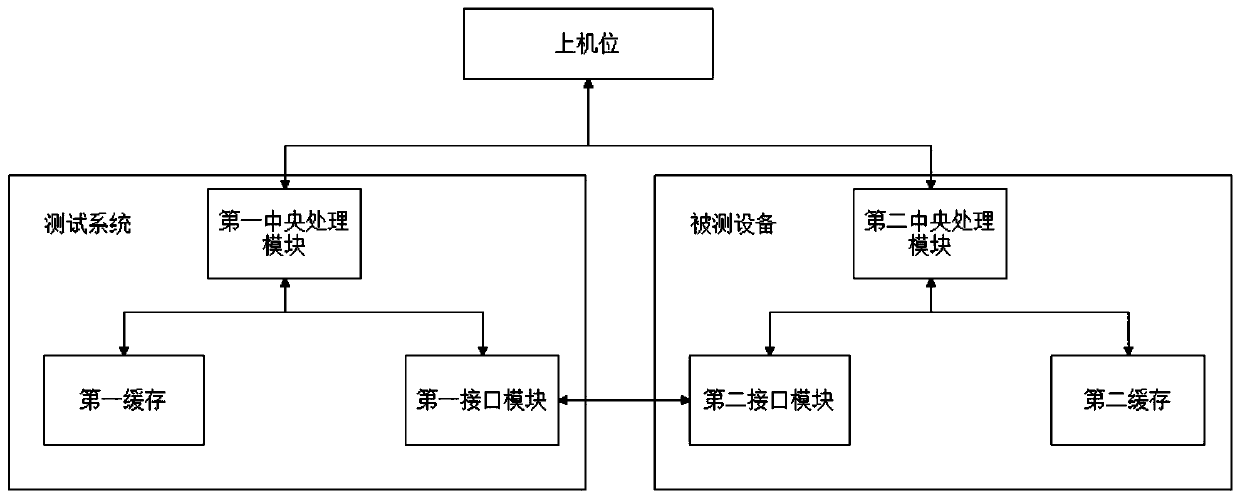

[0067] figure 2 It is a schematic structural diagram of a test platform provided by an embodiment of the present invention. Such as figure 2 As shown, the test platform includes: including the test system and the equipment under test;

[0068] The test system includes: a first central processing module CPM, a first cache, and a first interface module connected to each other; the first interface module is connected to a second interface module of the device under test;

[0069] The device under test includes: a second central processing module CPM, a second cache and a second interface module connected to each other; the second interface module is connected to the first interface module of the device under test.

[0070] Wherein, the first CPM is connected to the host position, receives the command of the host position, configures the preset condition according to the command of the host position and saves it in the first cache, and writes the first data to be tested into t...

Embodiment 3

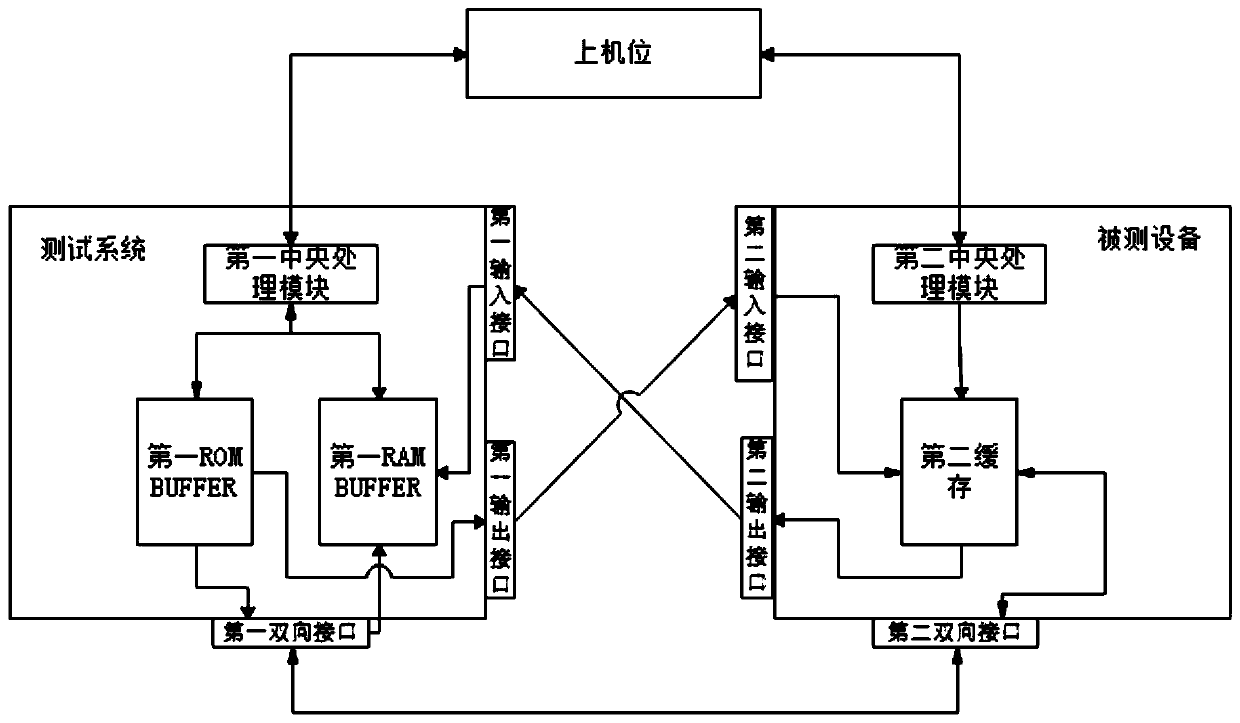

[0103] image 3 It is a schematic structural diagram of a test platform provided by another embodiment of the present invention.

[0104] Such as image 3 As shown, in this embodiment, on the basis of Embodiment 2, the first cache includes a first read-only memory buffer ROM Buffer and a first random access memory buffer RAM Buffer;

[0105] The first interface module includes: a first output interface, a first input interface, and a first bidirectional interface;

[0106] The second interface module includes: a second output interface, a second input interface, and a second bidirectional interface;

[0107] The first output interface is connected to the second input interface, the first input interface is connected to the second output interface, and the first bidirectional interface is connected to the second bidirectional interface;

[0108] The first data to be tested includes first digital data and first analog data; the second data to be tested includes second digital...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com