An apparatus and method for handling write operations

A technology for writing operations and processing equipment, which is applied in transaction processing, multi-programming devices, electrical digital data processing, etc., and can solve the problems of expensive hardware area and/or execution time, access to data, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

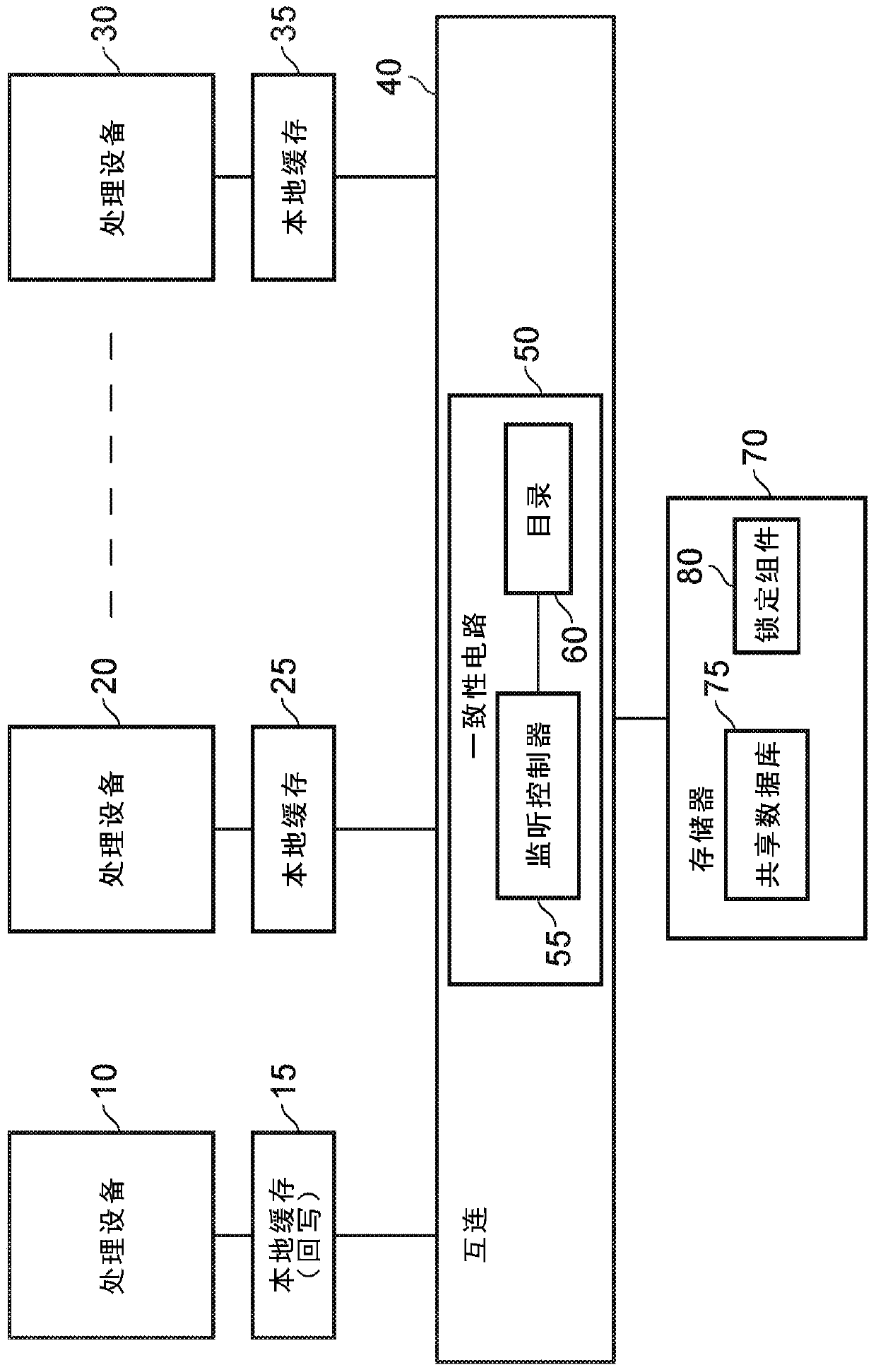

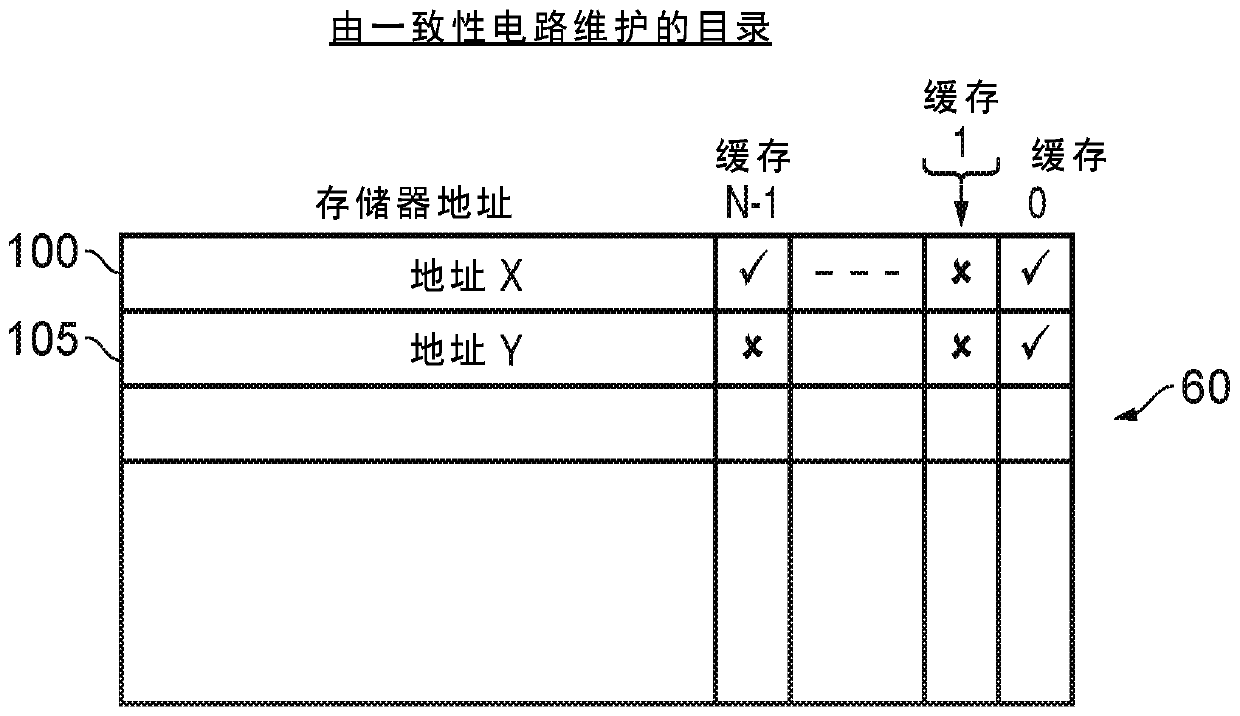

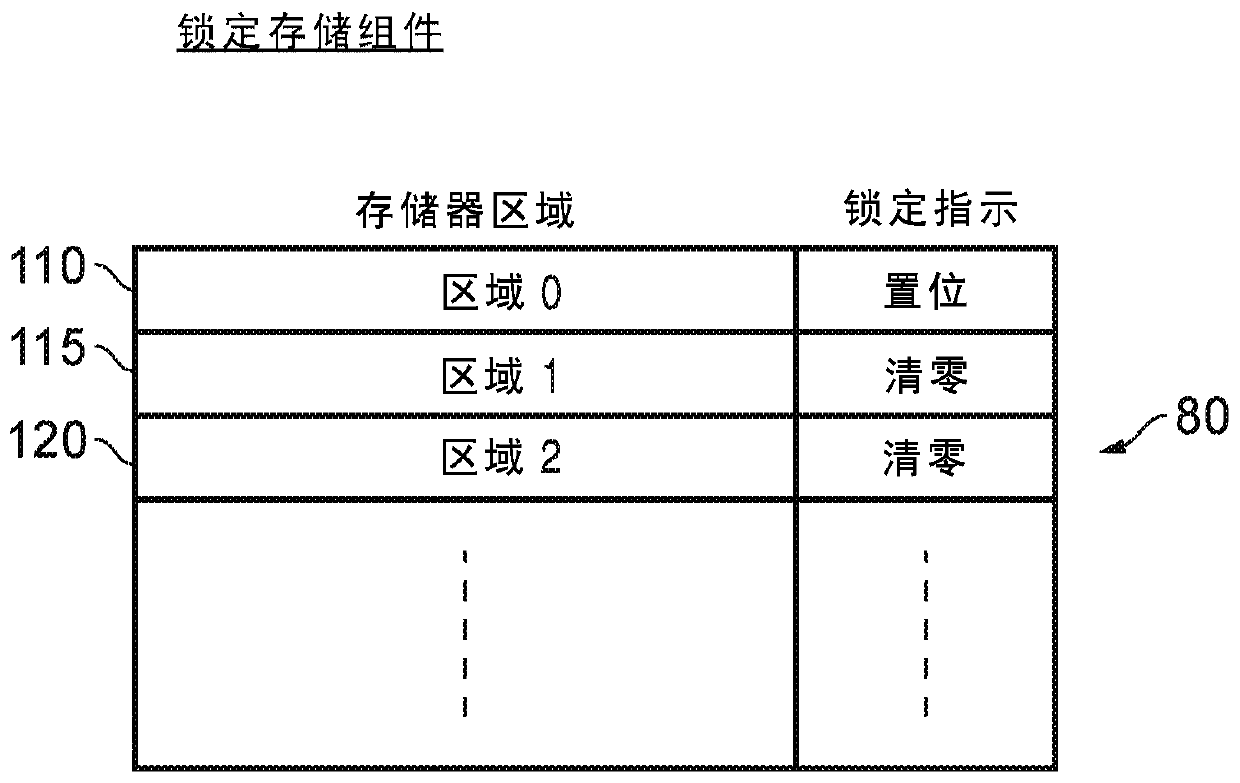

[0019] In systems that include multiple processing devices with their own local cache structures, cache coherence protocols are typically implemented to ensure that each processing device has the same view of the data shared between the processing devices. This cache coherency protocol needs to ensure that different processing devices cannot update data associated with a memory location in a conflicting manner, whereas if two different processing devices are allowed to perform write operations on the same data at the same time (this can be called "competing write" condition), this conflict may arise. Thus, when a write operation is required for data at a particular memory address, then according to known hardware cache coherency schemes, the processing device wishing to perform the write operation notifies the coherency circuitry so that the coherency circuitry then performs the any steps necessary to ensure that the requesting processing device can then perform the write oper...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com