Clock phase discrimination method and device

A clock and phase detection technology, applied in the field of network communication

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0026] In order to enable those skilled in the art to better understand the technical solutions in the embodiments of the present invention, and to make the above-mentioned purposes, features and advantages of the embodiments of the present invention more obvious and understandable, the following describes the technical solutions in the embodiments of the present invention in conjunction with the accompanying drawings For further detailed explanation.

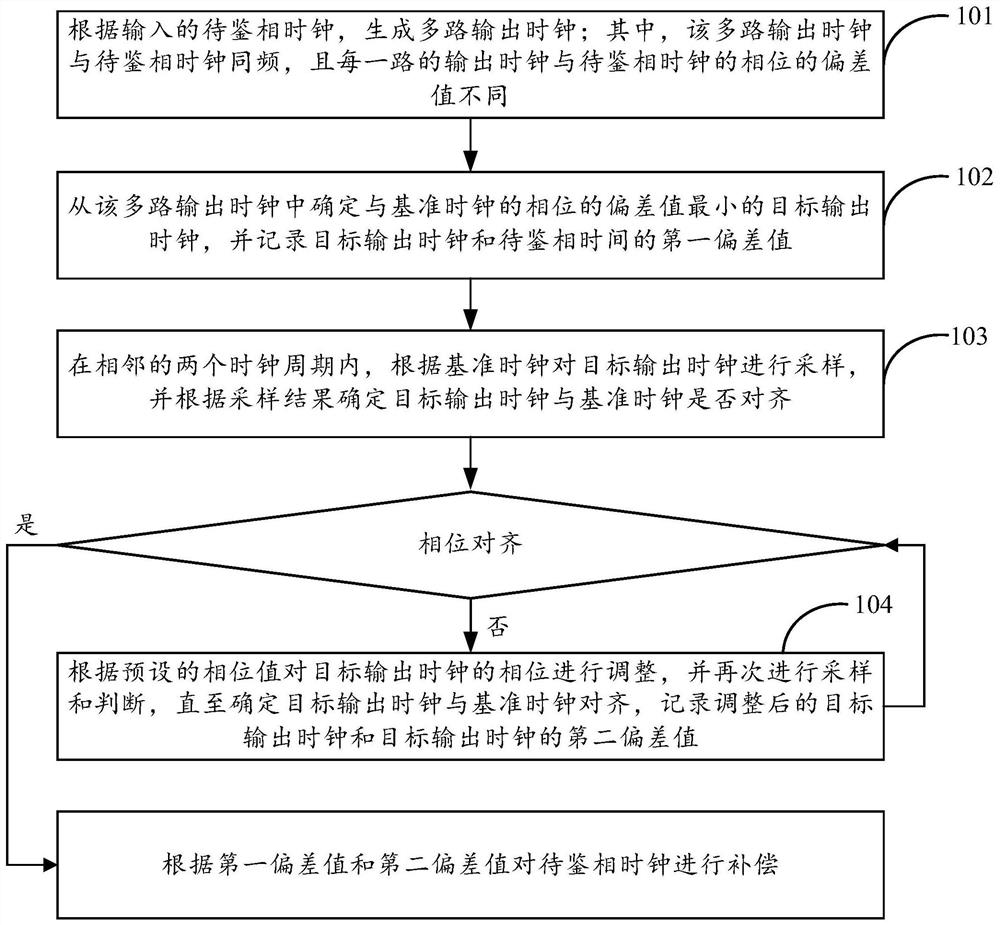

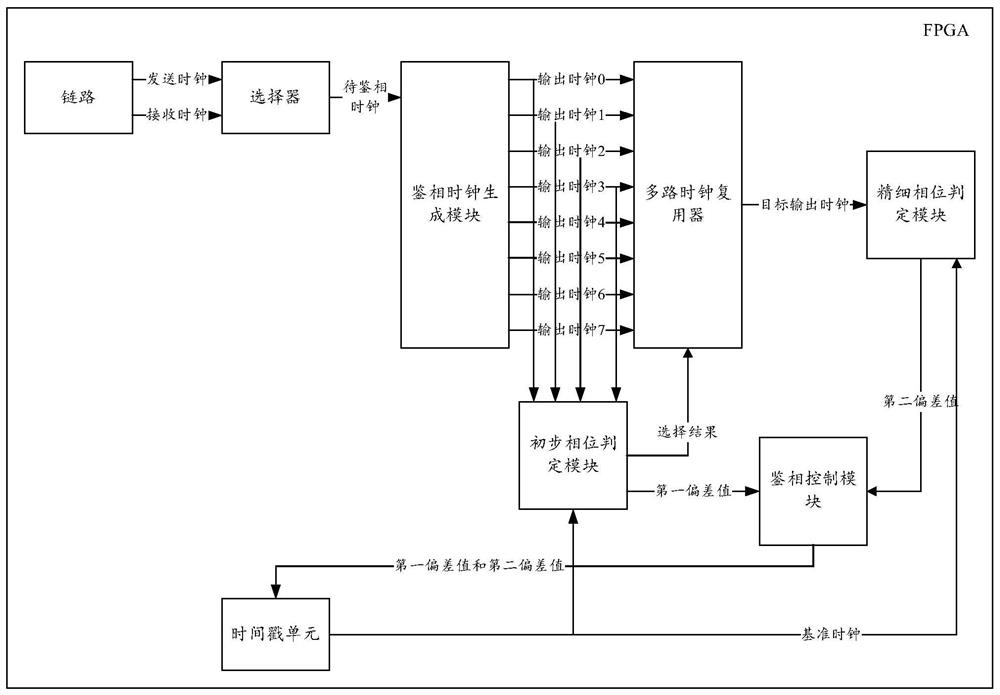

[0027] See figure 1 , is a schematic flowchart of a clock phase detection method provided by an embodiment of the present invention, wherein the clock phase detection method can be applied to FPGA, such as figure 1 As shown, the clock phase detection method may include the following steps:

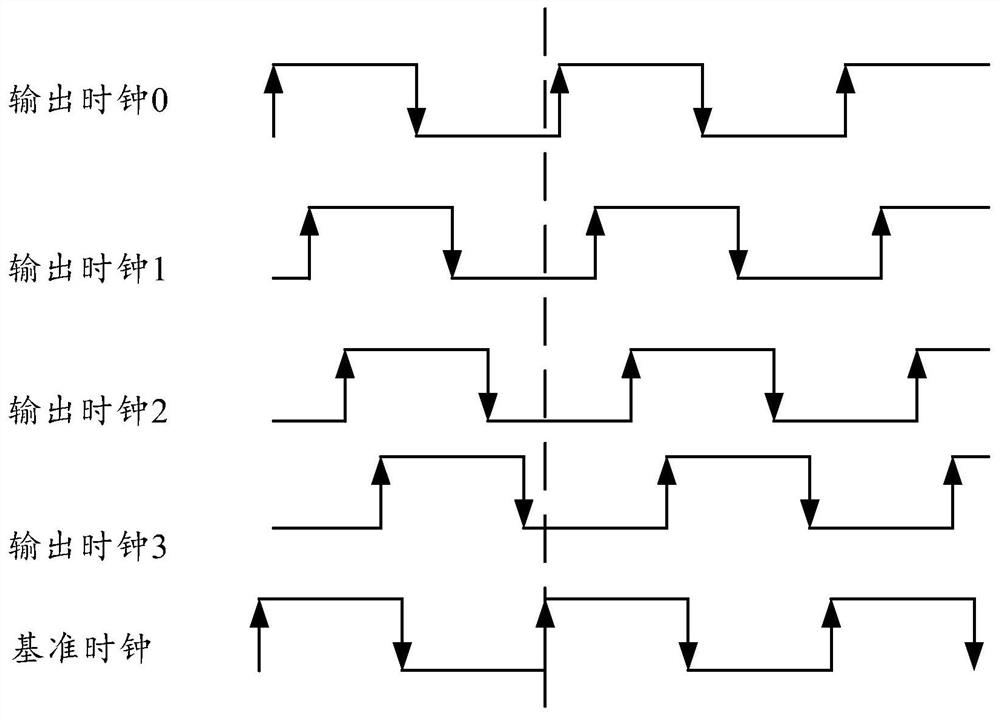

[0028] Step 101 : Generate multiple output clocks according to the input clocks to be phase-detected; wherein, the multiple output clocks are of the same frequency as the clocks to be phase-detected, and the phase deviations between the ou...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More