Patents

Literature

254 results about "Precision Time Protocol" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

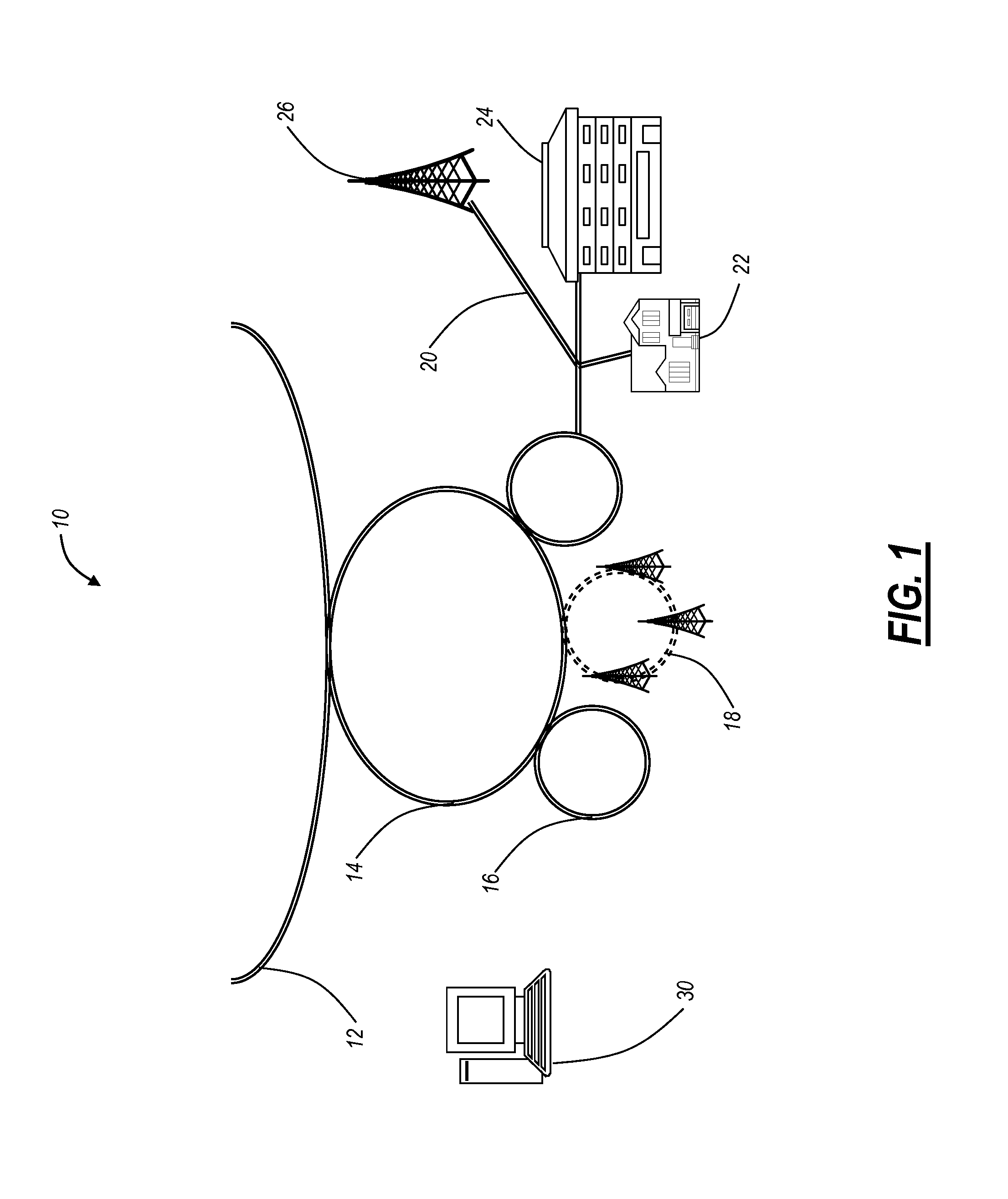

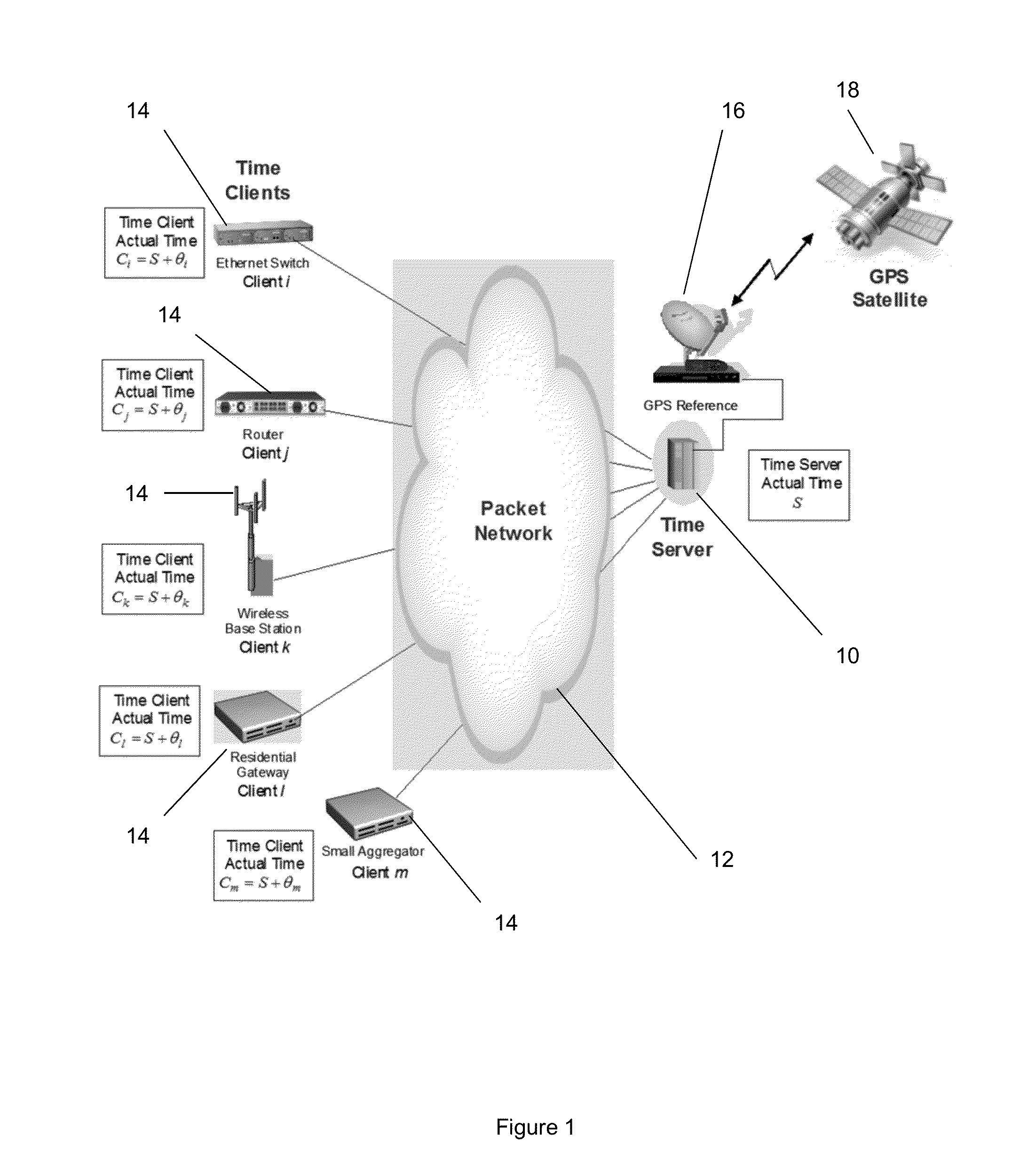

The Precision Time Protocol (PTP) is a protocol used to synchronize clocks throughout a computer network. On a local area network, it achieves clock accuracy in the sub-microsecond range, making it suitable for measurement and control systems. PTP is currently employed to synchronize financial transactions, mobile phone tower transmissions, sub-sea acoustic arrays, and networks that require precise timing but lack access to satellite navigation signals.

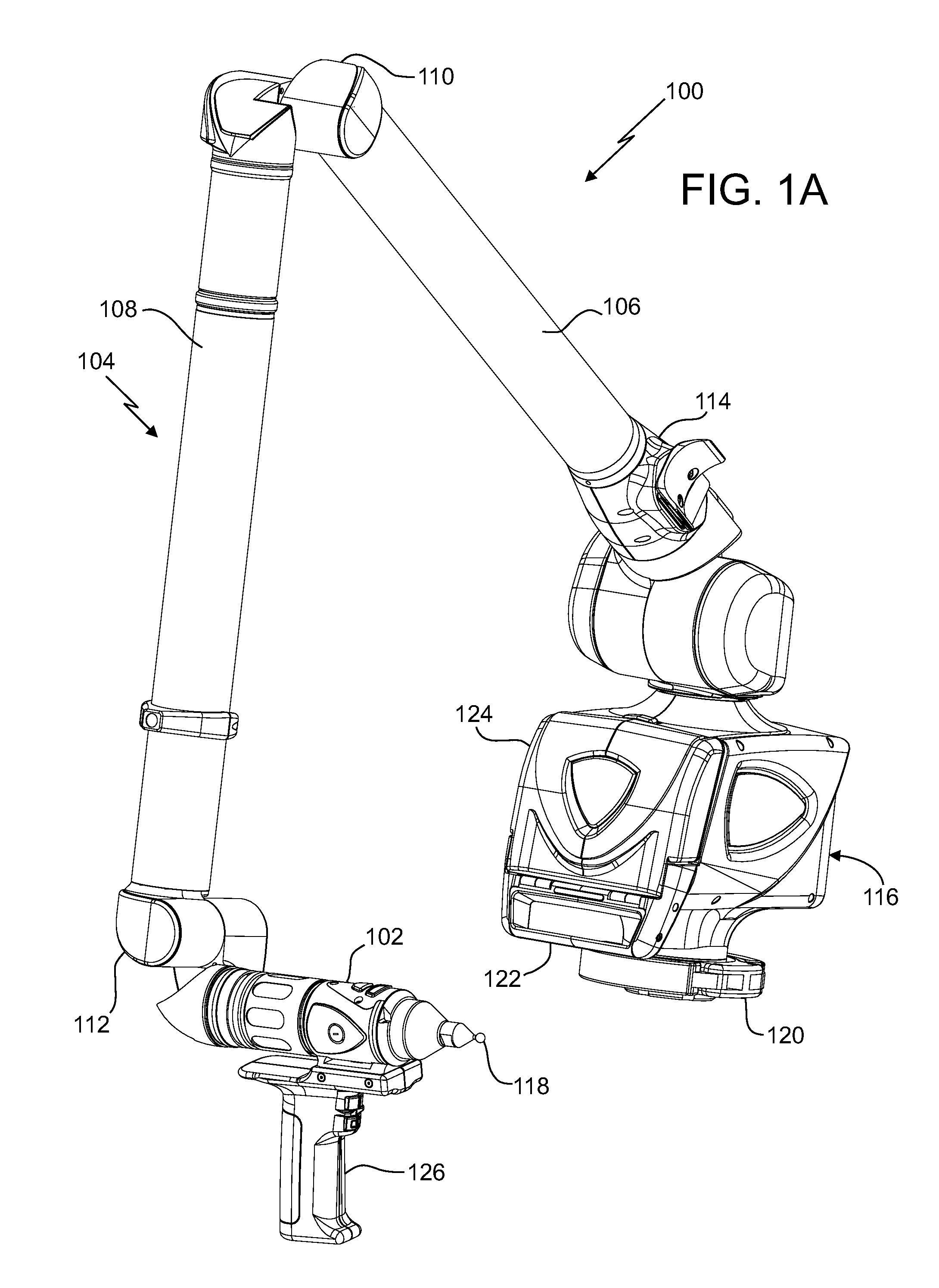

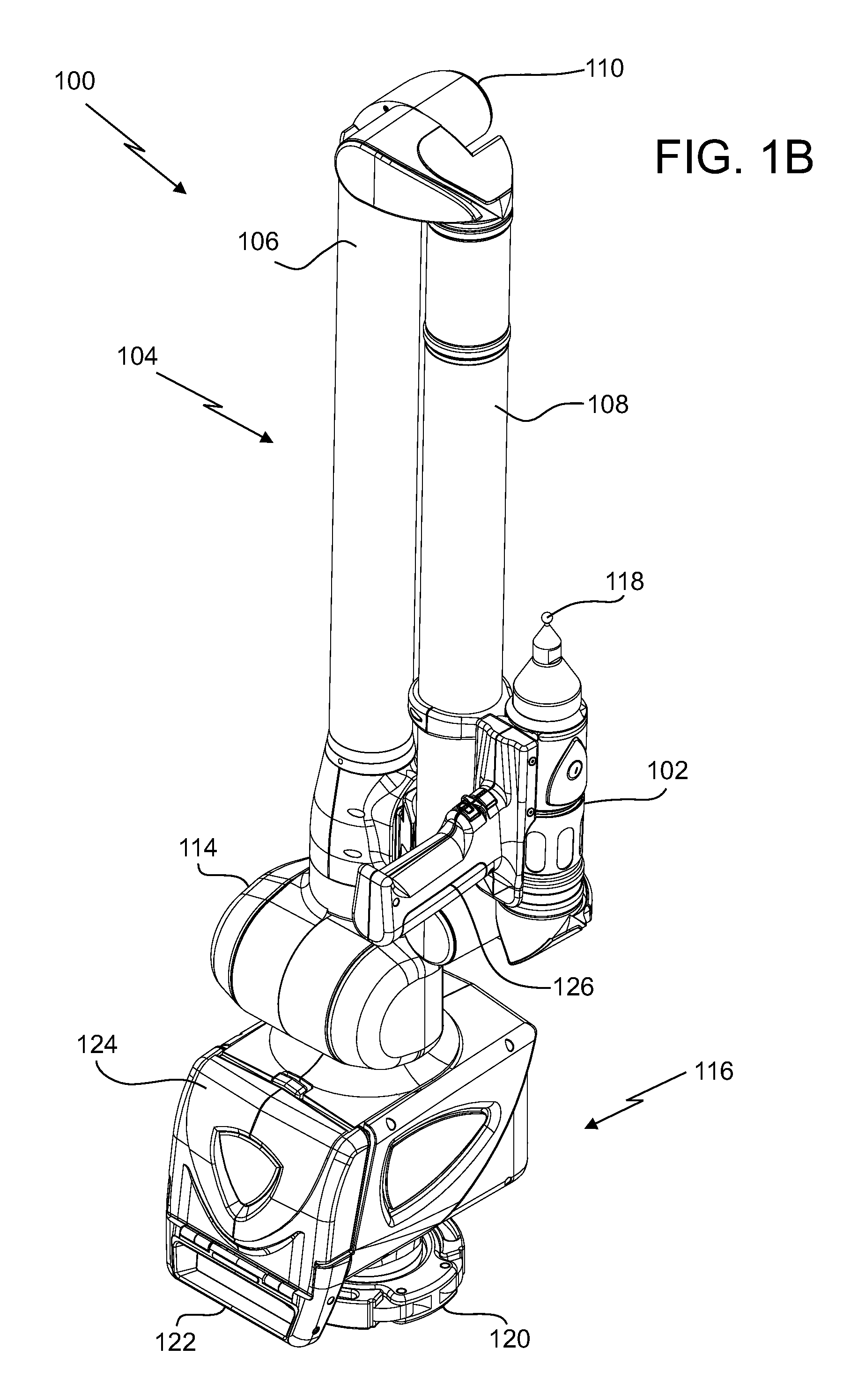

Method and apparatus for synchronizing measurements taken by multiple metrology devices

ActiveUS8630314B2Accuracy issueEasy to integrateTime-division multiplexUsing optical meansComputer hardwareMetrology

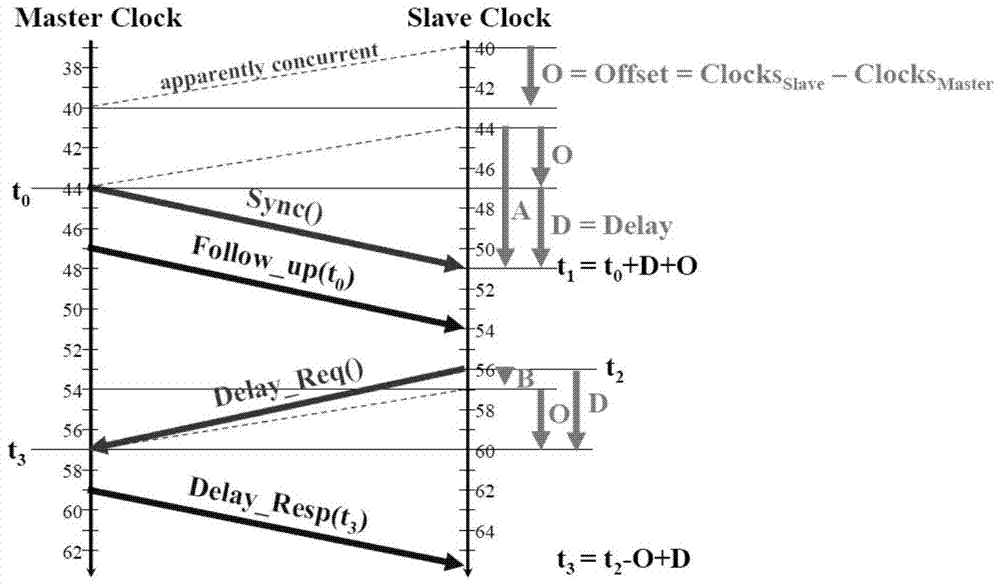

Apparatus includes at least two devices that communicate with each other, wherein a first one of the at least two devices having an IEEE 1588 precision time protocol interface, the interface including one or more components configured for communications in both a wired manner and a wireless manner with a second one of the at least two devices. The second one of the at least two devices having an IEEE 1588 precision time protocol interface, the interface including one or more components configured for communications in both a wired manner and a wireless manner with the first one of the at least two devices. Wherein one of the at least two devices includes a master clock and the other one of the at least two devices includes a slave clock, wherein the master clock communicates a time to the slave clock and the slave clock is responsive to the communicated time from the master clock to adjust a time of the slave clock if necessary to substantially correspond to the time of the master clock, thereby time synchronizing the at least two devices together.

Owner:FARO TECH INC

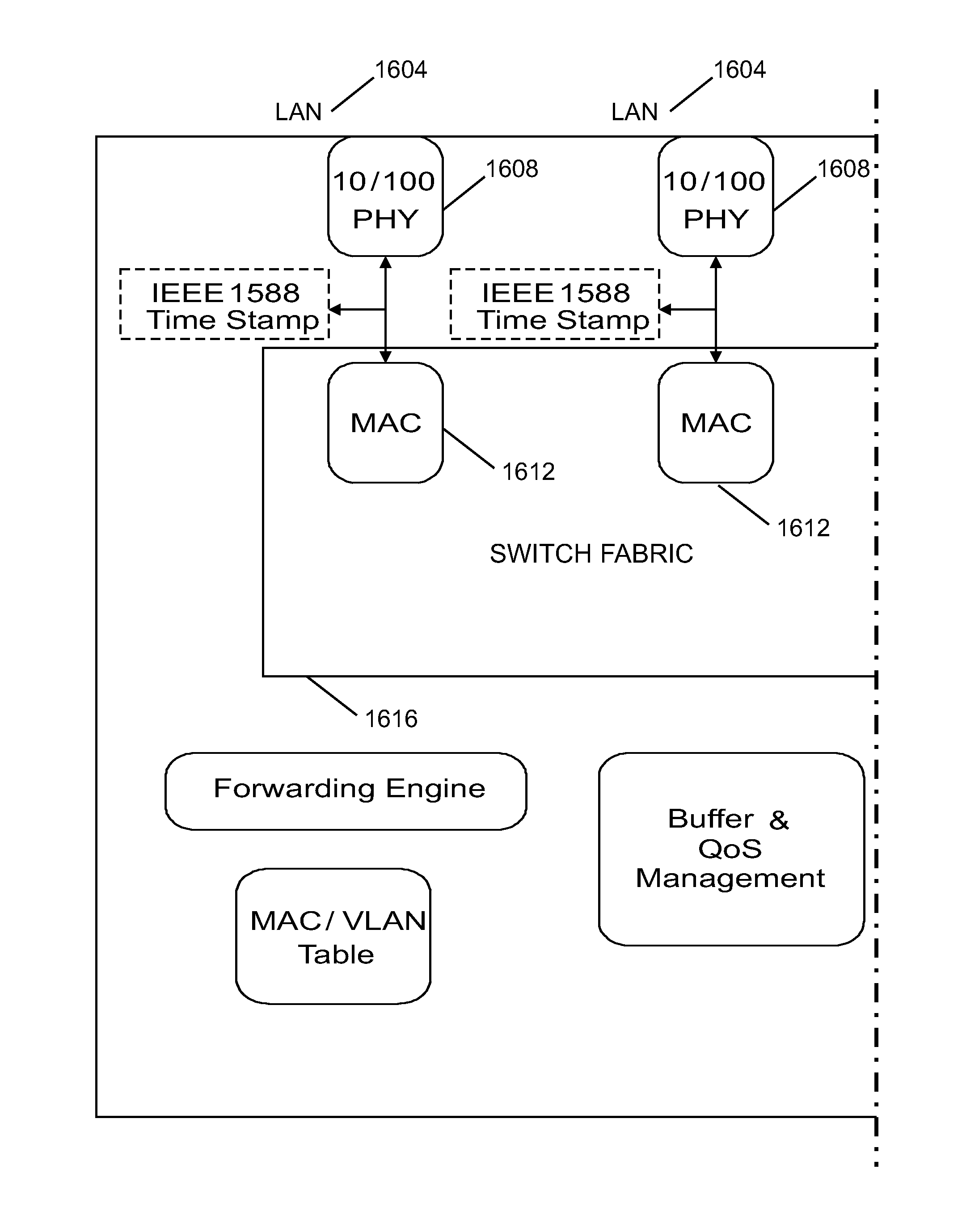

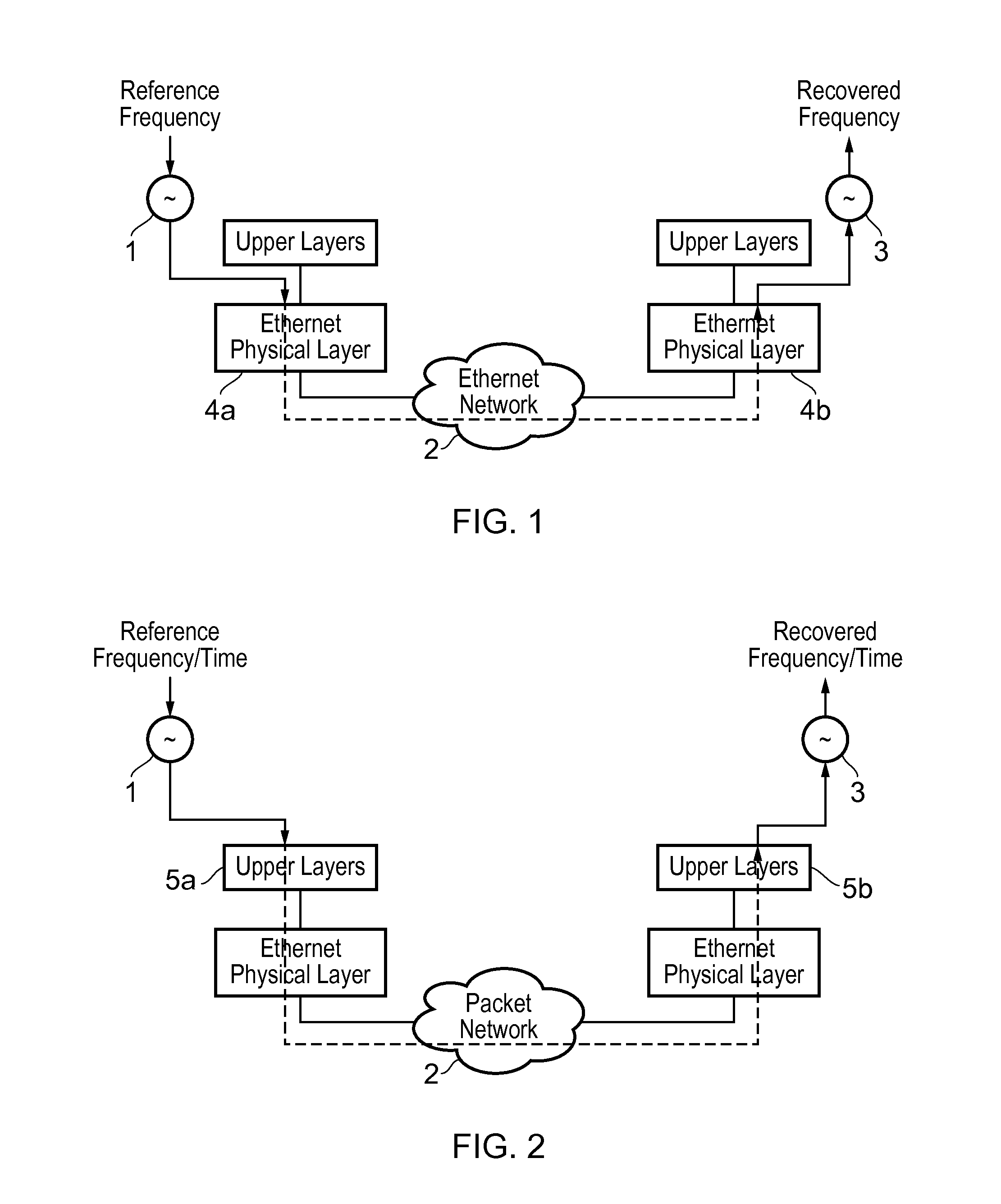

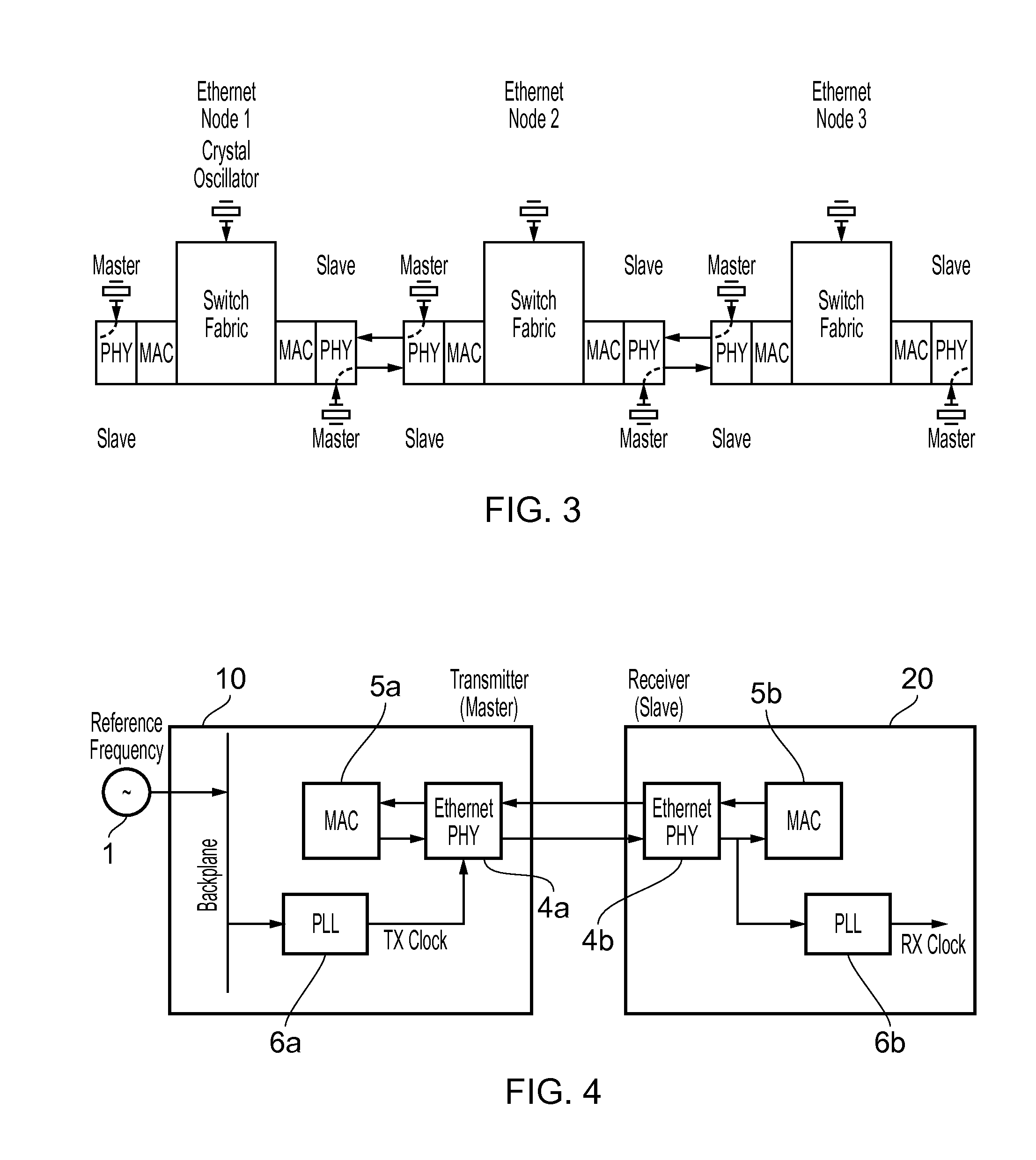

Ethernet network synchronization systems and methods

ActiveUS20110200051A1Reduce in quantityImprove stabilityTime-division multiplexData switching by path configurationSynchronization systemSynchronous Ethernet

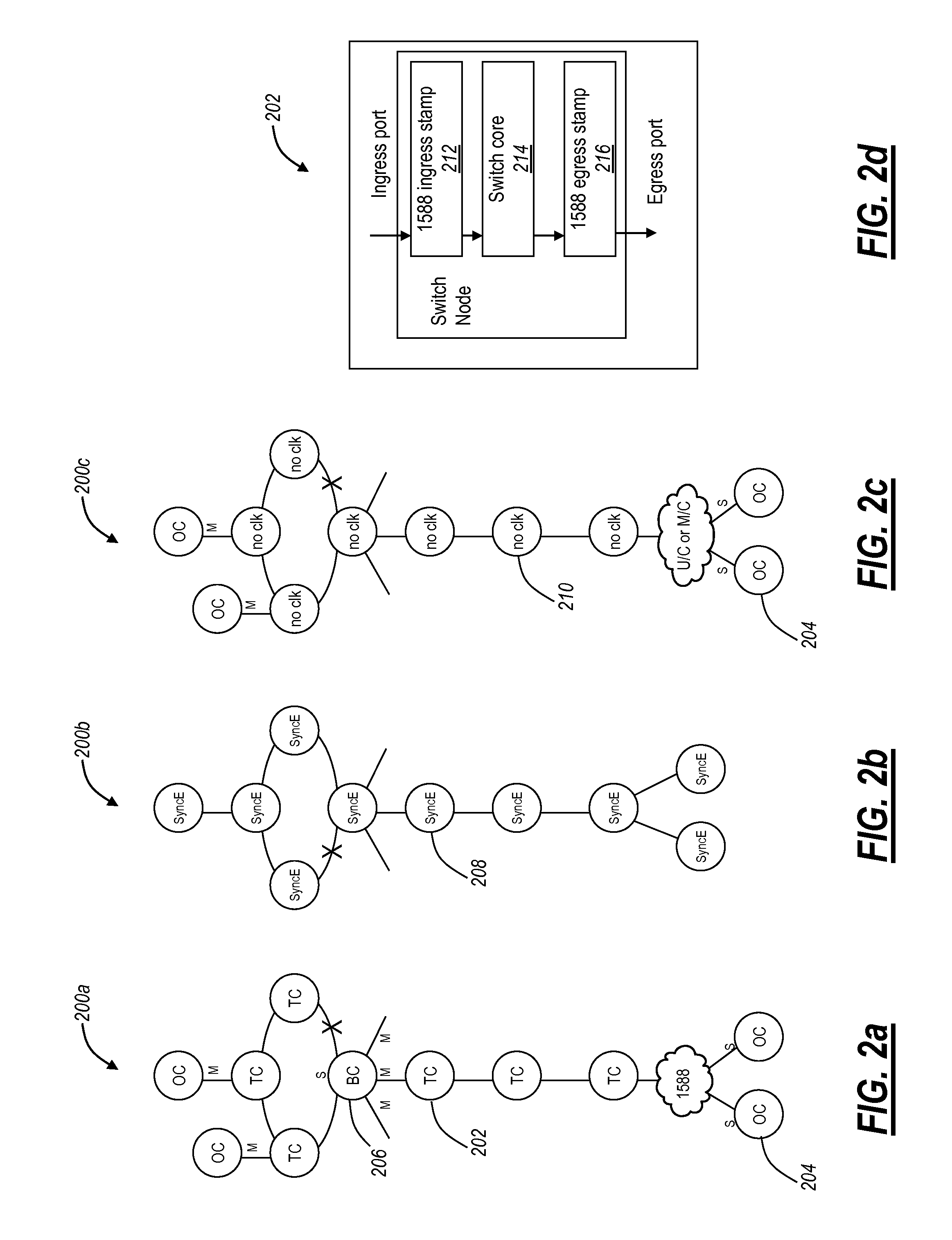

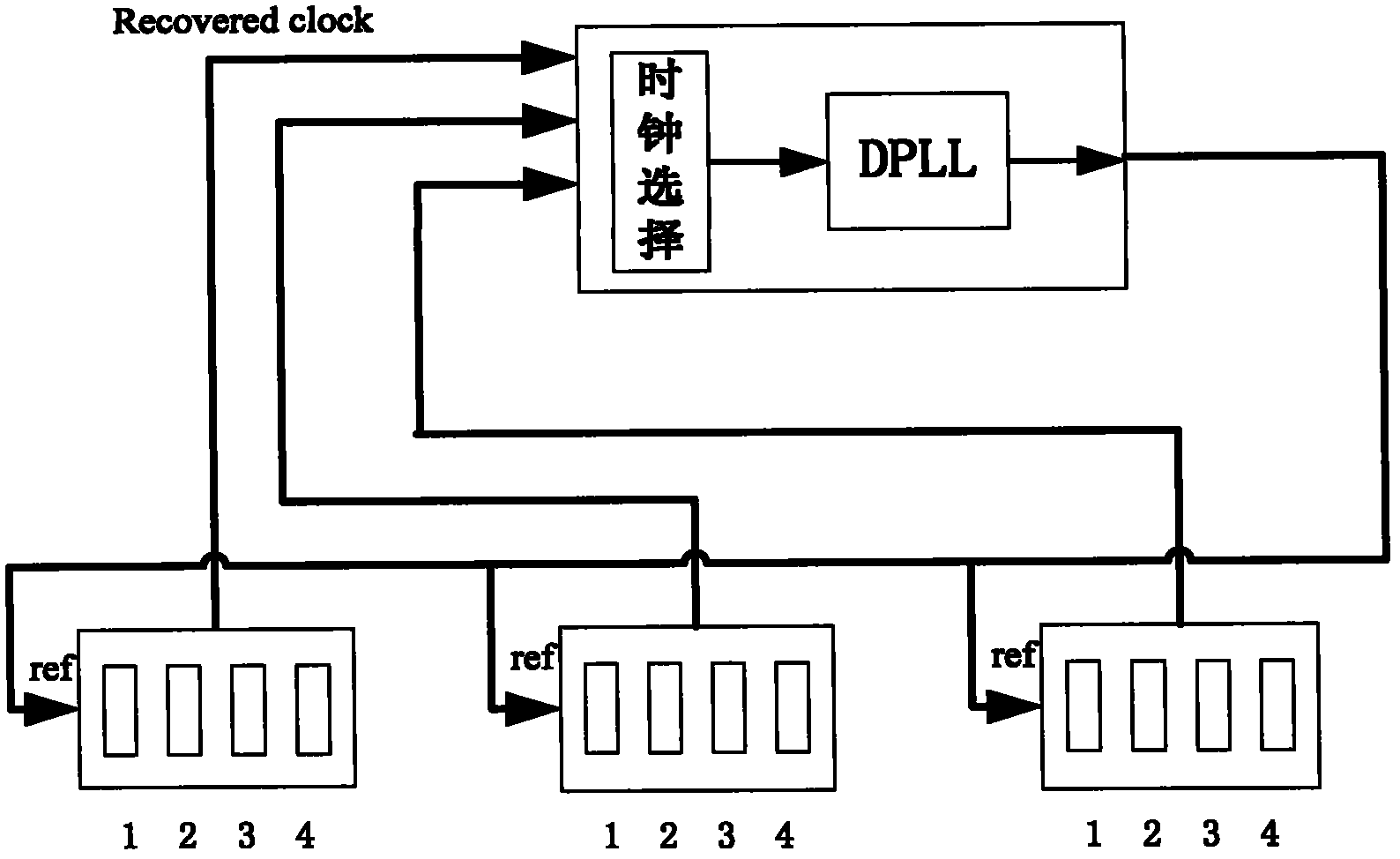

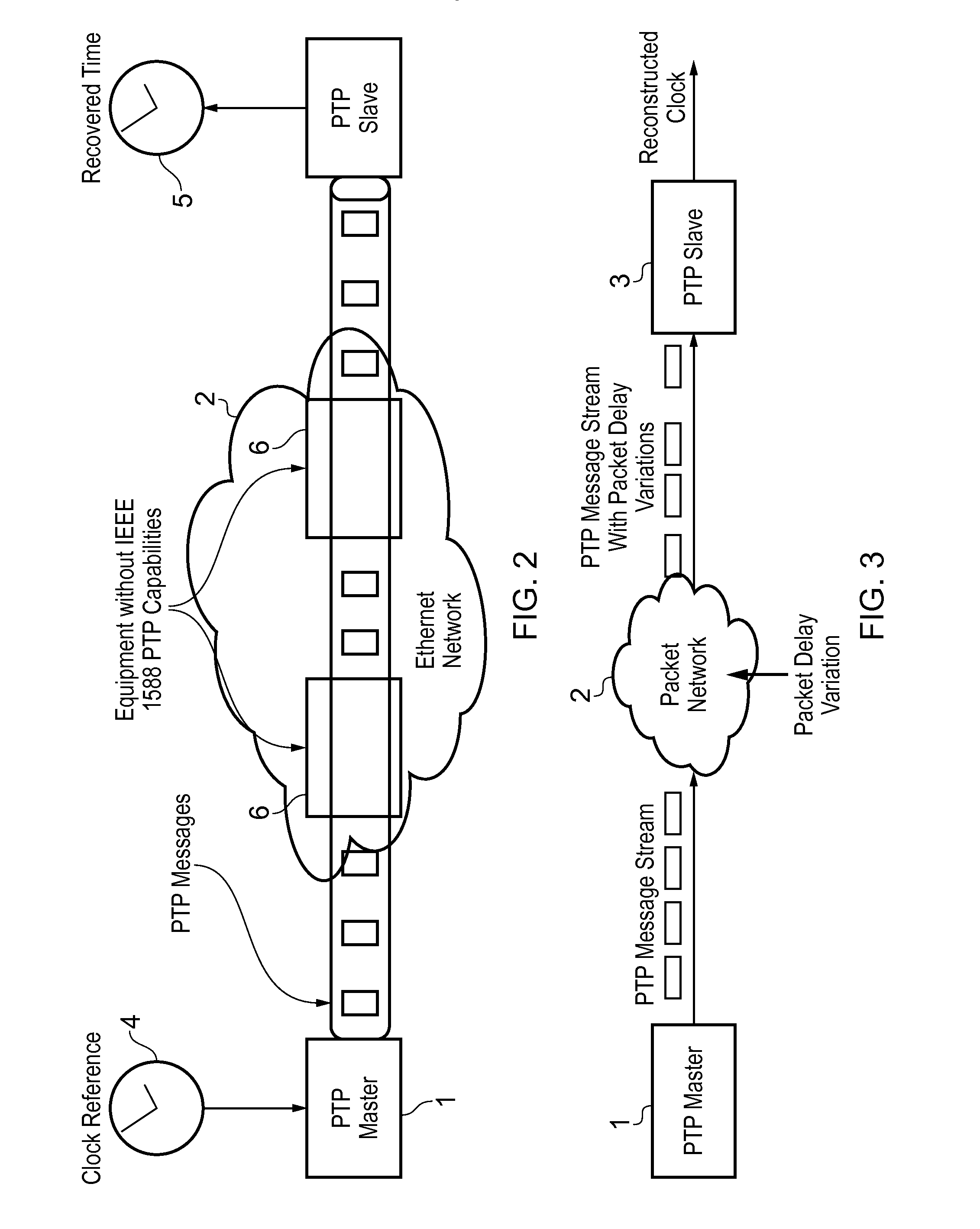

The present disclosure relates to Ethernet synchronization systems and methods that combines Synchronous Ethernet (Sync-E) and Precision Time Protocol (PTP) IEEE 1588 algorithms. The present invention includes systems and methods for Ethernet networks and node configurations that include a set of rules on node placement, such as Boundary Clock (BC) nodes and Sync-E nodes, a clock selection algorithm, a holdover algorithm, and the like. Advantageously, the present invention provides an architecture that allows practical and real-world useful clock propagation through placement of BCs and Sync-E nodes for best performance. Practical experience and theoretical design are embodied in the present invention to define a very specific set of rules on how to build a network capable of providing accurate and reliable synchronization. The present invention includes clock selection that unifies Sync-E and 1588 algorithms.

Owner:CIENA

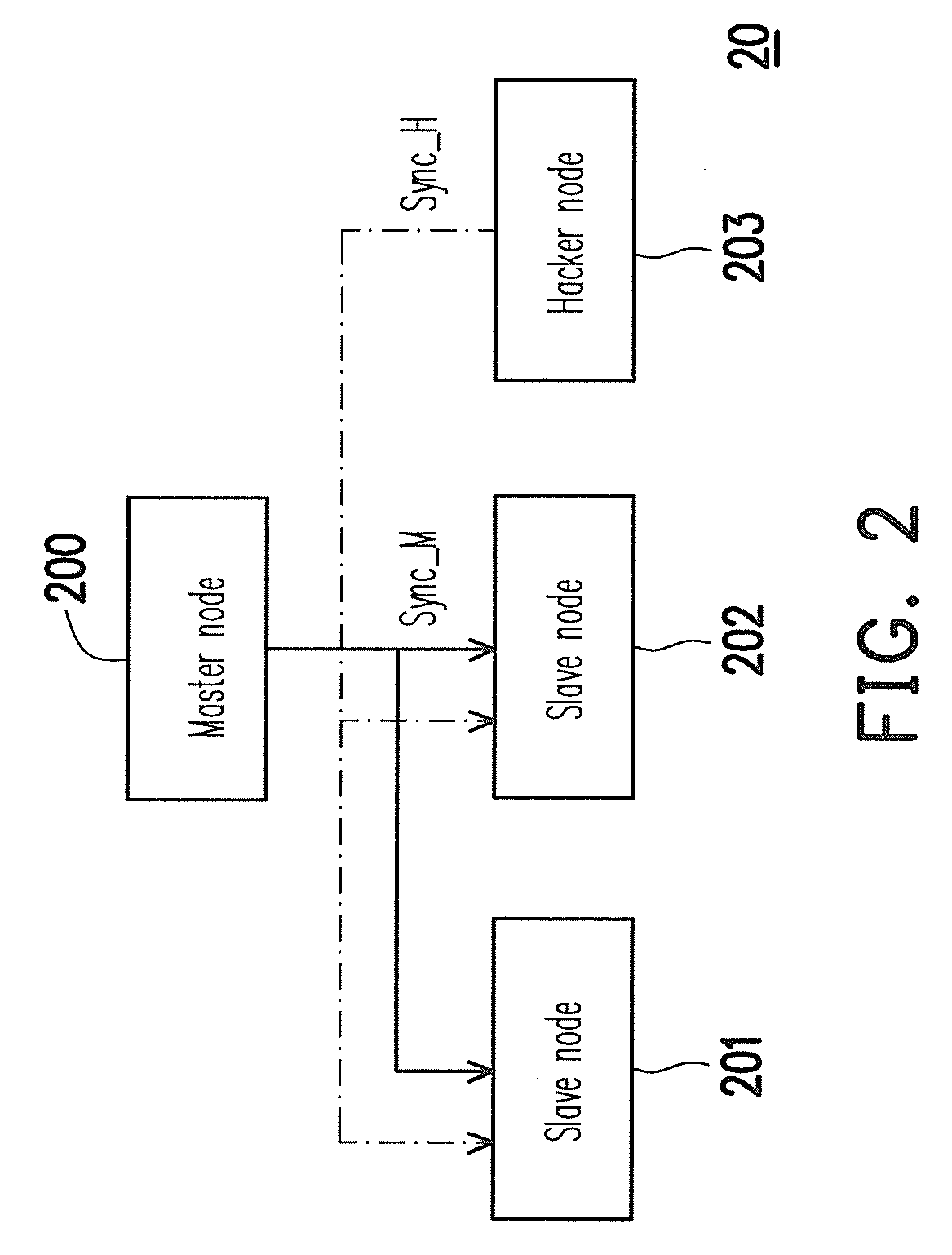

Network Slave Node and Time Synchronization Method in Network Applying the Same

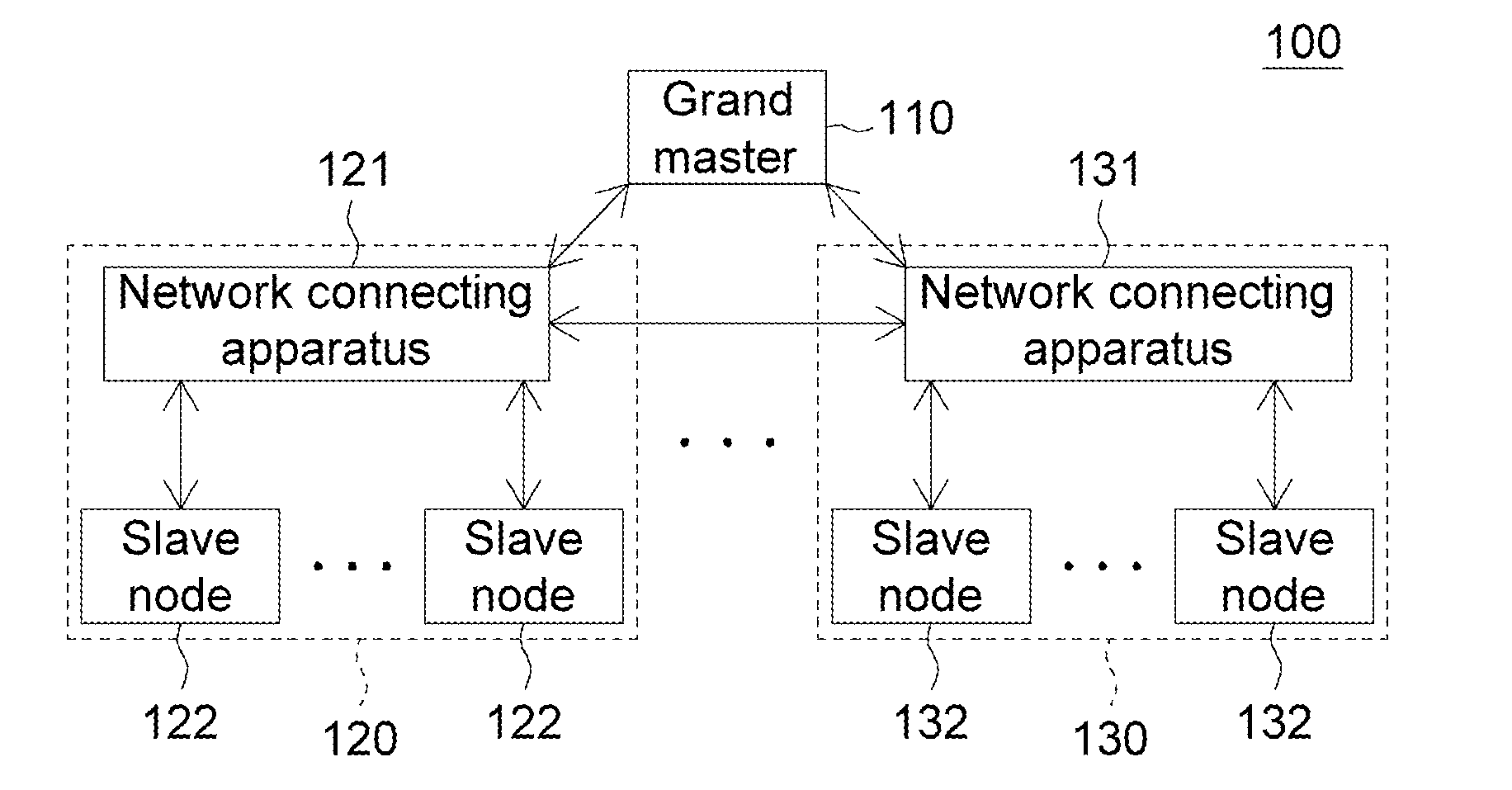

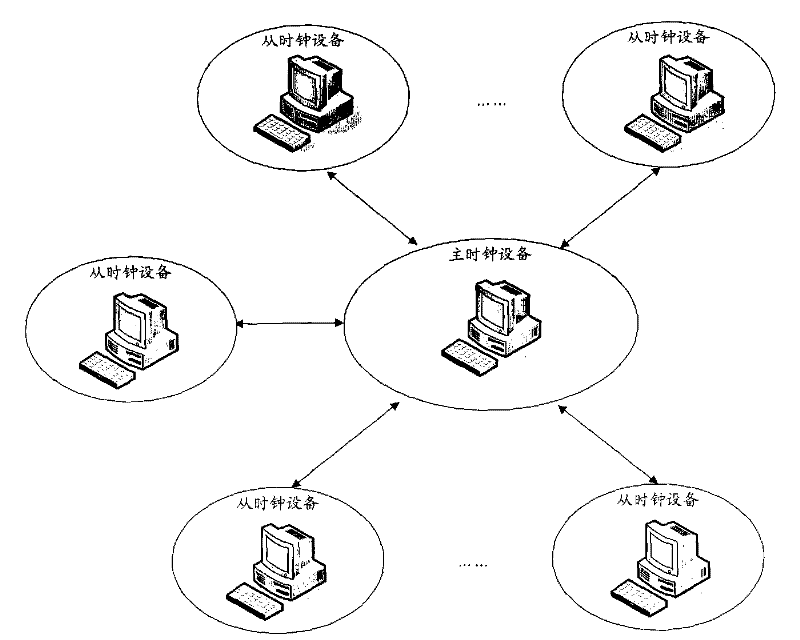

Provided are a network slave node and a time synchronization method using precision time protocol-like (PTP-like) in a network. The network slave node includes a packet detection unit for detecting whether the slave node receives or sends a synchronization protocol packet and recording a synchronization protocol packet receiving time and a synchronization protocol packet sending time; a hardware clock; and a control unit controlling the packet detection unit and the hardware clock. The control unit reads out the packet receiving time and the packet sending time from the packet detection unit and informs a local master node. The local master node calculates a time offset between the local master node and the slave node, and informs the control unit. The control unit adjusts the hardware clock based on the time offset so that the local master node and the slave node are time synchronized.

Owner:IND TECH RES INST

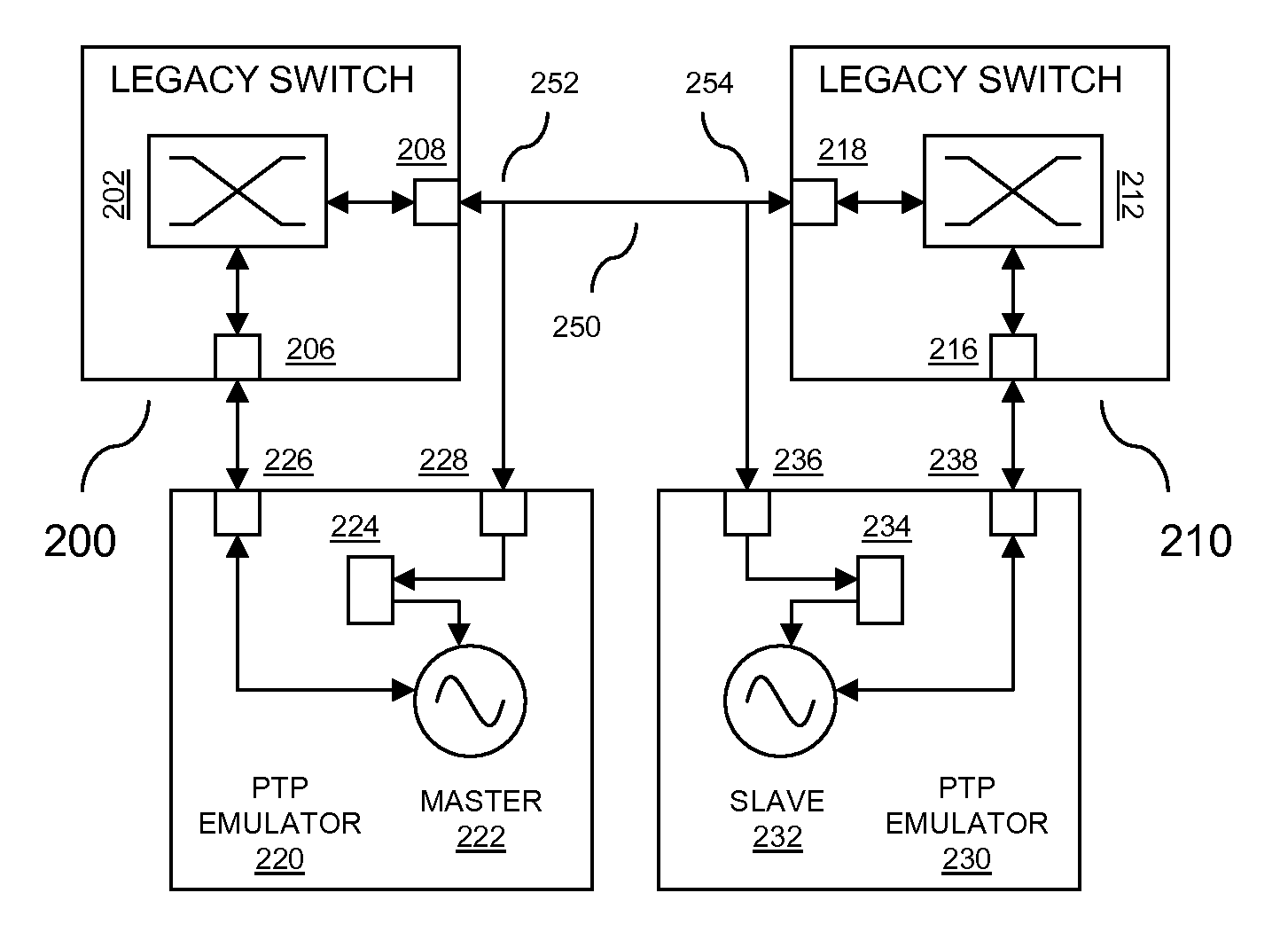

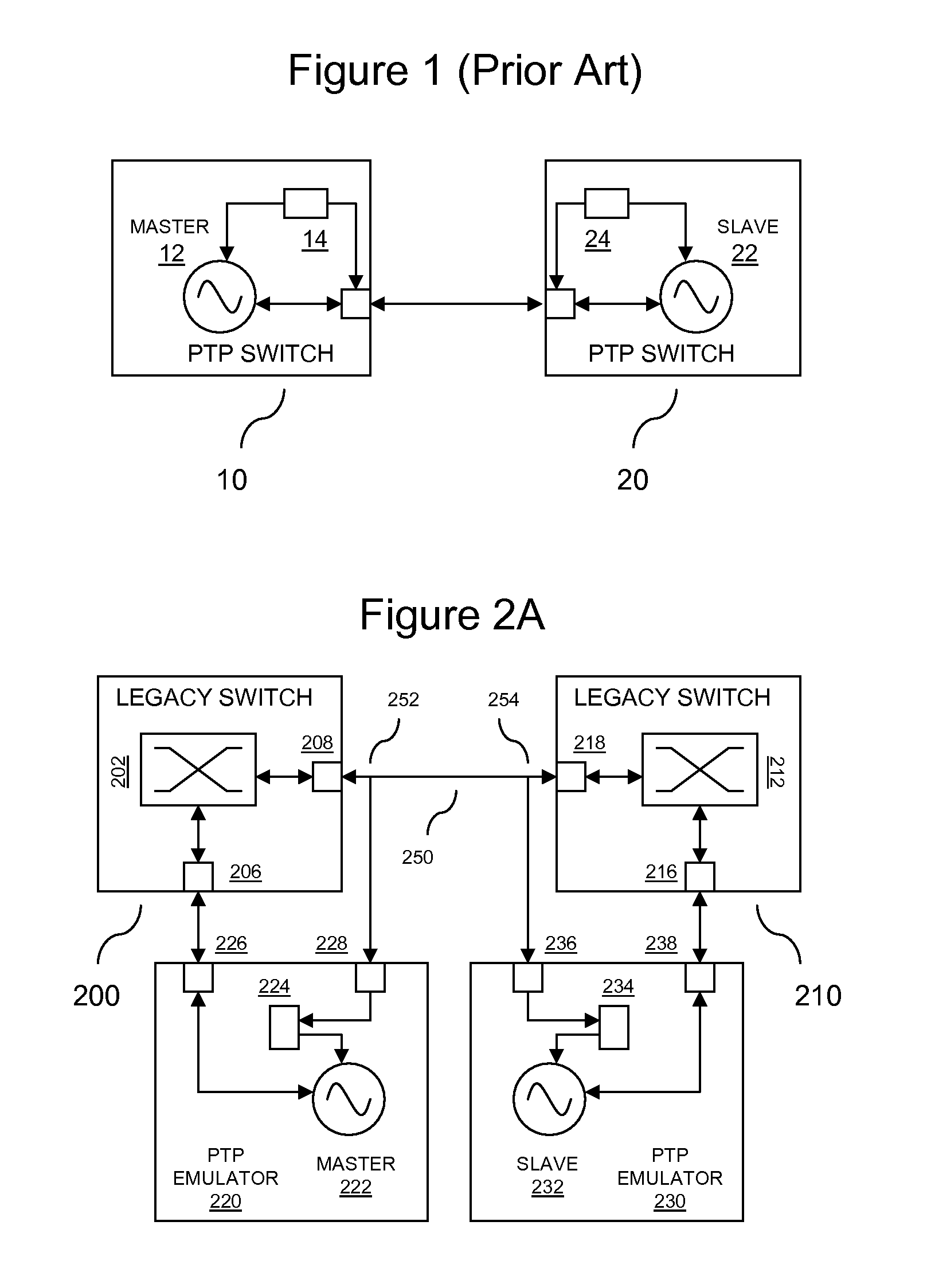

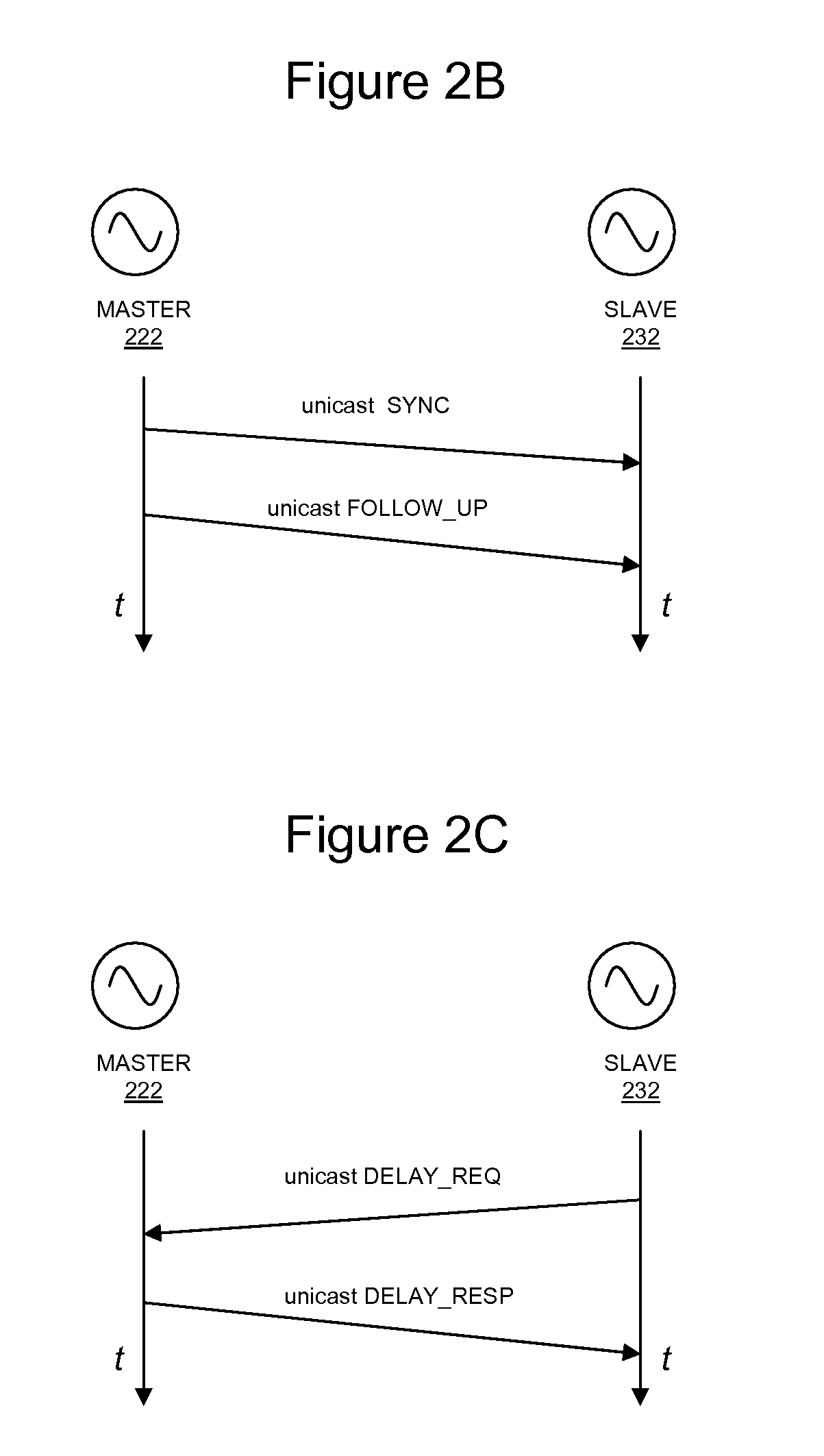

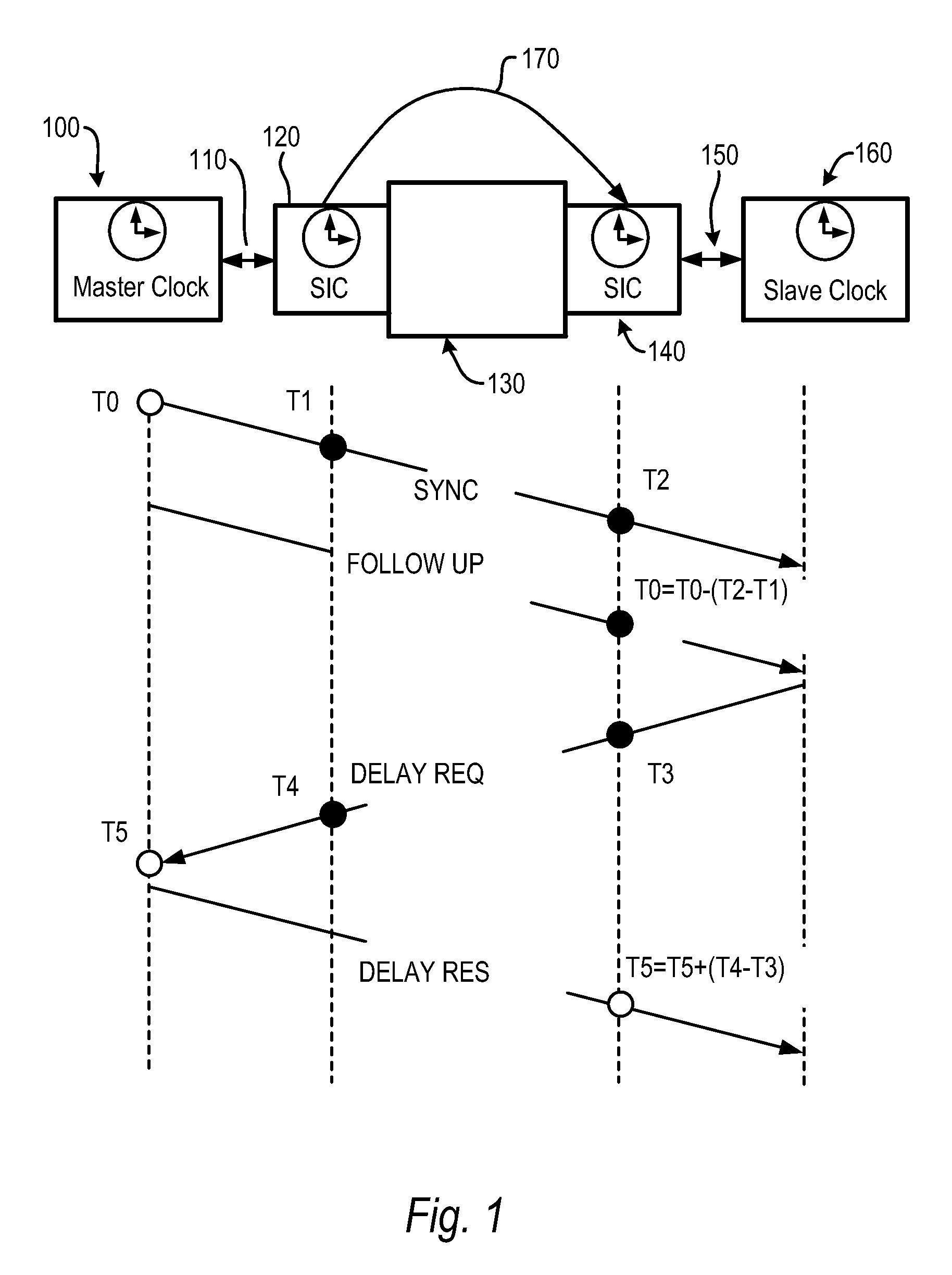

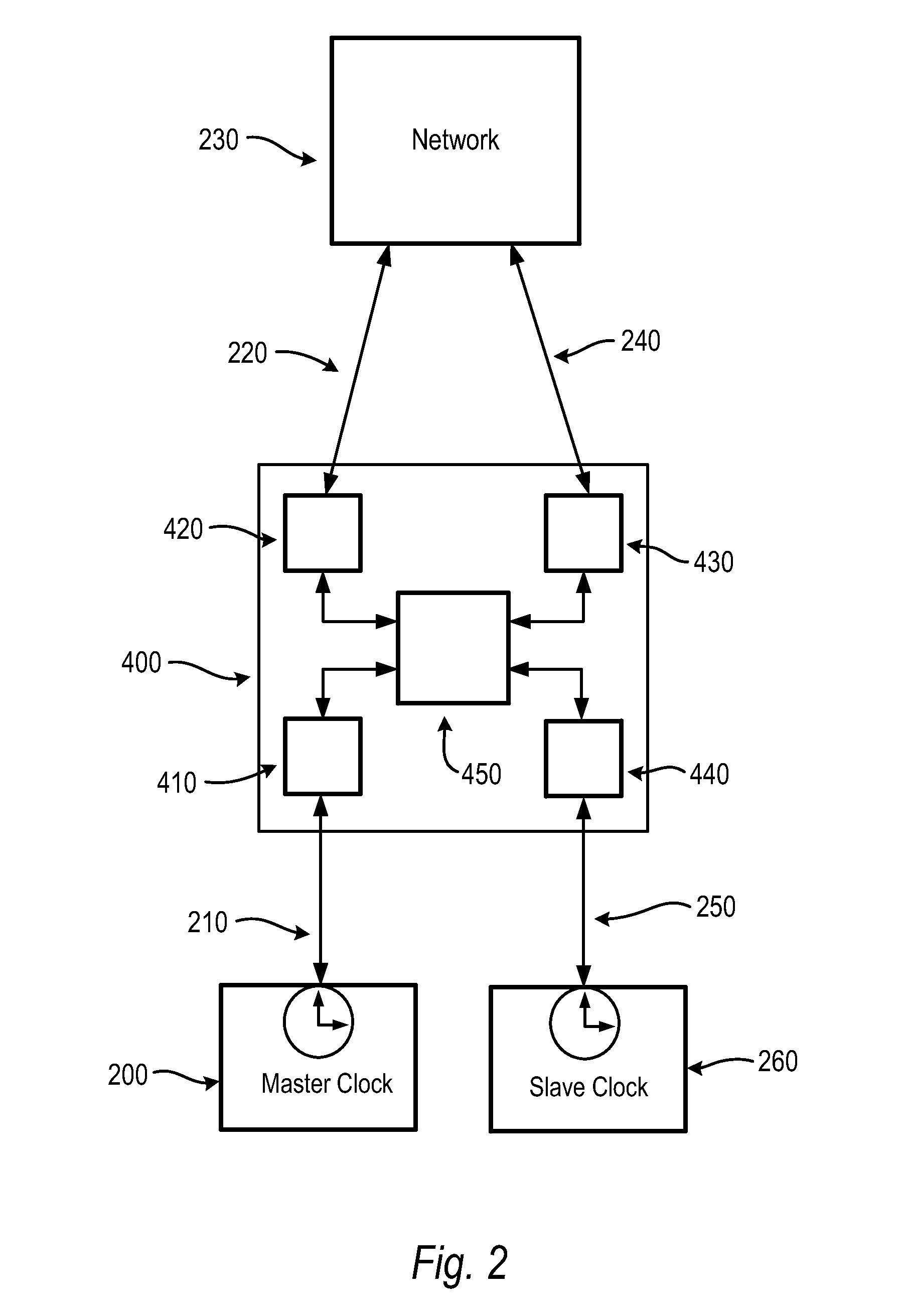

Precision Time Protocol Emulation for Network Supportive of Circuit Emulation Services

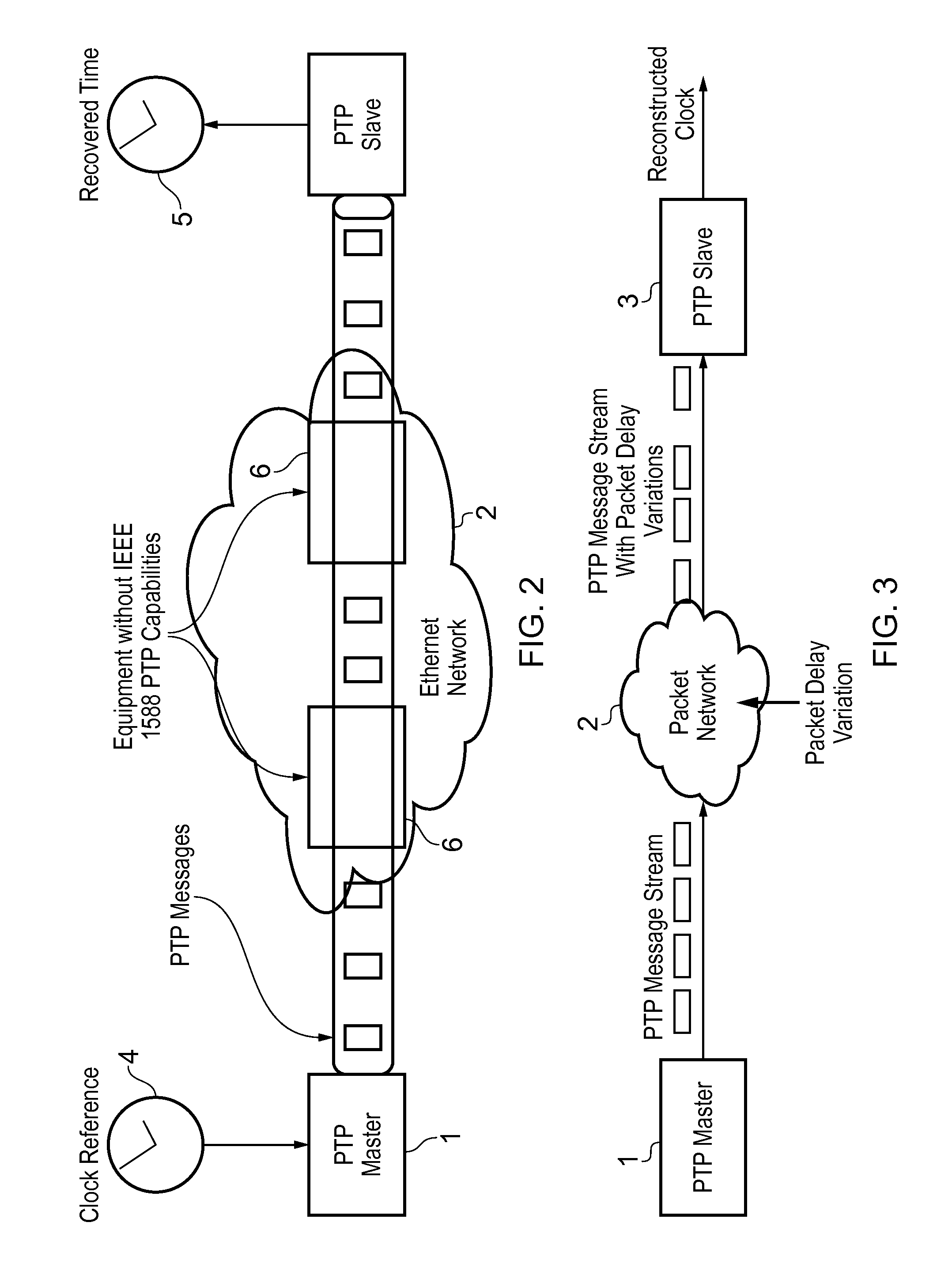

Precision Time Protocol (PTP) emulation service for a data communication network of a type that is adapted to support circuit emulation services (CES). The PTP emulation service enables seamless PTP-style clock synchronization over such a network using any combination of legacy switches, PTP boundary switches and PTP switches. The PTP emulation service is delivered through the expedient of external PTP emulation devices that are associated with legacy switches and PTP boundary switches.

Owner:ALCATEL LUCENT SAS

Methods and devices for clock synchronization

ActiveUS20140064303A1Time-division multiplexSynchronisation signal speed/phase controlPrecision Time ProtocolTime Protocol

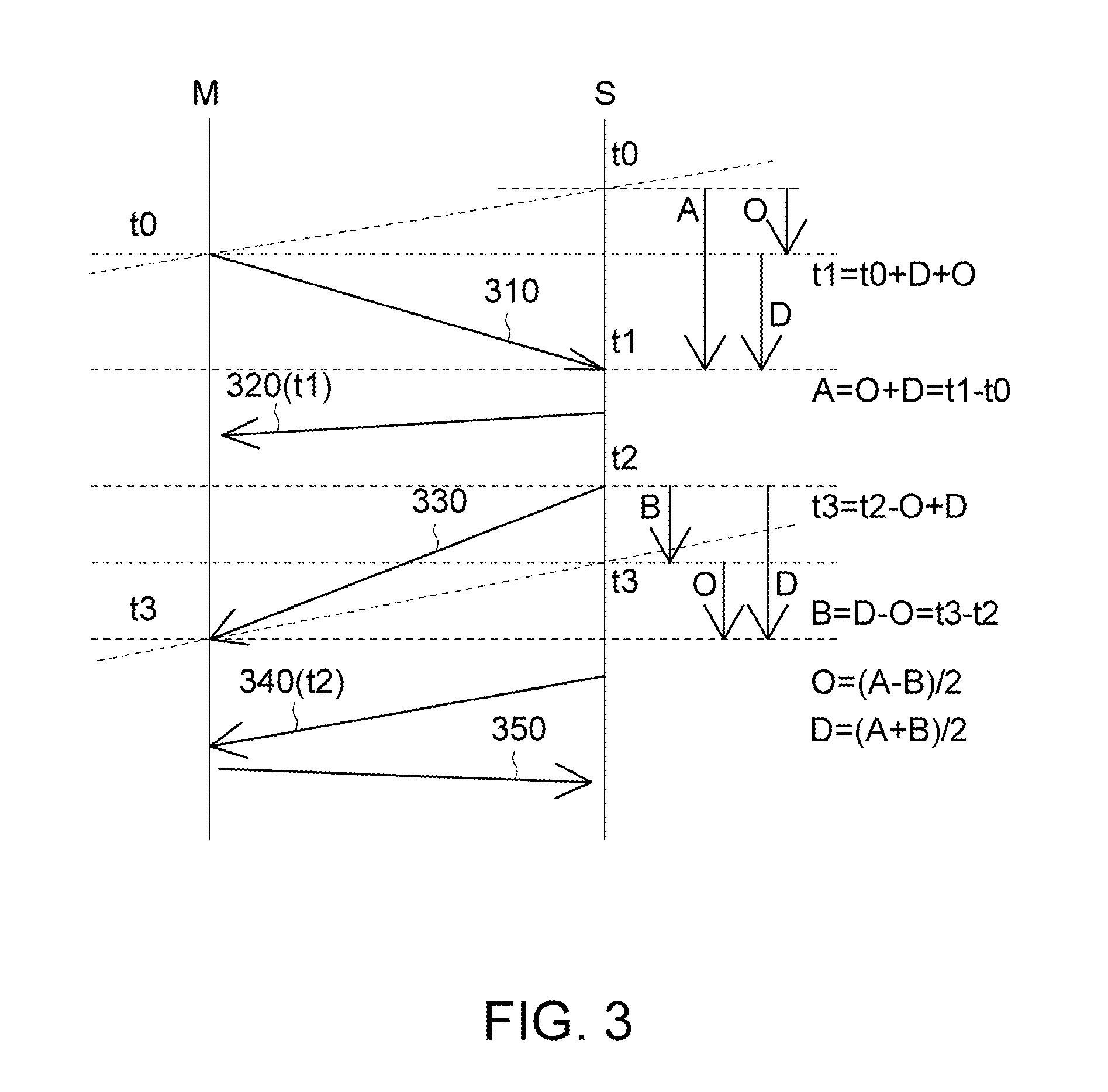

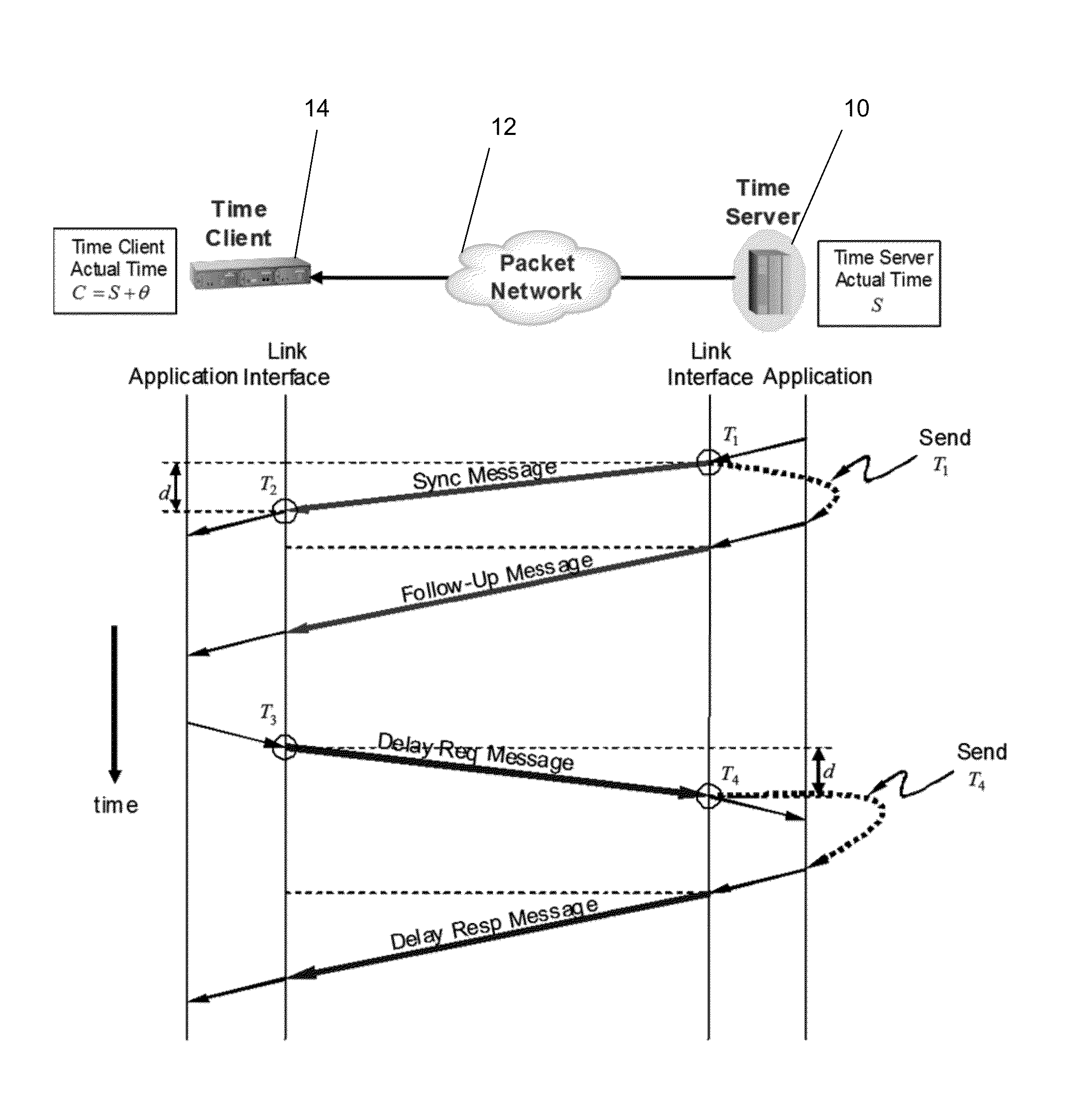

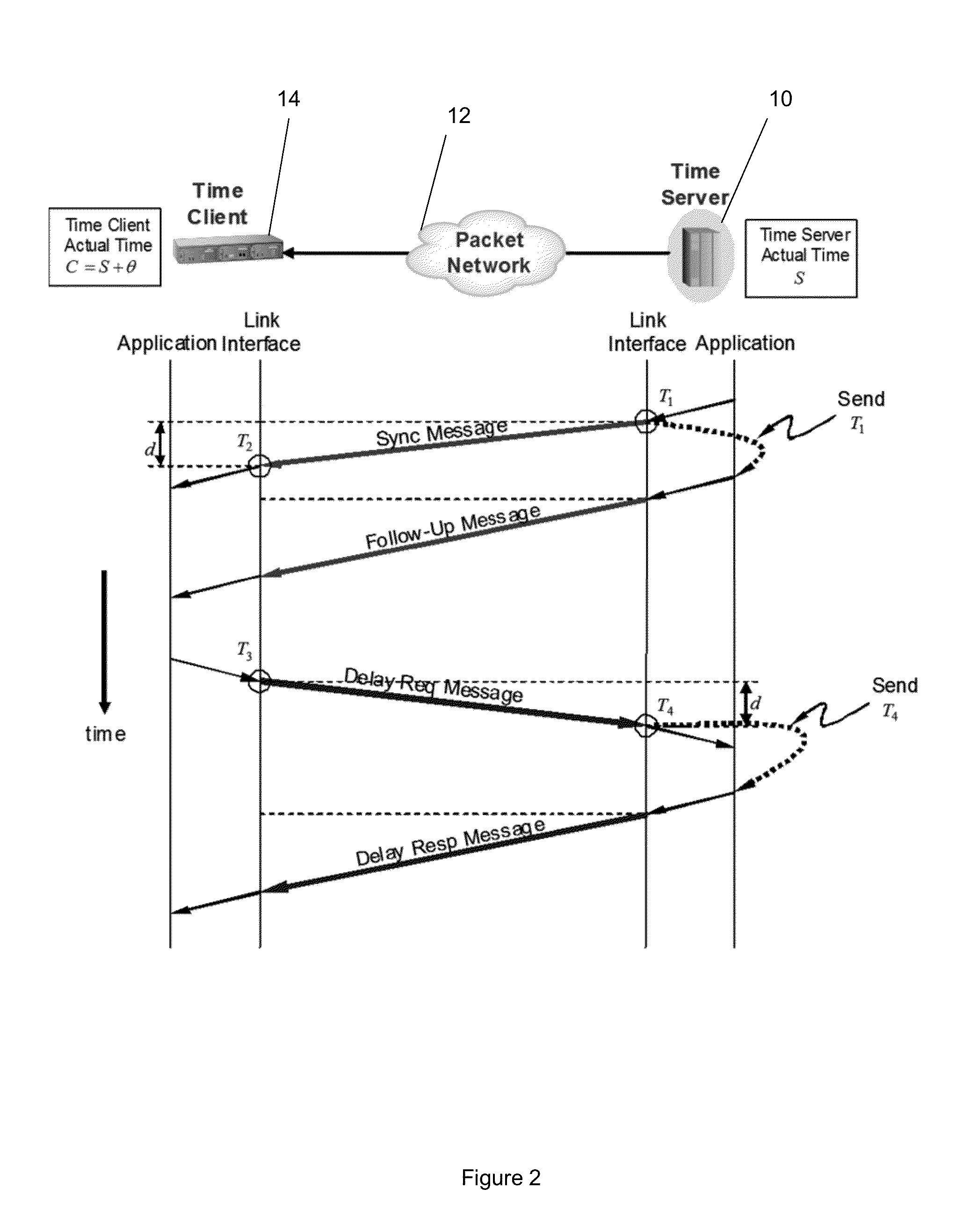

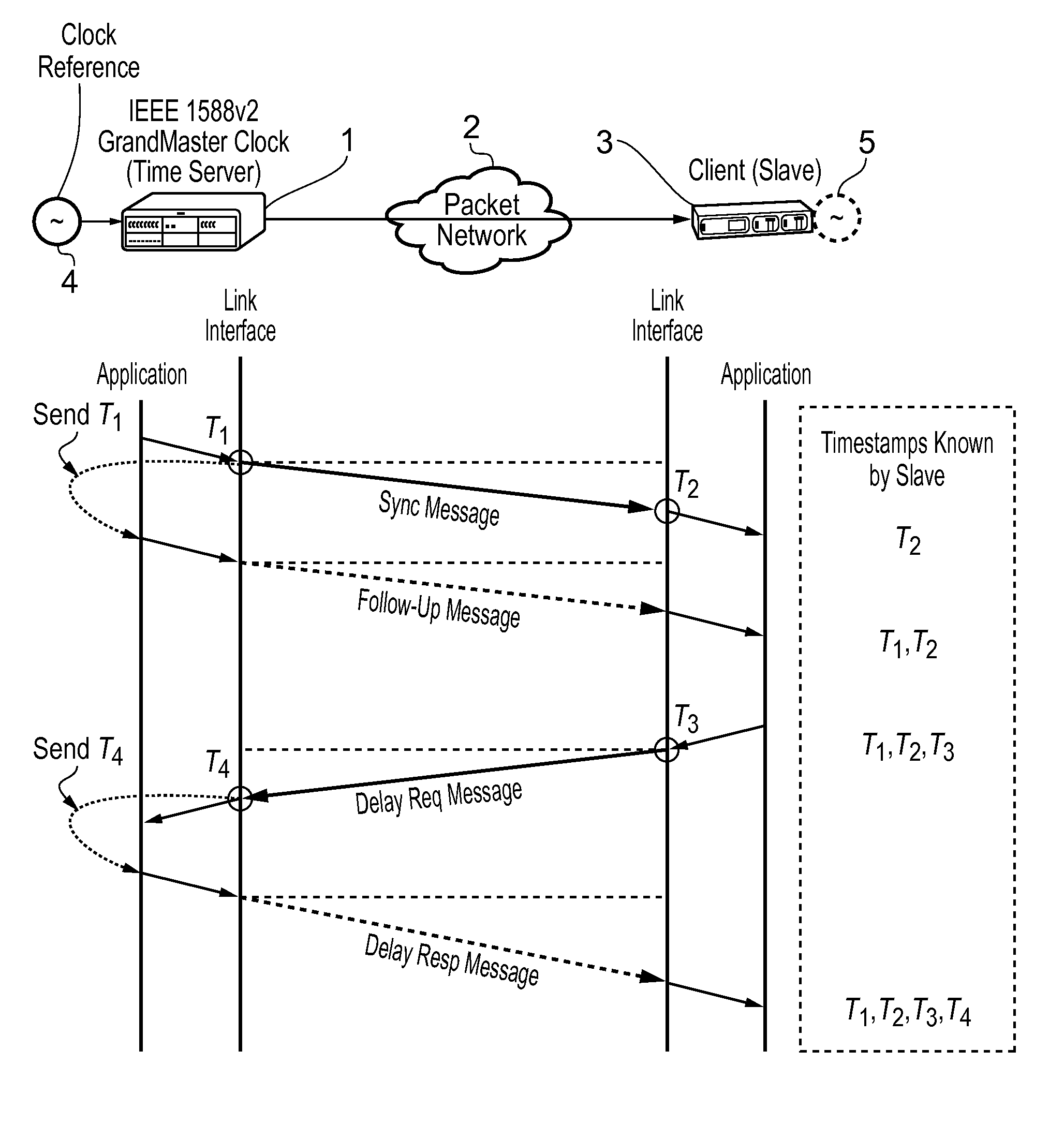

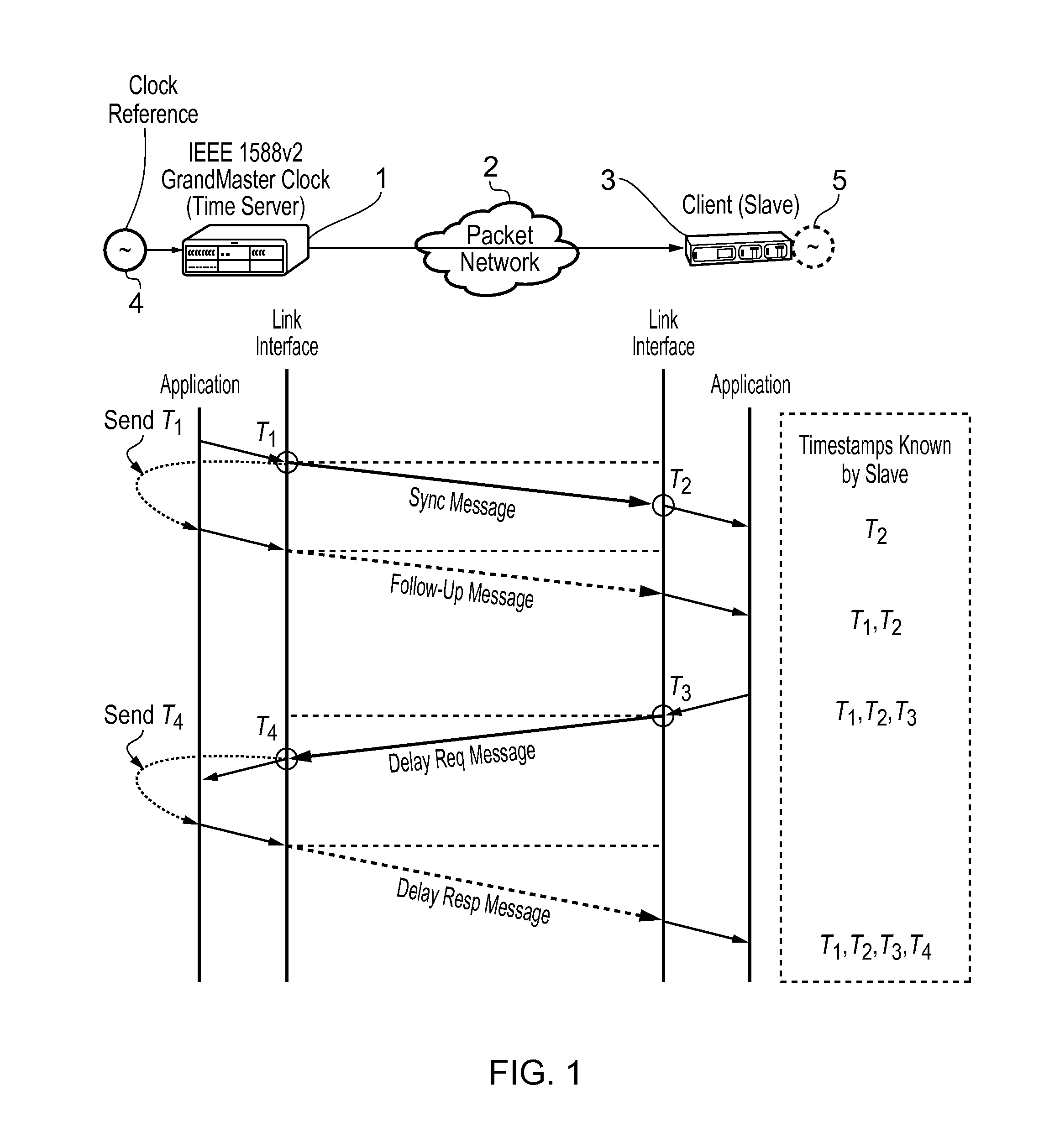

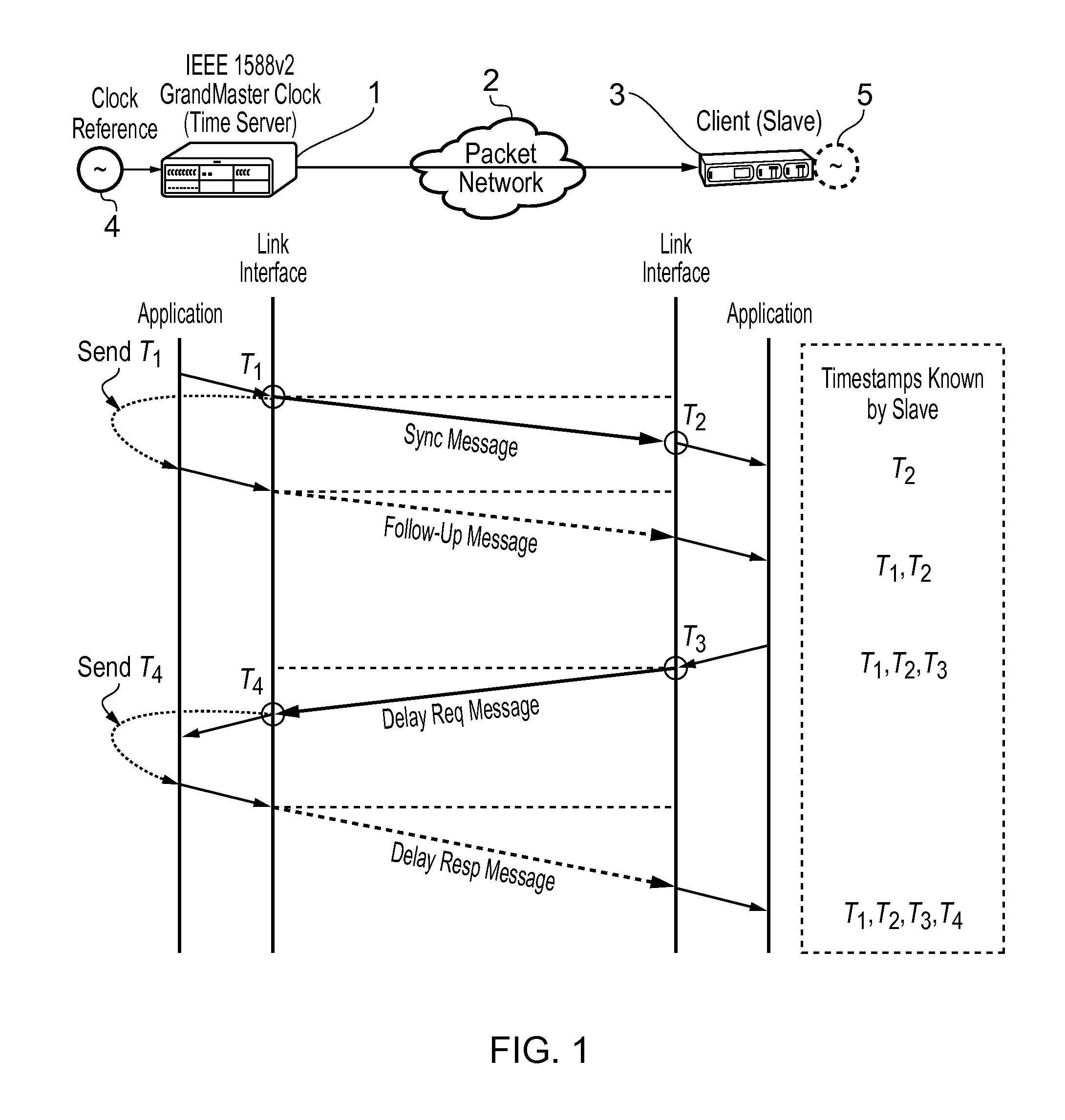

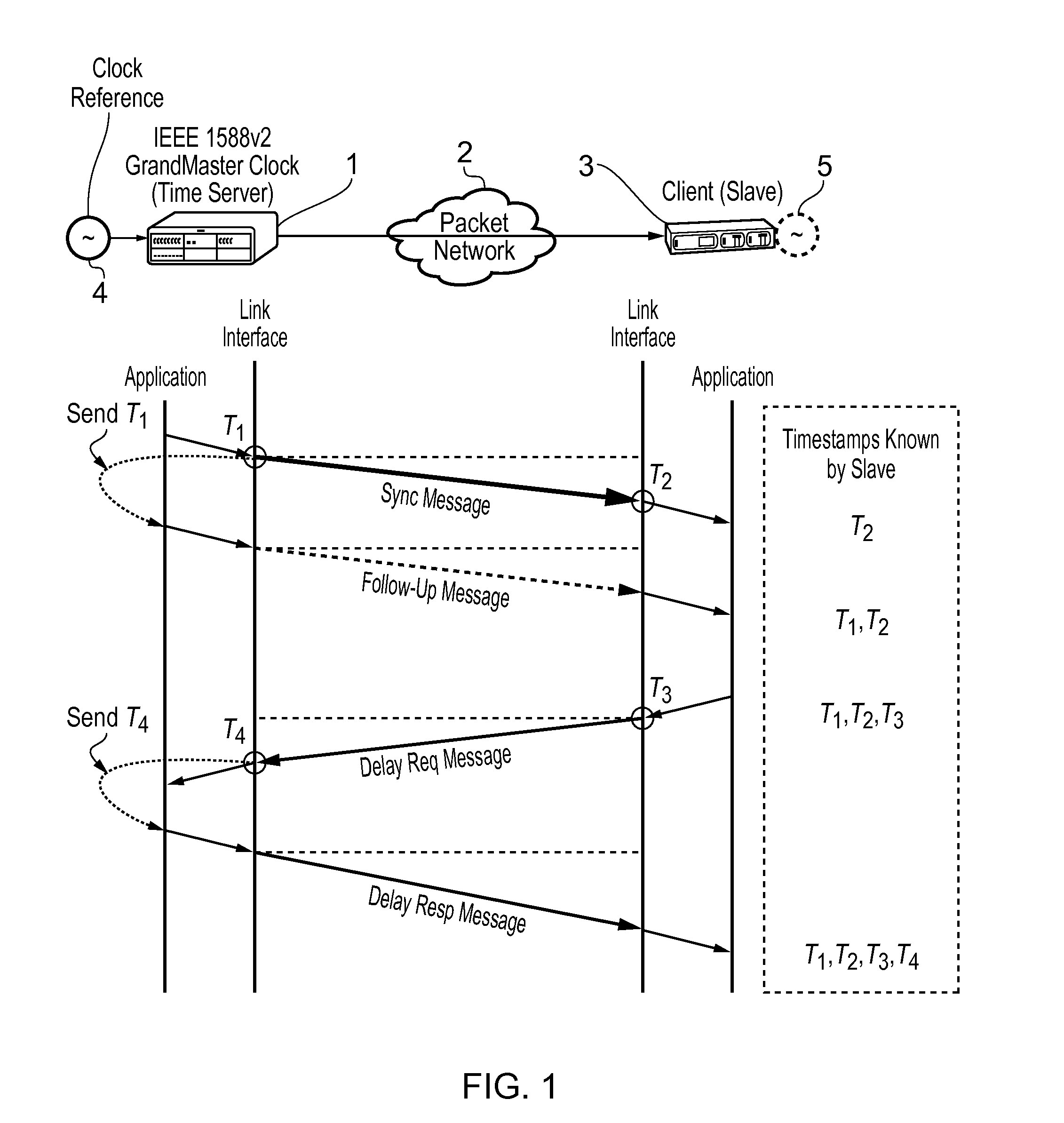

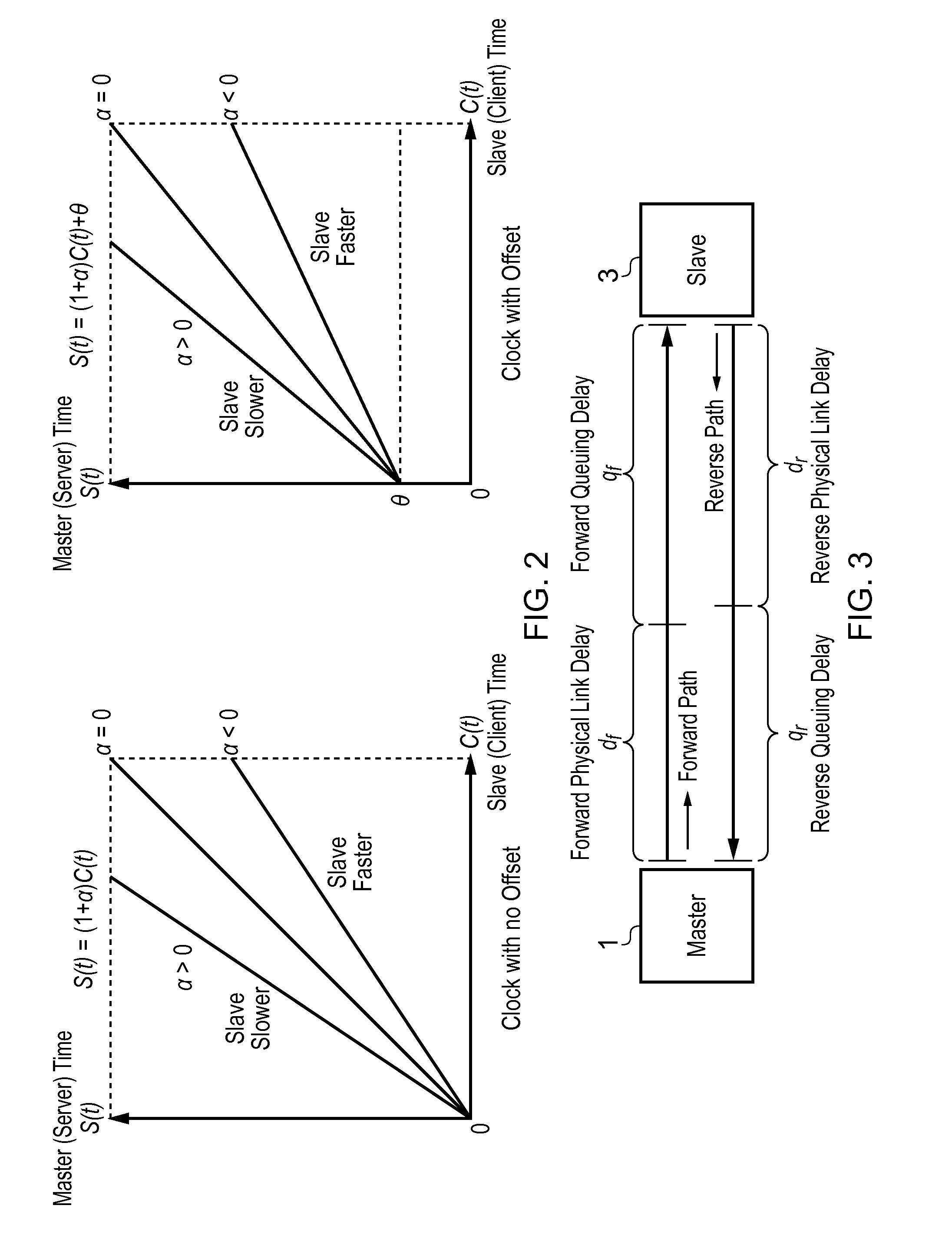

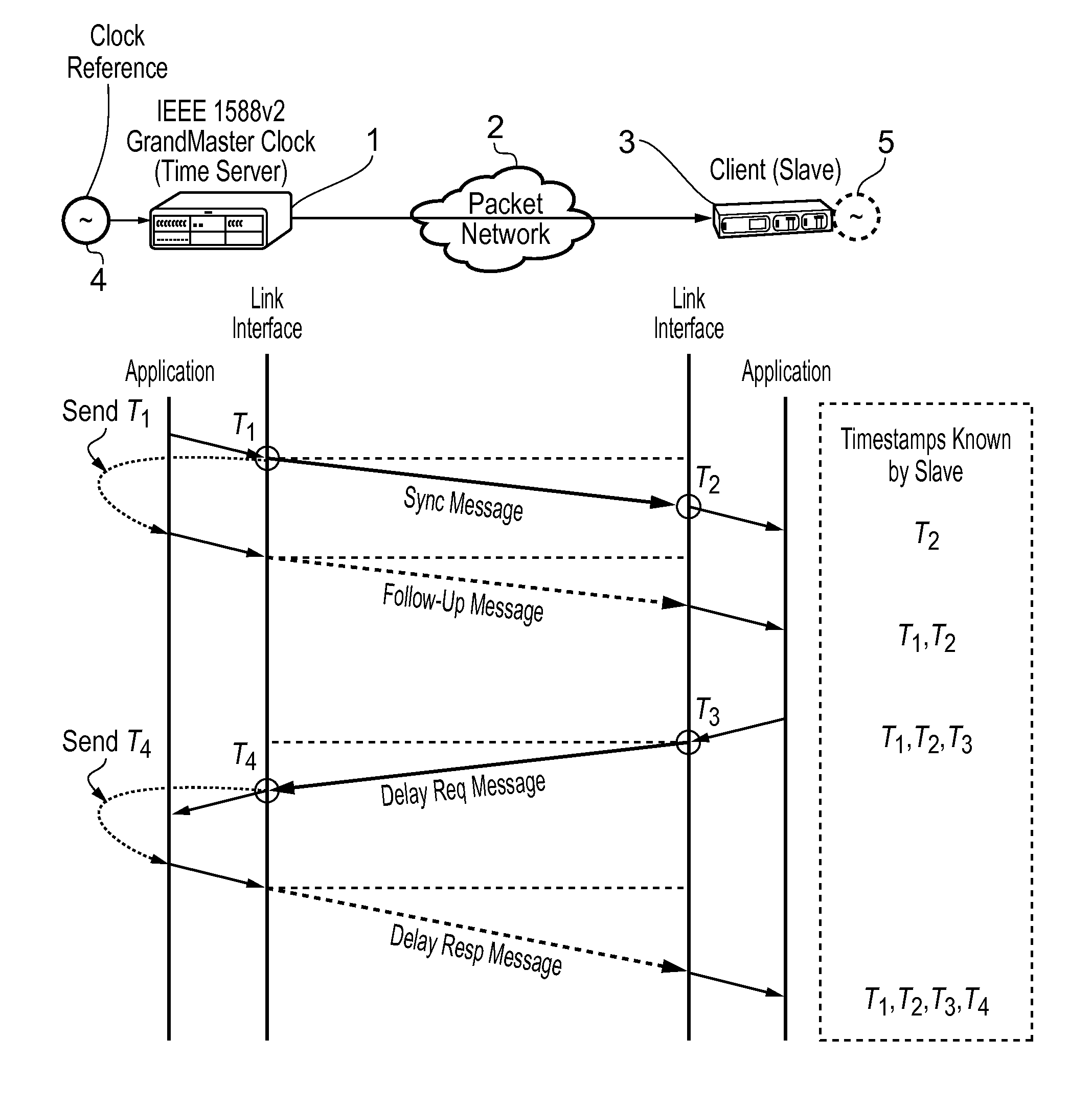

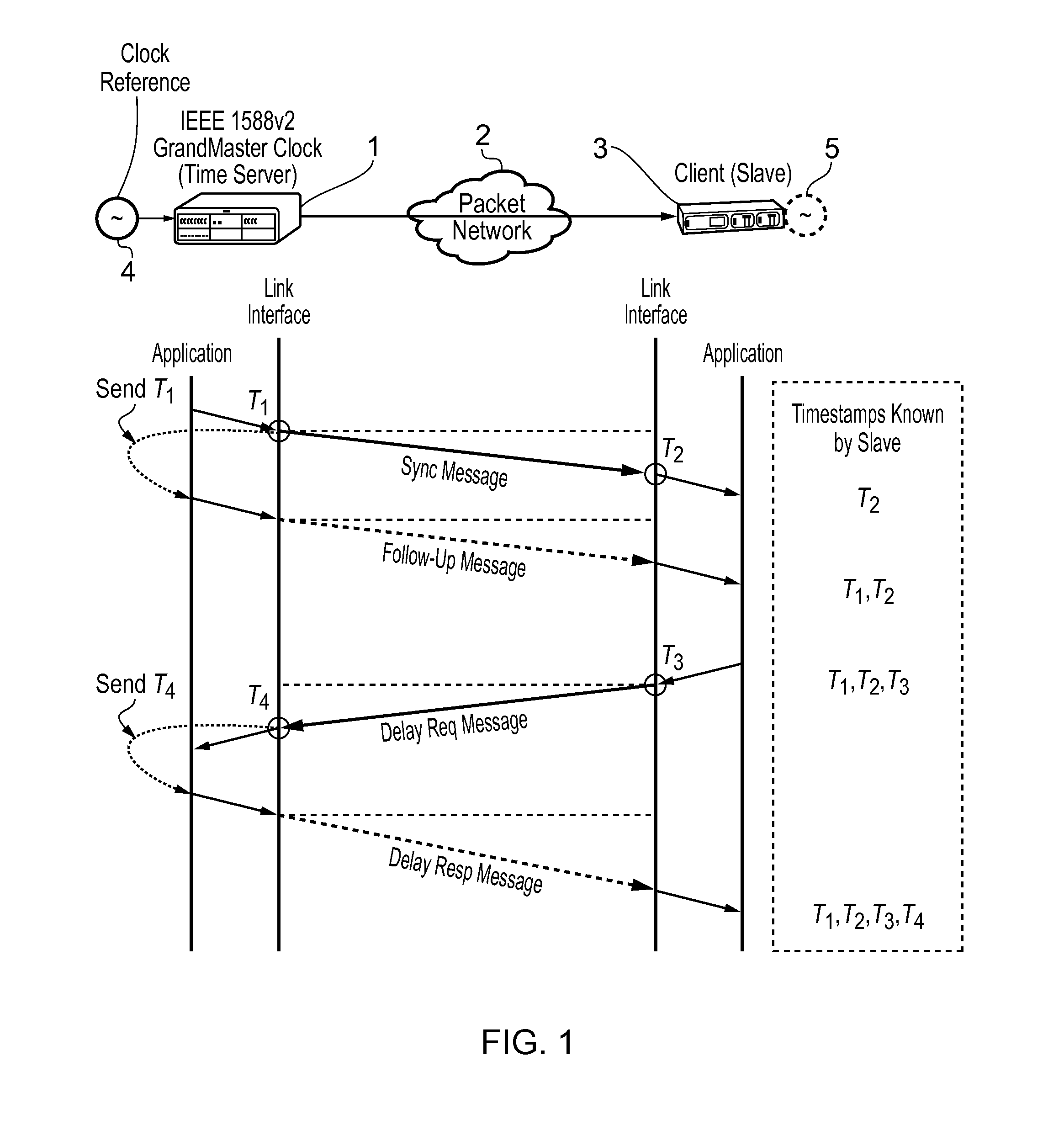

This invention relates to methods and devices for clock synchronization. The invention makes particular use of IEEE 1588 with offset and skew correction. In embodiments of the invention, the IEEE 1588 Precision Time Protocol is used to exchange time stamps between a time server and a client from which the client can estimate the clock offset and skew. In embodiments of the invention a free running clock at the client is provided with an estimation technique based on the time stamps from the IEEE 1588 PTP message exchange between the server and client clocks. The offset and skew from the estimation process can be combined with the local free running clock to give a synchronized local clock which is an accurate image of the master clock.

Owner:KHALIFA UNIV OF SCI & TECH +2

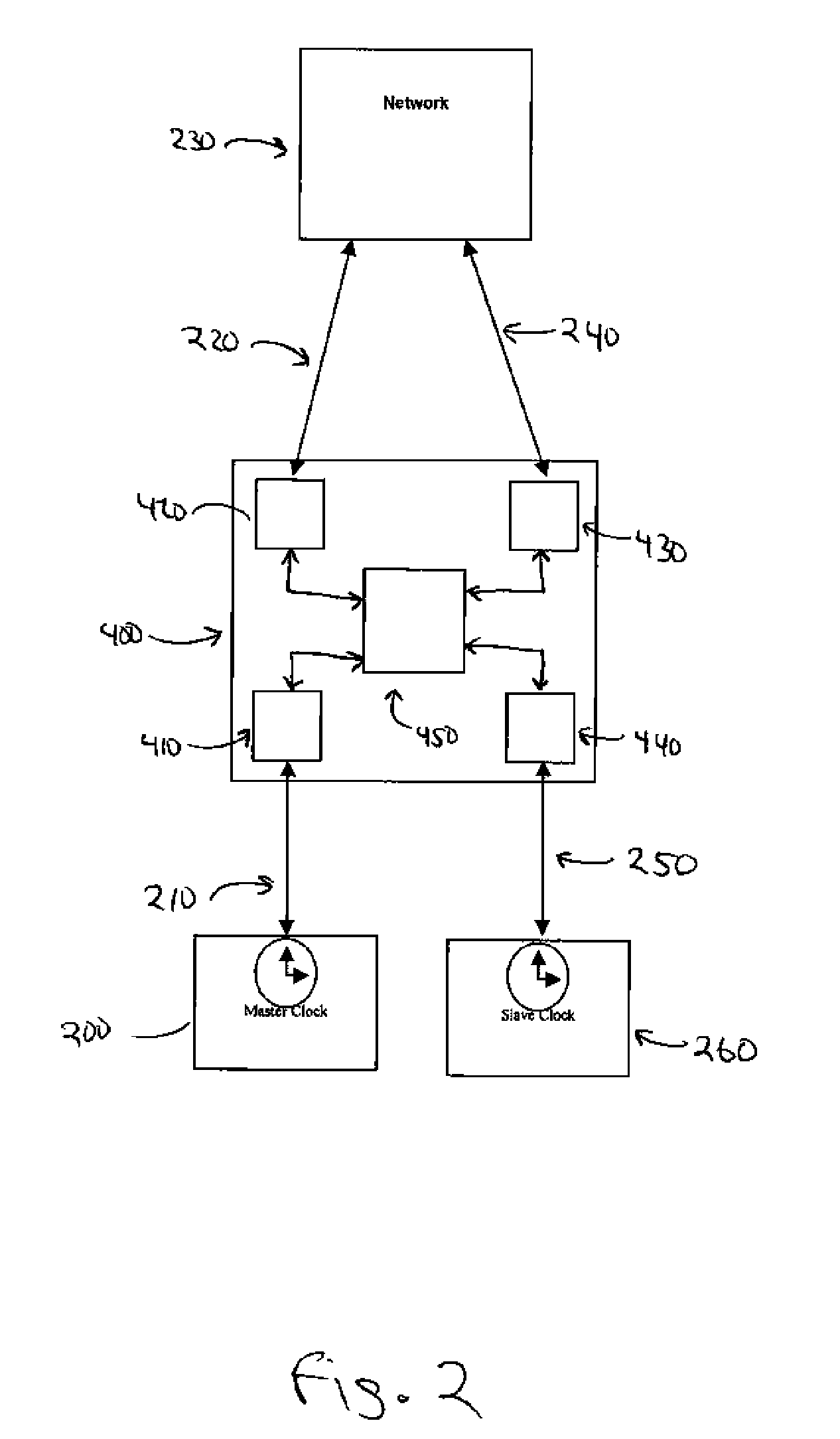

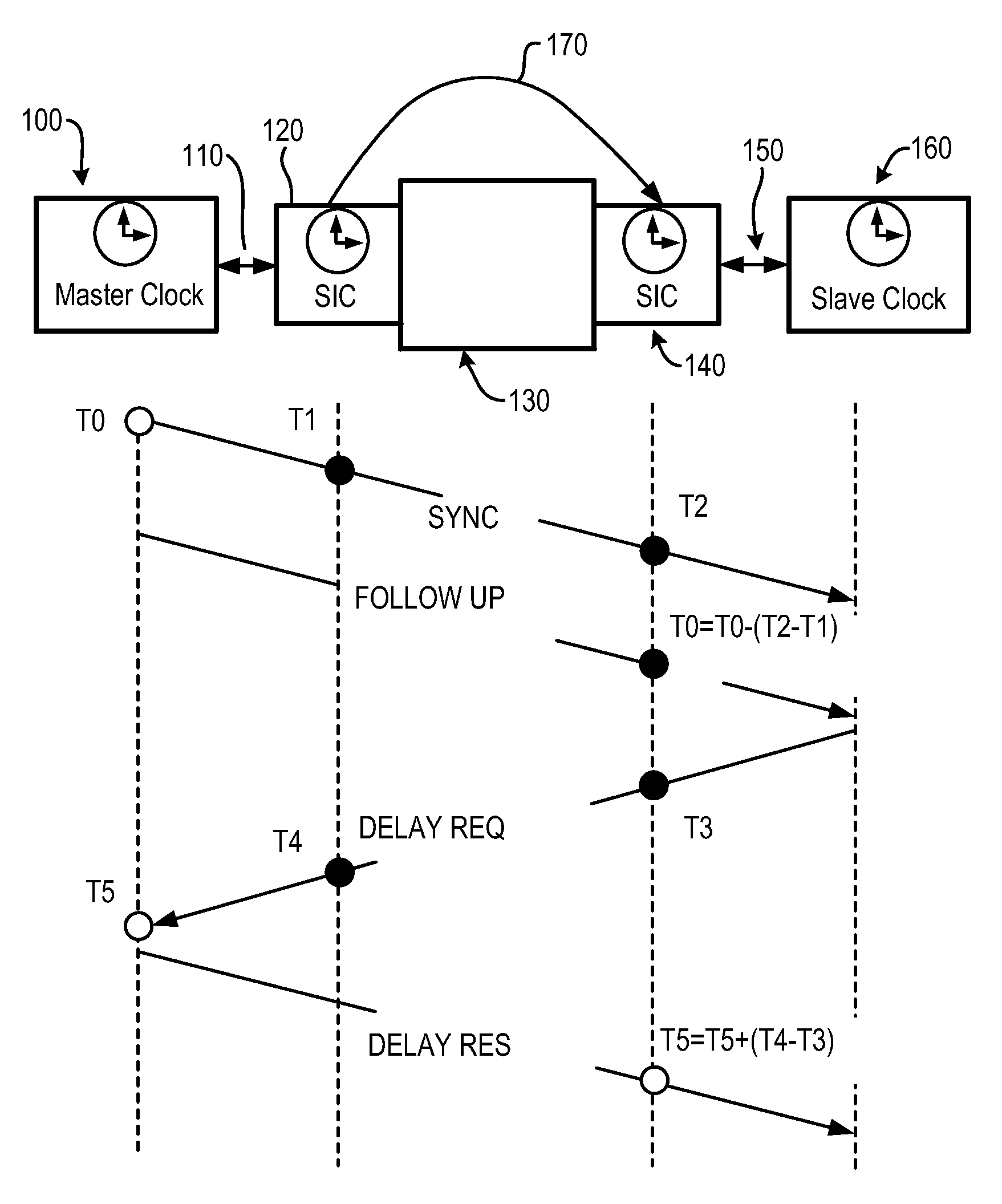

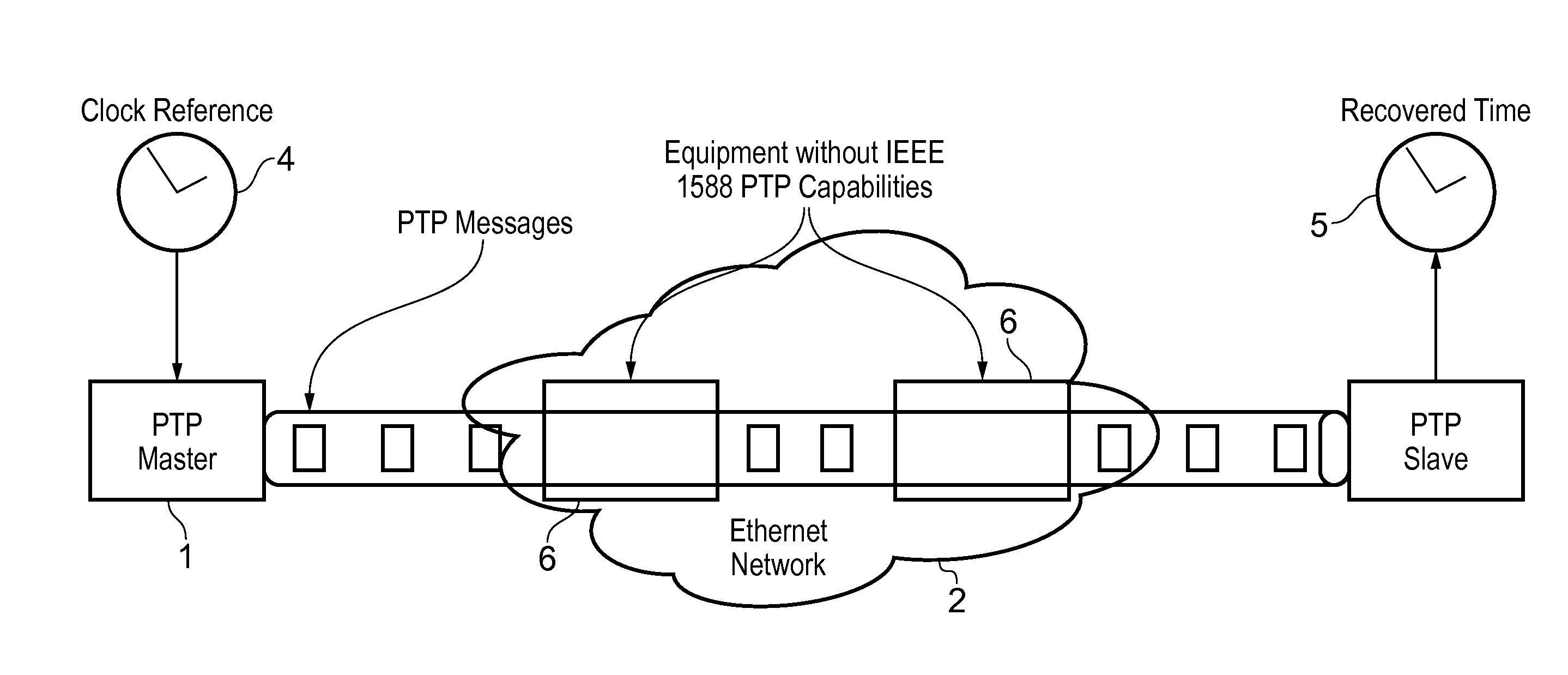

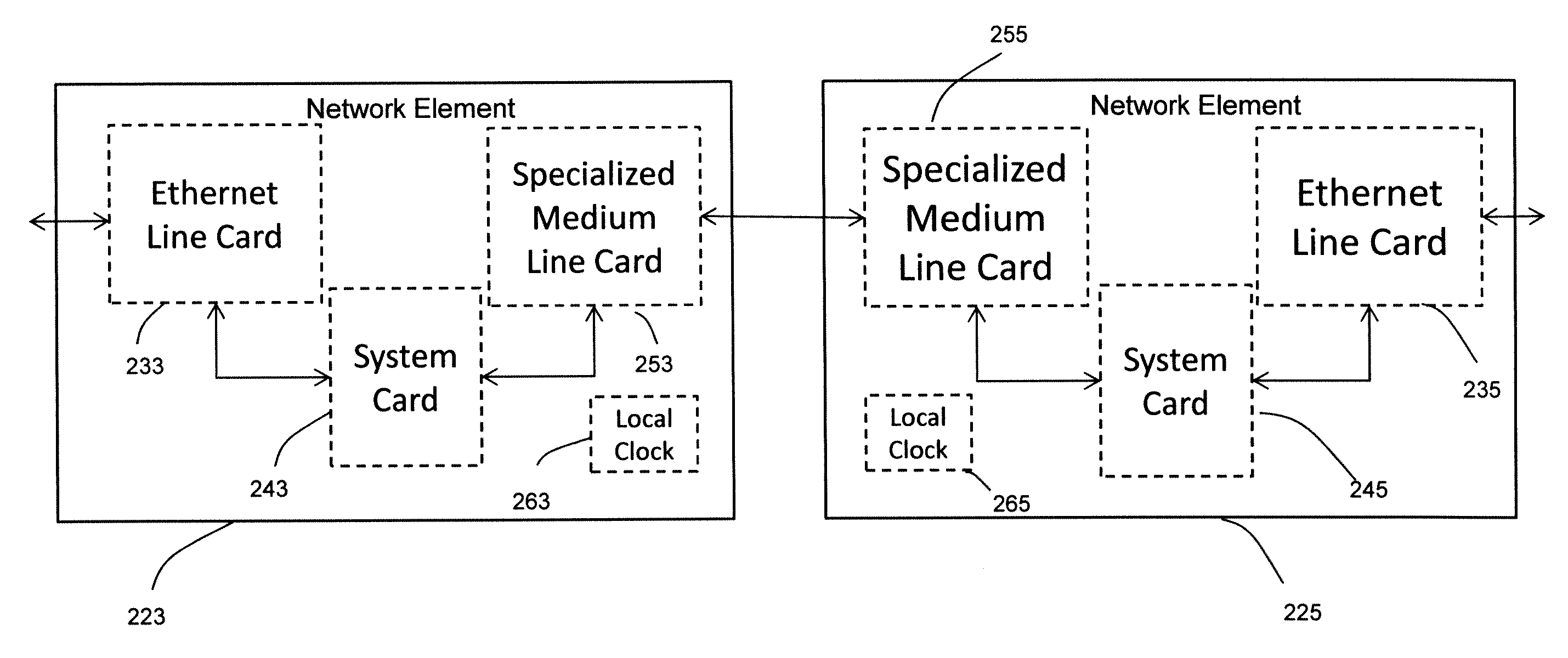

Mechanism For Making Delay From Network Elements Transparent To IEEE 1588 Protocols

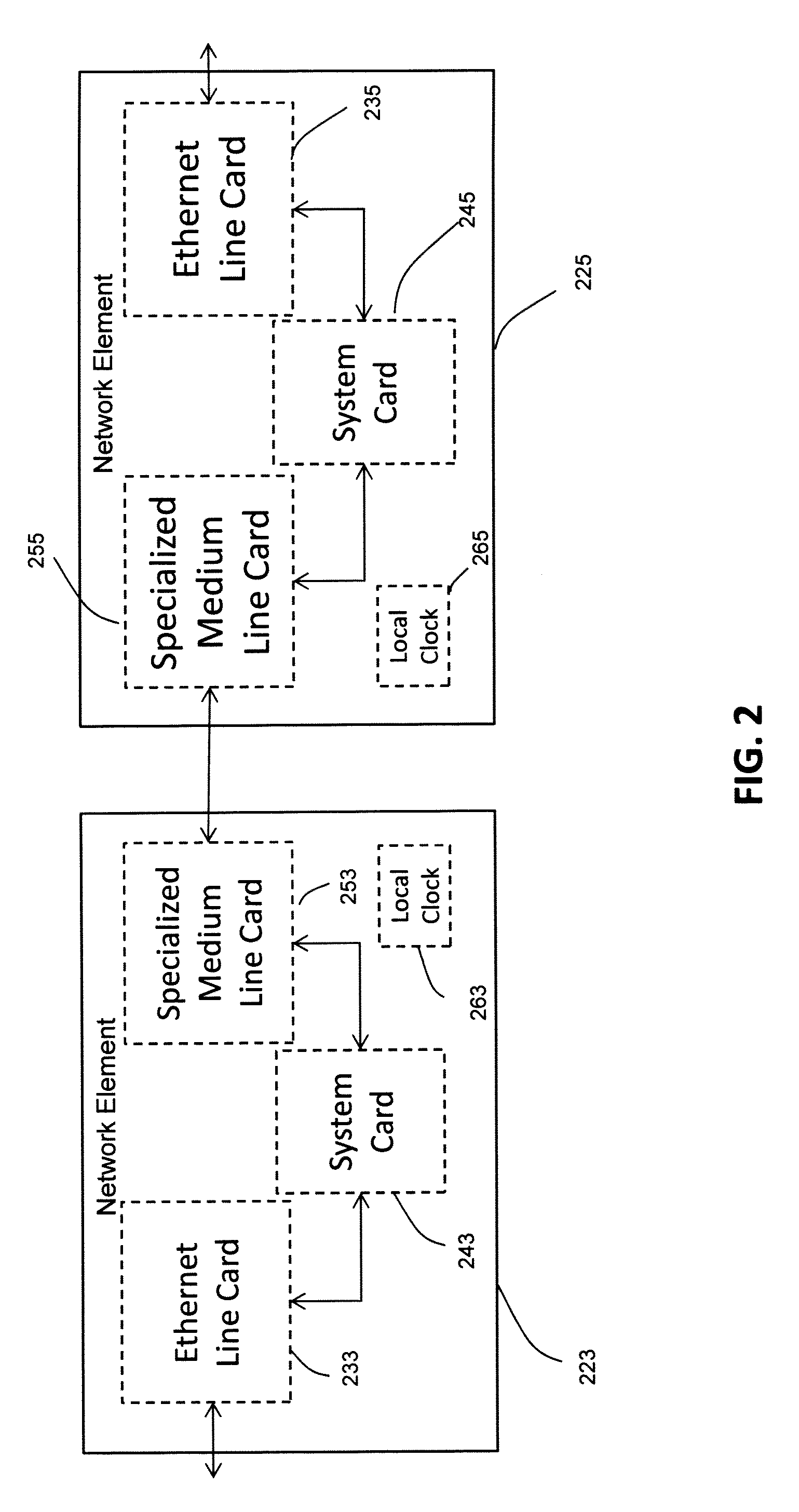

ActiveUS20080075217A1Time-division multiplexGenerating/distributing signalsComputer hardwareTime Protocol

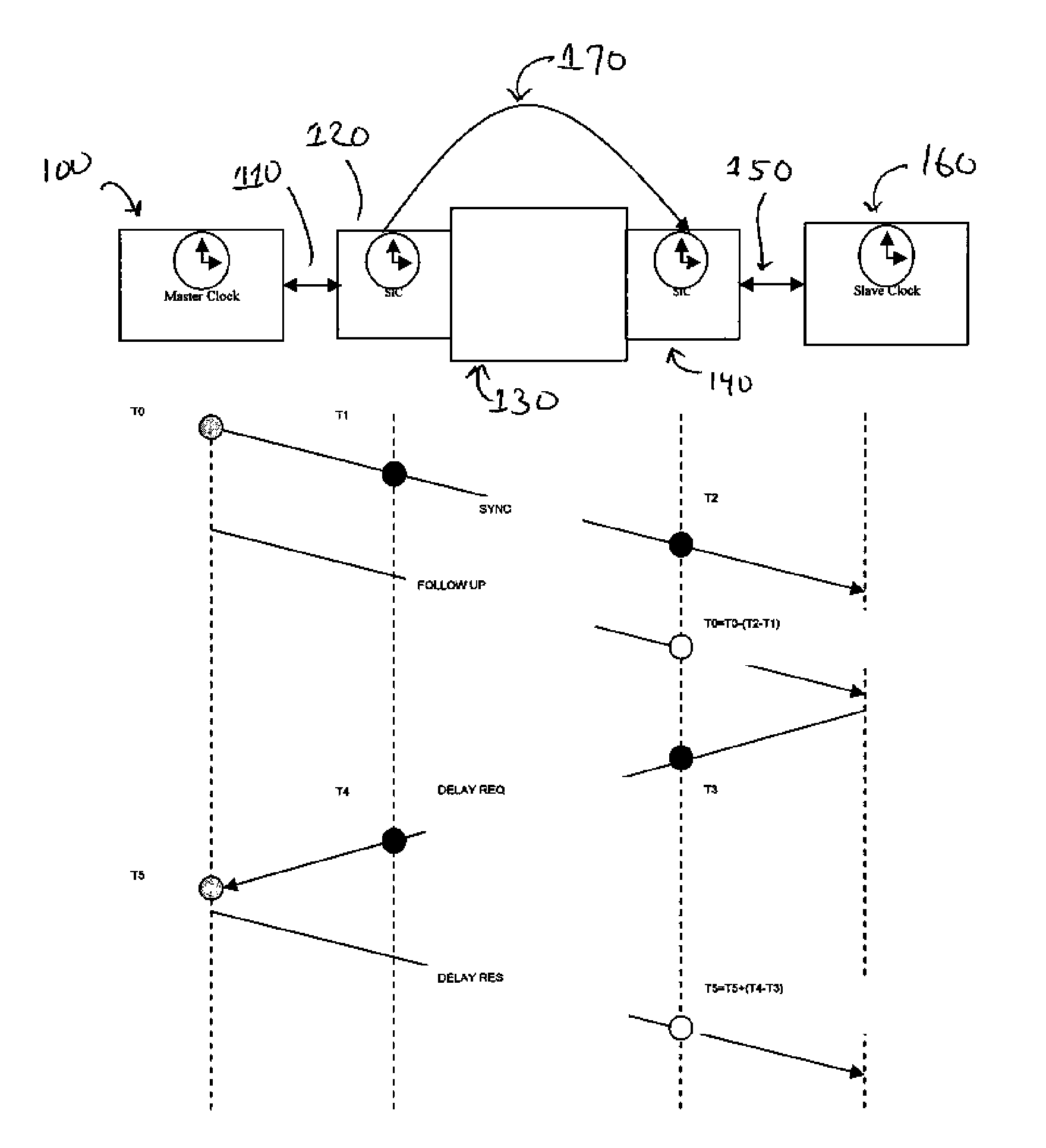

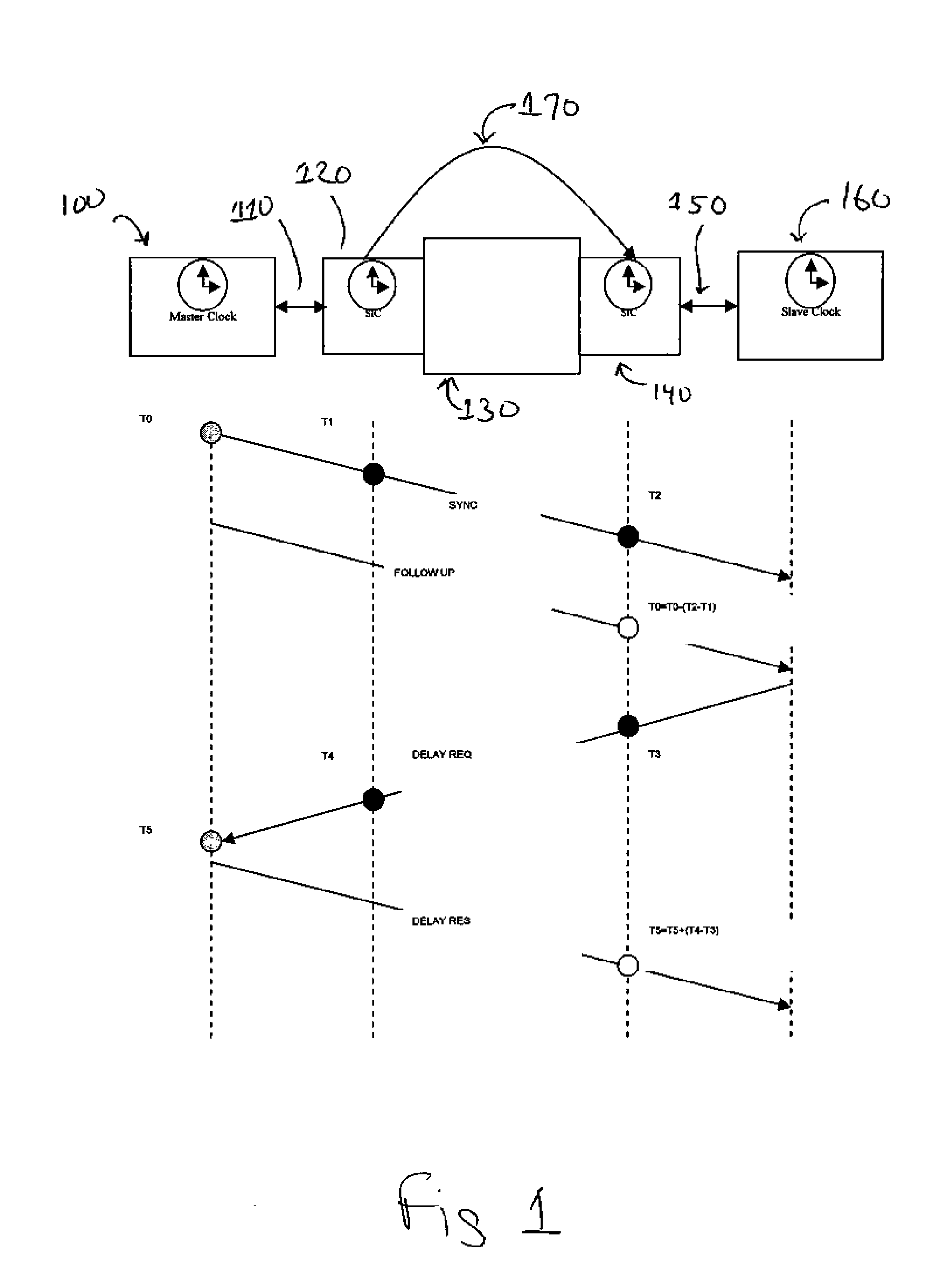

Apparatus for making legacy network elements transparent to IEEE 1588 Precision Time Protocol operation. Network elements are wrapped by device(s) capable of providing either transparent clock or boundary clock operation. In one embodiment, smart interface converters are used to provide transparent clock or boundary clock operation. The smart interface converters work cooperatively.

Owner:VIAVI SOLUTIONS INC

Method and apparatus for establishing IEEE 1588 clock synchronization across a network element comprising first and second cooperating smart interface converters wrapping the network element

ActiveUS7689854B2Time-division multiplexGenerating/distributing signalsComputer hardwareComputer science

Owner:VIAVI SOLUTIONS INC

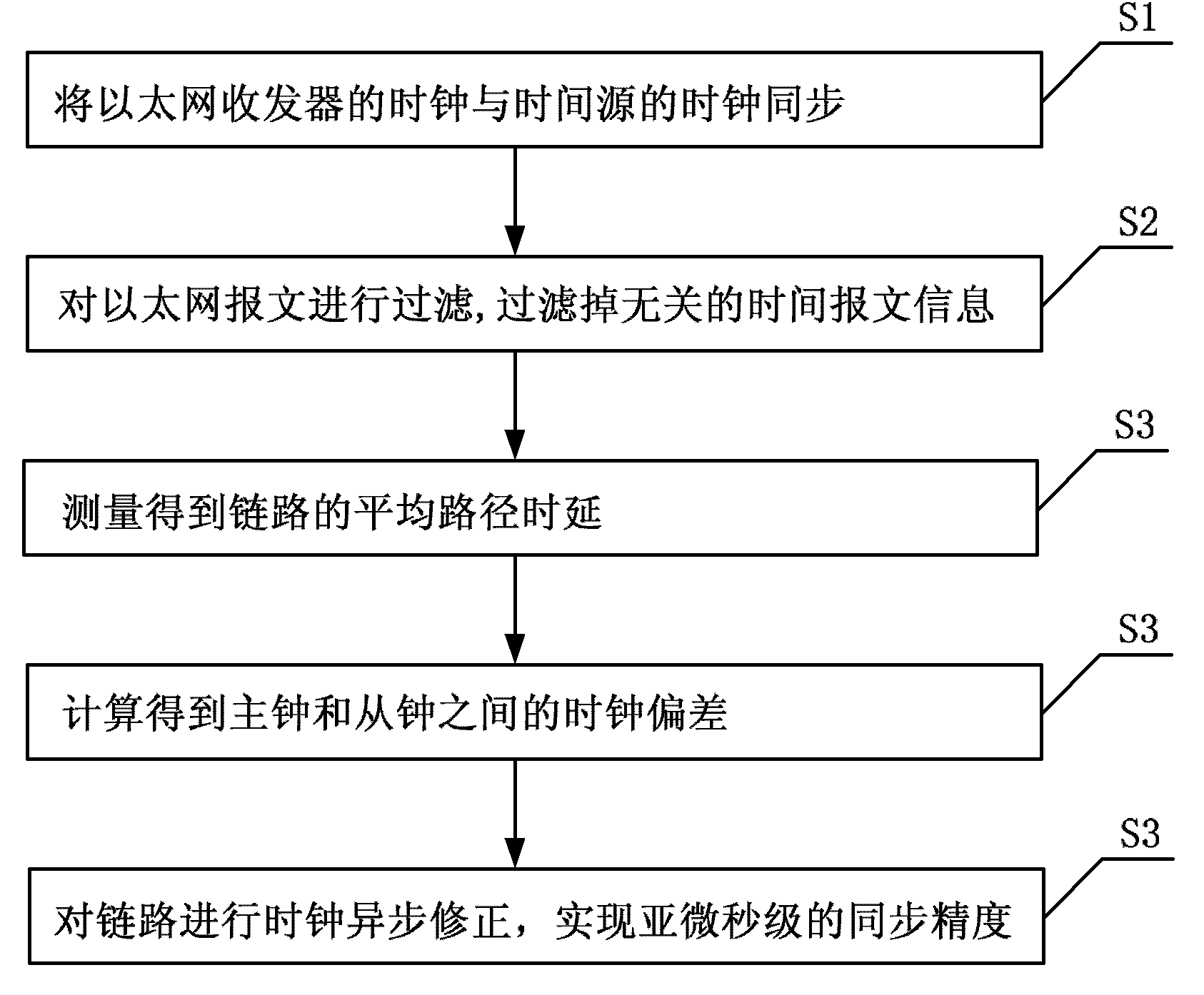

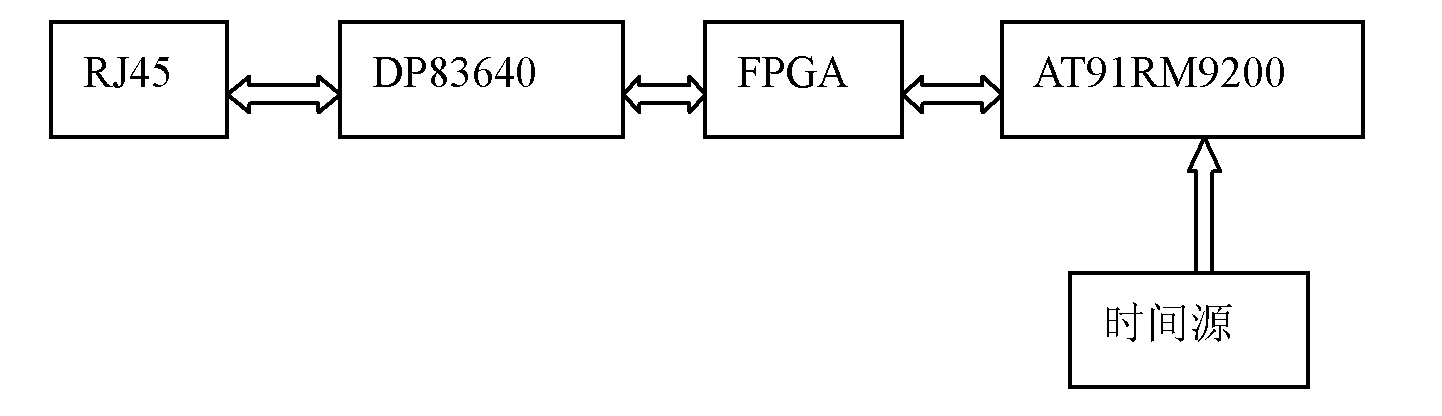

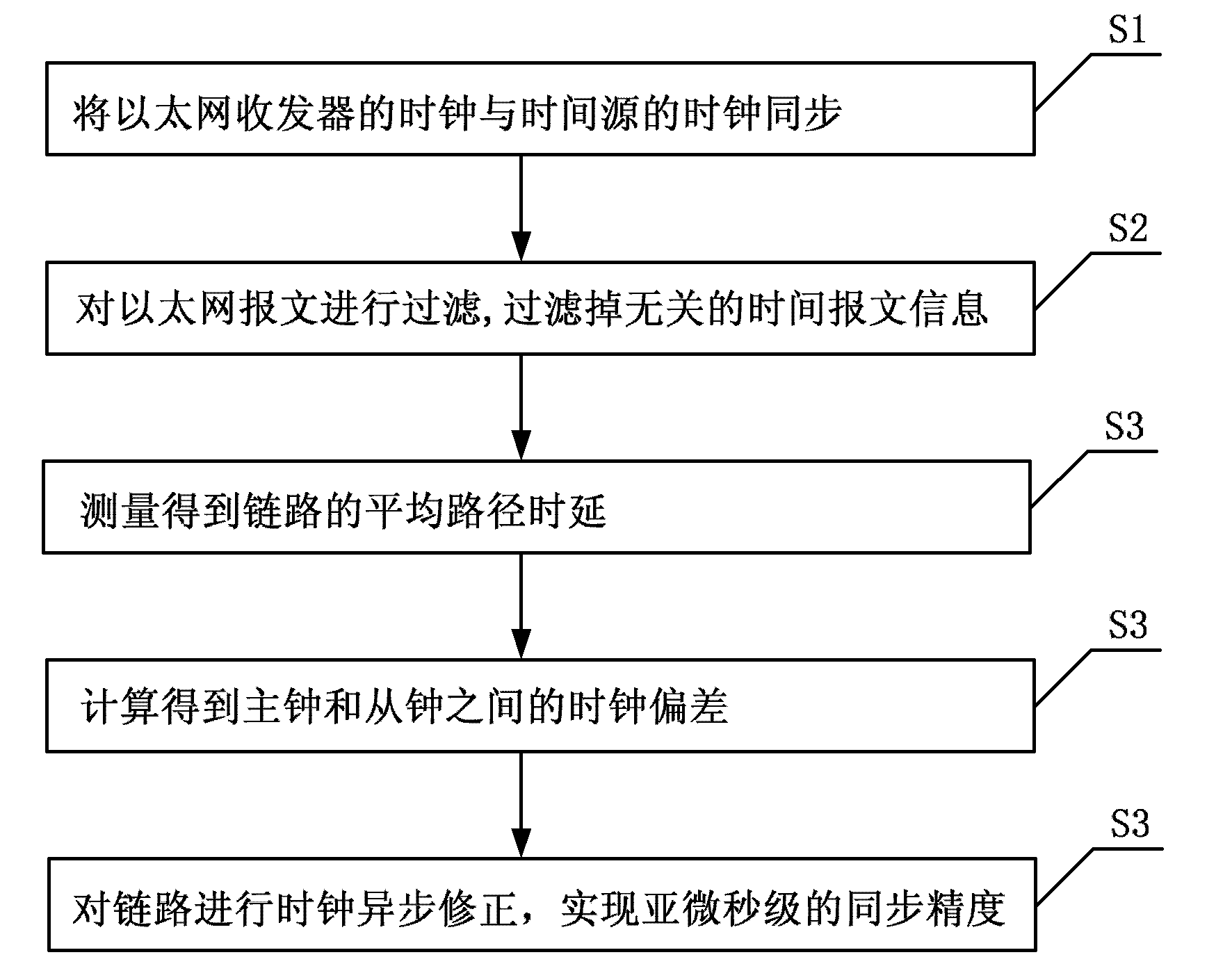

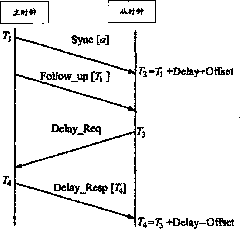

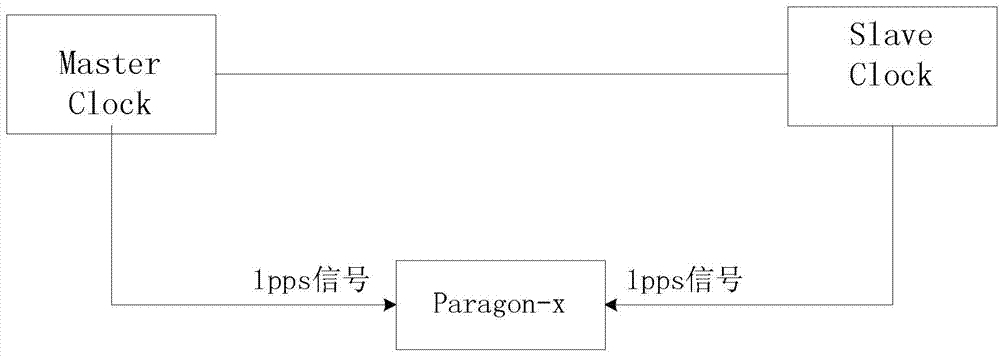

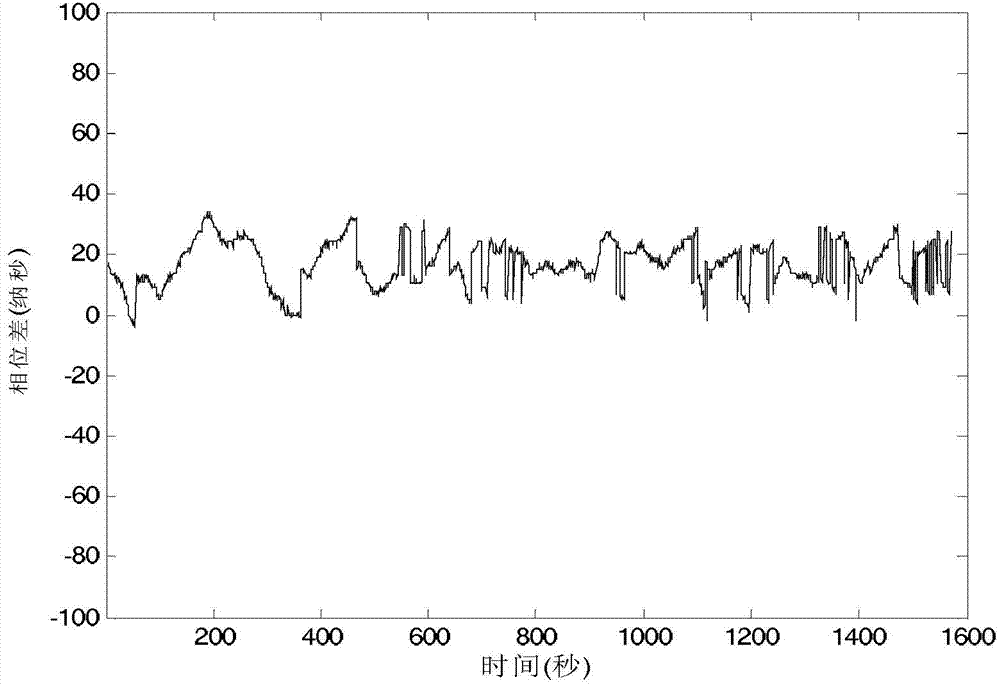

Method for realizing sub-microsecond synchronization accuracy based on PTP (Precision Time Protocol)

The invention relates to a method for realizing sub-microsecond synchronization accuracy based on a PTP (Precision Time Protocol), belonging to the technical field of communication; in order to obtain high-accuracy synchronization efficiency and save hardware investment cost, the method comprises the following steps: before a master time sends synchronization messages, synchronizing a clock and a clock source of an Ethernet transceiver; obtaining average path delay of links by a delay request information packet delay measuring mechanism or measuring a waiting delay information packet delay measuring mechanism; and performing asynchronous correction on the links so as to realize sub-microsecond synchronization accuracy. In the method, the DP83640 Ethernet transceiver is adopted, network message time stamp can be exactly obtained, the PTP protocol on an AT91RM9200 platform is realized, and sub-microsecond synchronization accuracy can be realized. Via test, the synchronization accuracy can be up to 100ns; and the whole system is low in cost, excellent in openness and expandability, and easy to implement.

Owner:GZH BEIDOU TECH GRP

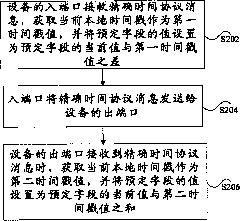

Processing method and device for time synchronization

InactiveCN101827098AThe residence time is effectively knownTime-division multiplexTransmissionTime ProtocolArrival time

The invention provides a processing method and a device for time synchronization. The method comprises the following steps: according to the receiving time of a precise time protocol message at the import of the equipment and the arrival time of the precise time protocol message at the export of the equipment, adjusting the preset field value in the precise time protocol message at the export of the equipment, thereby using the preset field to record the transmission time of the precise time protocol message between the import and the export of the equipment. The invention effectively acquires the residence time of the message in the equipment.

Owner:ZTE CORP

Method and devices for time and frequency synchronization using a phase locked loop

This invention relates to methods and devices for time and frequency synchronization, especially over packet networks using, for example, the IEEE 1588 Precision Time Protocol (PTP). Timing protocol messages are exposed to artifacts in the network such as packet delay variations (PDV) or packet losses. Embodiments of the invention provide a digital phase locked loop (DPLL) based on direct digital synthesis to provide both time and frequency signals for use at the slave (time client). An example of this DPLL in conjunction with a recursive least squares mechanism for clock offset and skew estimation is also provided.

Owner:BRITISH TELECOMM PLC +2

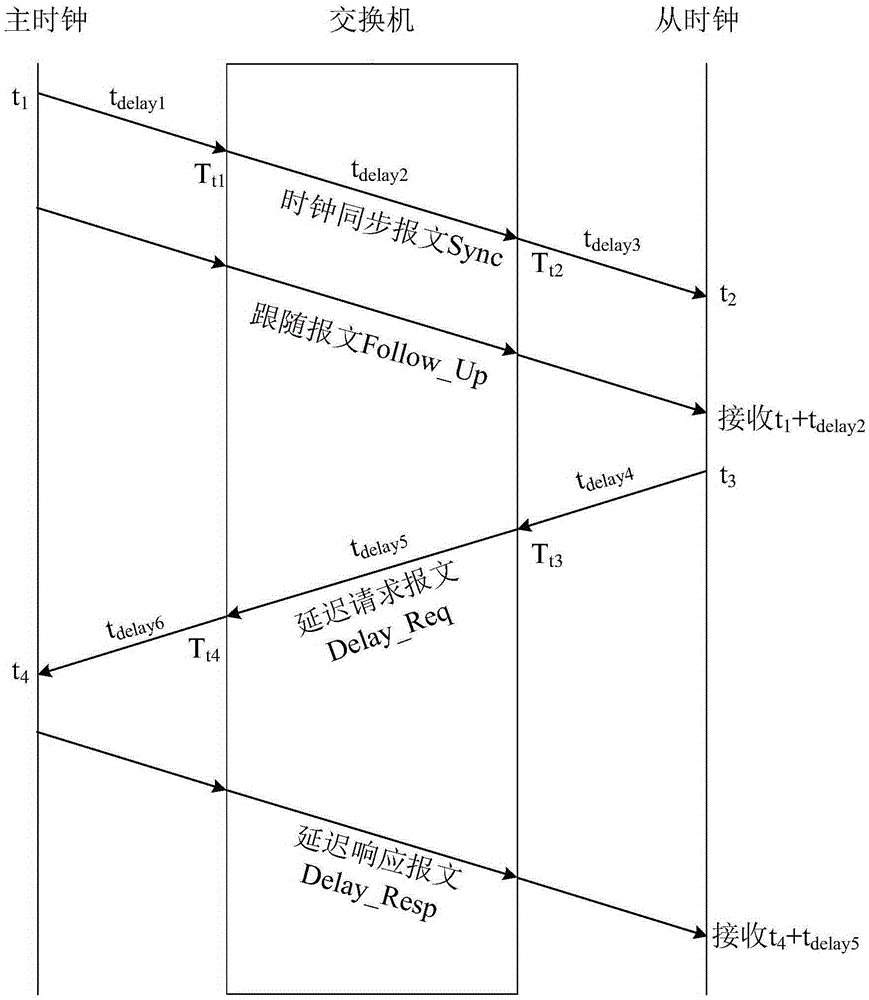

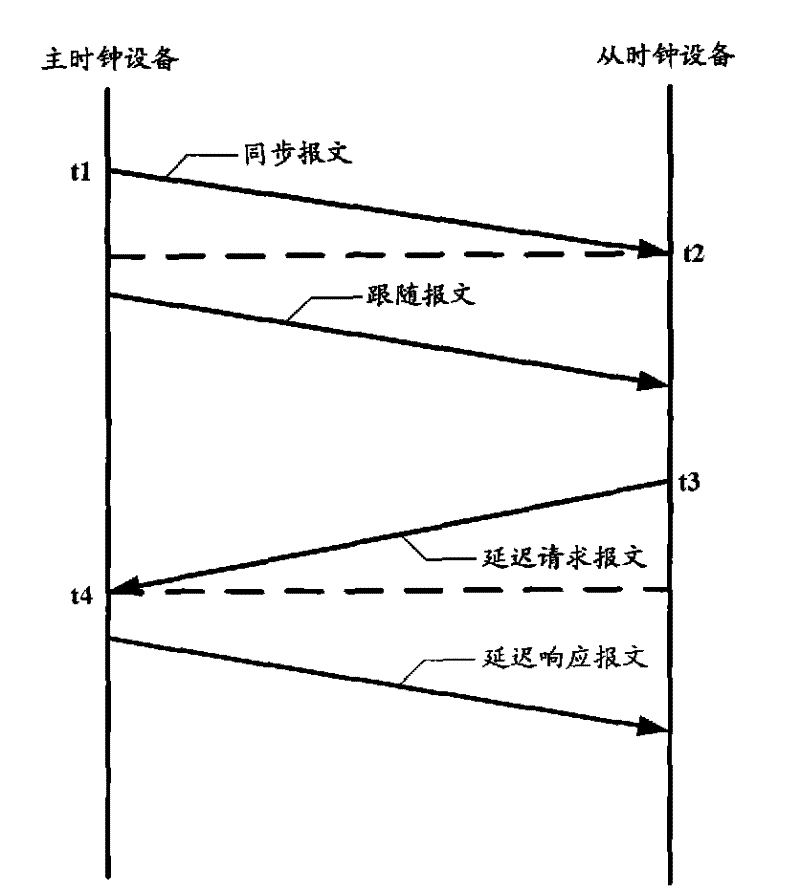

Time synchronization method and system for synchronous messages of IEEE1588 (Precision Time Protocol) master-slave clocks of intelligent transformer substation

ActiveCN102833062AImprove timing accuracyHigh time accuracyData switching networksSynchronising arrangementTime deviationTimestamp

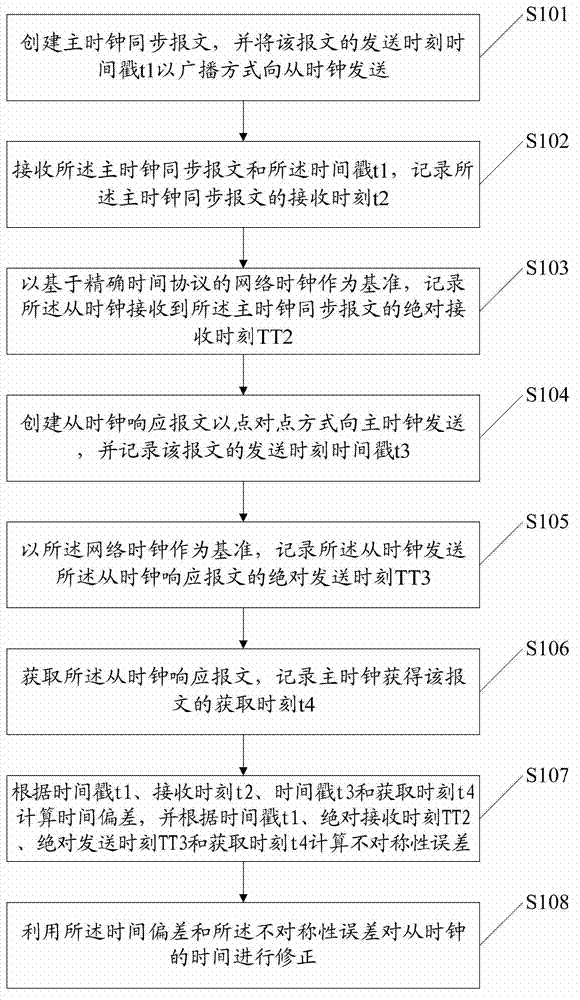

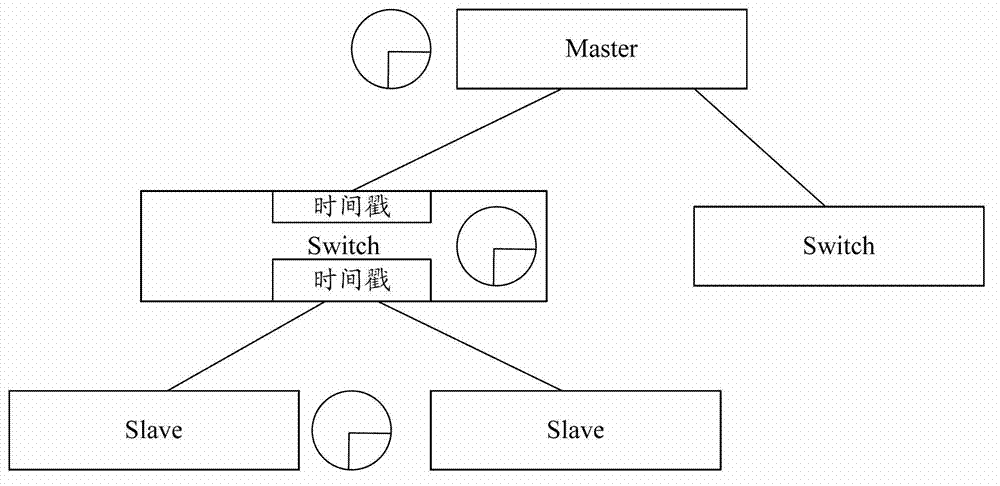

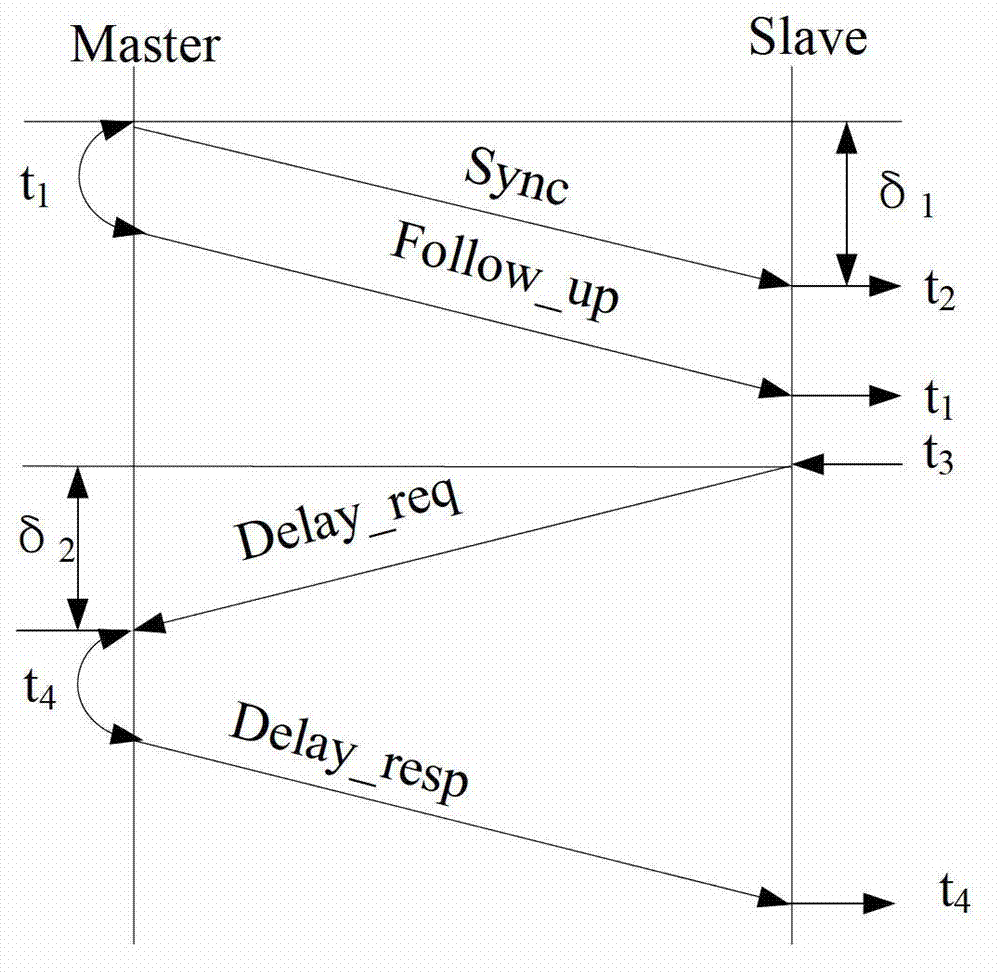

The invention discloses a time synchronization method and a time synchronization system for synchronous messages of IEEE1588 master-slave clocks of an intelligent transformer substation. The method comprises the following steps of: establishing a master clock synchronous message, and sending the timestamp t1 of the sending moment of the message to the clock in a broadcasting manner; recording a receiving moment t2 of the master clock synchronous message; recording an absolute receiving moment TT2 when the master clock synchronous message is received by a slave clock; establishing a slave clock responding message, sending the slave clock responding message to the master clock in a peer-to-peer manner, and recording the timestamp t3 of the sending moment of the message; recording an absolute sending moment TT3 when the slave clock sends the clock responding message; recording an acquiring moment t4 when the master clock acquires the message; calculating a time deviation, and calculating asymmetry errors according to the timestamp t1, the absolute receiving moment TT2, the absolute sending moment TT3 and the acquiring moment t4; and carrying out time correction on the slave clock by the time deviation and the asymmetry errors. According to the time synchronization method and the time synchronization system for synchronous messages of IEEE1588 master-slave clocks of the intelligent transformer substation, the influences of the asymmetry errors can be eliminated, and the time synchronization precision of the master-slave clocks is improved.

Owner:ZHUHAI POWER SUPPLY BUREAU GUANGDONG POWER GIRD CO

Method and devices for synchronization

ActiveUS20150092793A1Time-division multiplexSynchronising arrangementReal-time computingSynchronous Ethernet

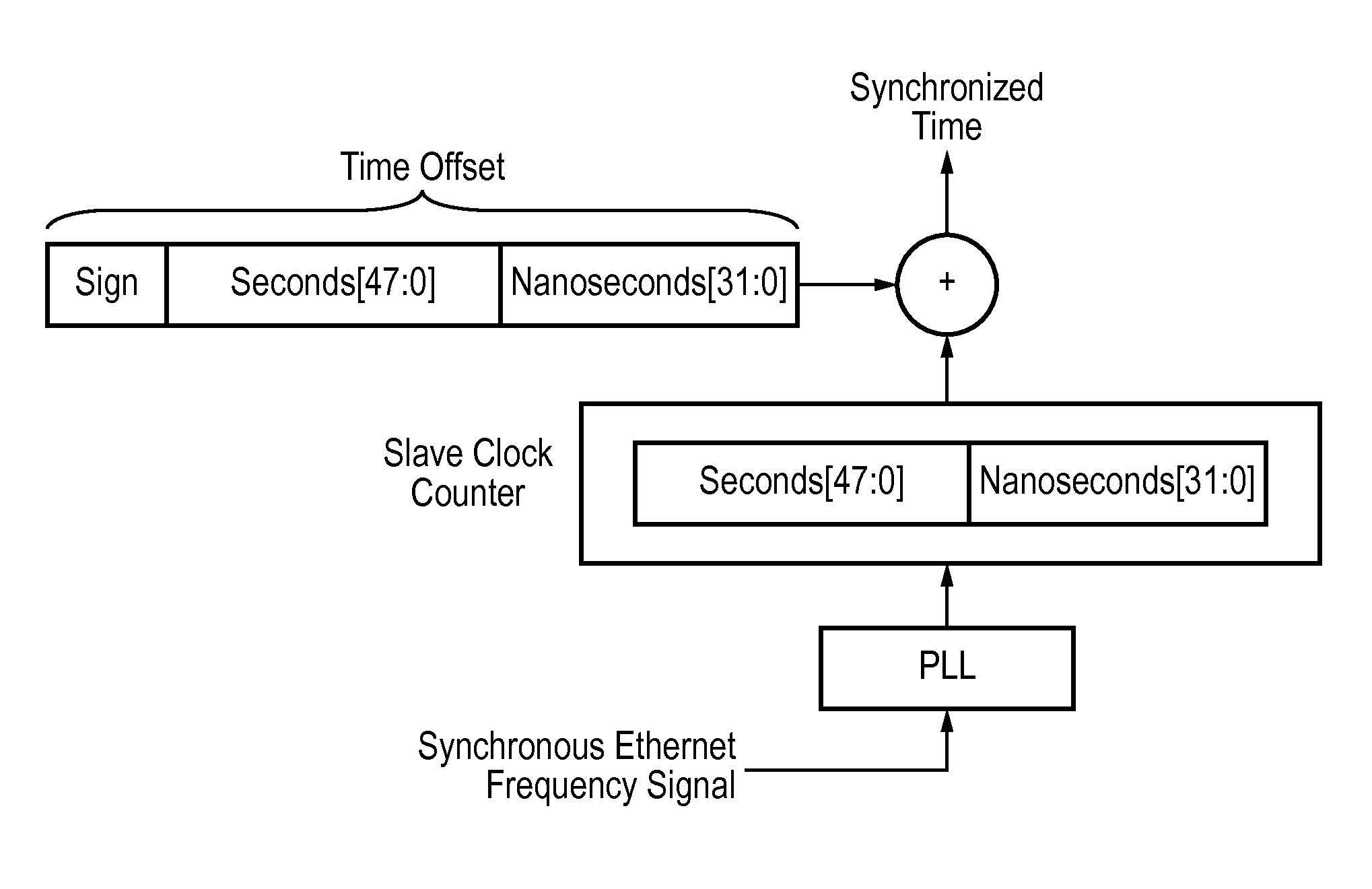

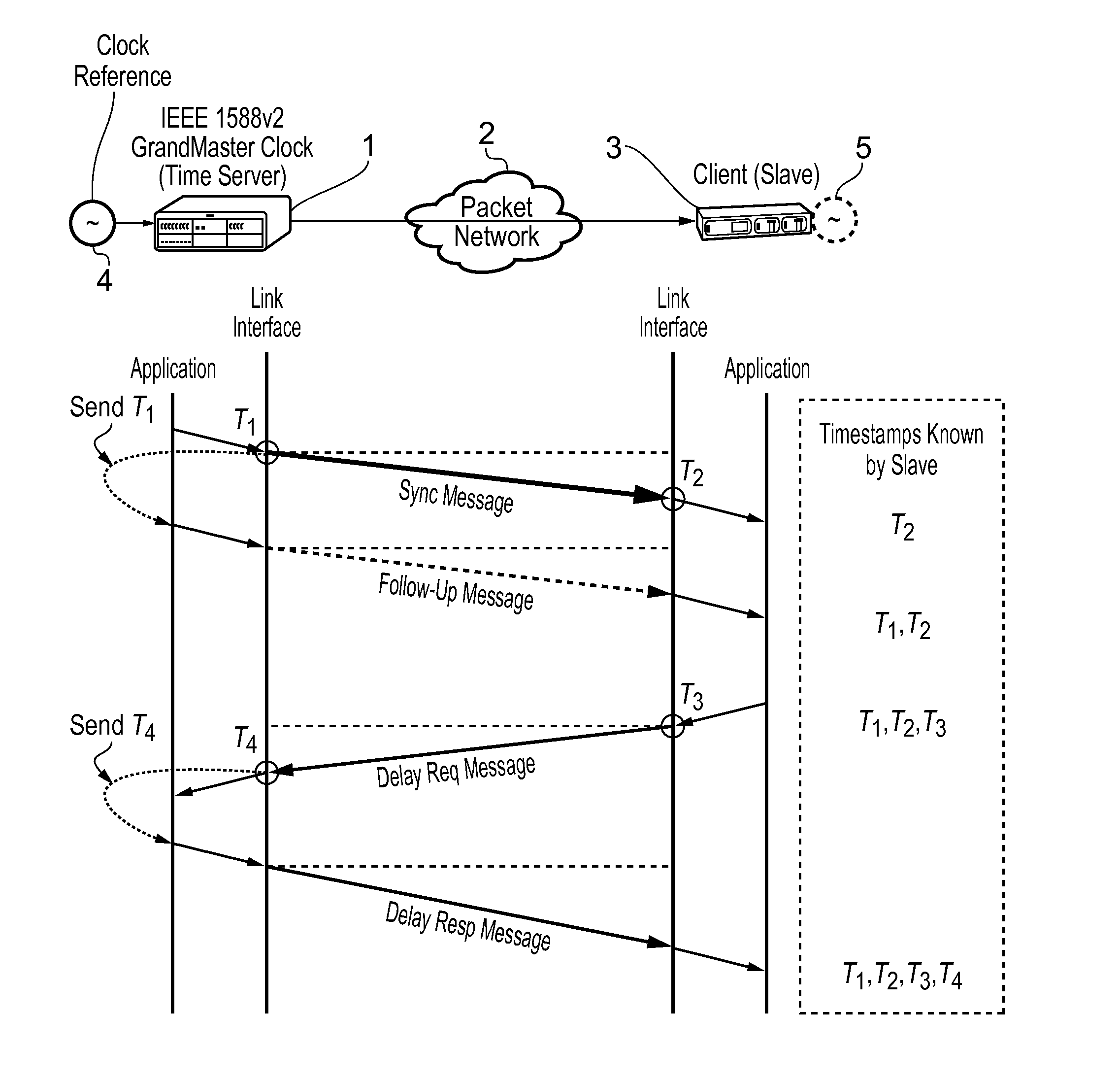

This invention relates to methods and devices for time and frequency synchronization. The invention has particular application where time and frequency synchronization over packet networks using, for example, the IEEE 1588 Precision Time Protocol (PTP) is being carried out. The primary challenge in clock distribution over packet networks is the variable transit delays experienced by timing packets, packet delay variations (PDVs). Embodiments of the invention provide a method for time offset alignment with PDV compensation where a synchronized frequency signal is available at a slave device via Synchronous Ethernet and is used to determine the compensation parameters for the PDV.

Owner:KHALIFA UNIV OF SCI & TECH +2

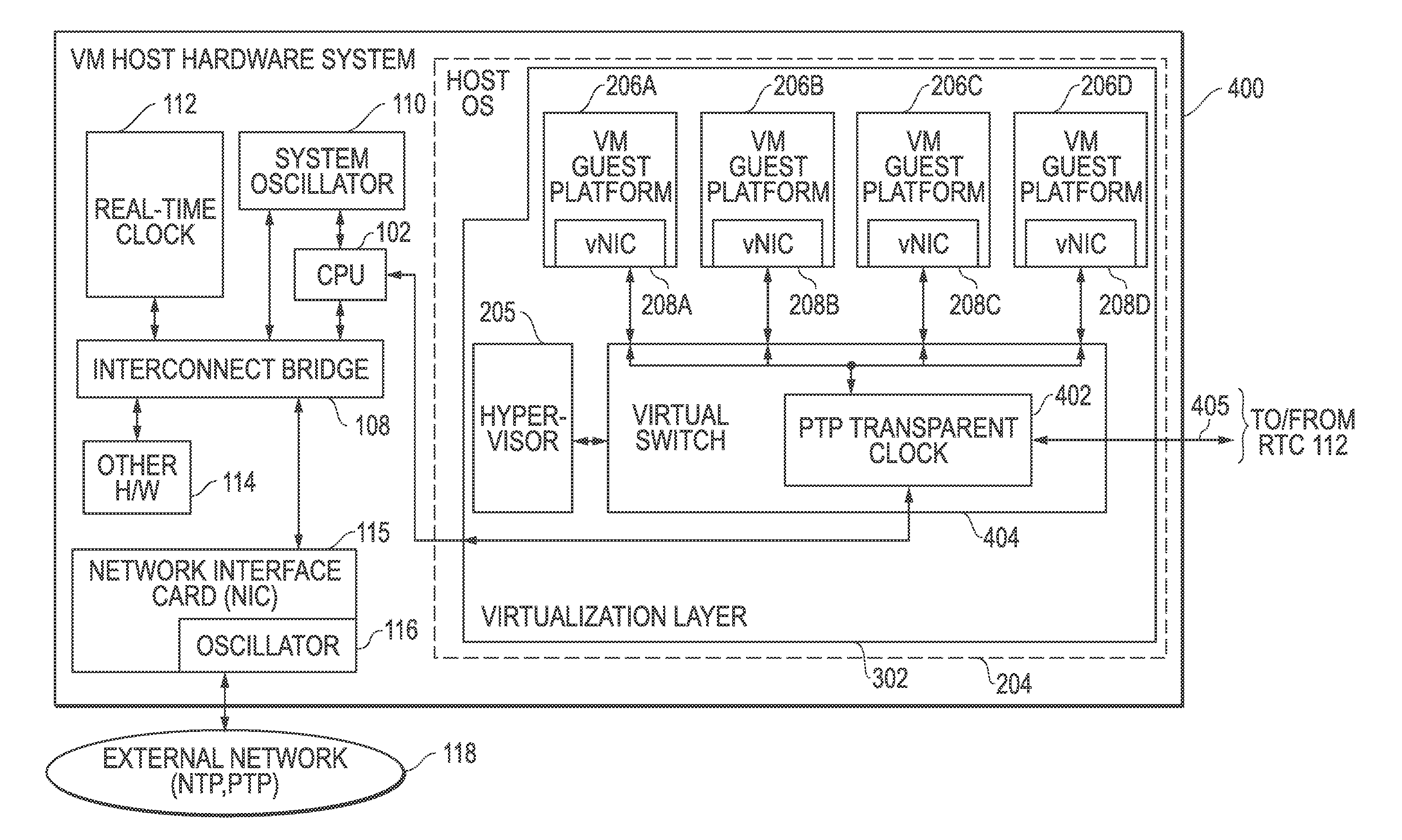

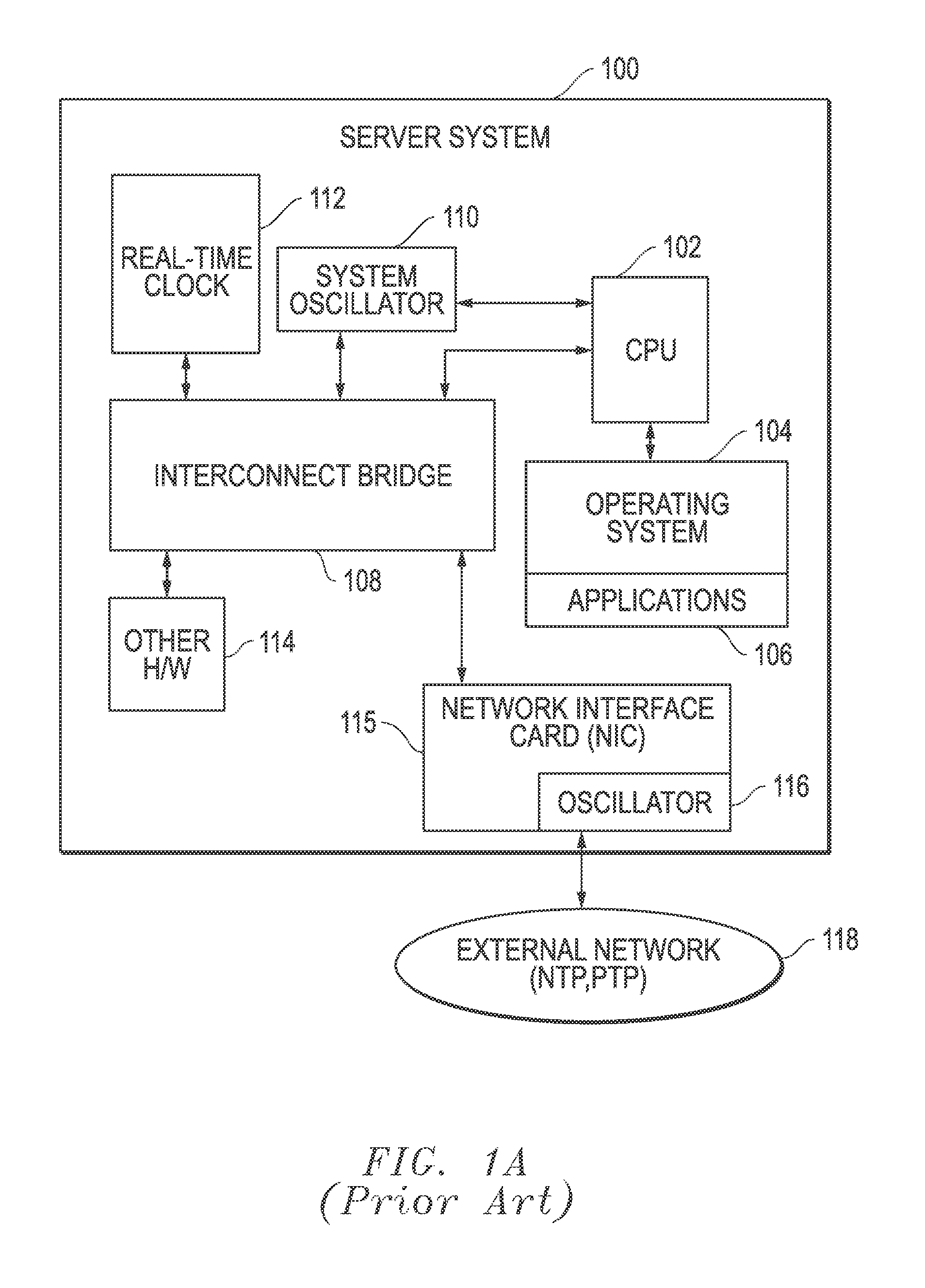

Network Packet Timing Synchronization For Virtual Machine Host Systems

ActiveUS20160112182A1Synchronisation information channelsTime-division multiplexVirtualizationSlave clock

Network timing synchronization for virtual machine (VM) host systems and related methods are disclosed that provide synchronization of master / slave clocks within VM host hardware systems. Master timing messages are sent from the master clocks to slave clocks within VM guest platforms hosted by the VM host hardware system within a virtualization layer, and return slave timing messages are communicated from the VM guest platforms to the master clock. Virtual switches within the virtualization layer use virtual transparent clocks to determine intra-switch delay times for the timing packets traversing the virtual switch. These intra-switch delay times are then communicated to target destinations and used to account for variations in packet transit times through the virtual switch. The VM guest platforms synchronize their timing using the timing messages. The master / slave timing messages can be PTP (Precision Time Protocol) timing messages and / or timing messages based upon some other timing protocol.

Owner:KEYSIGHT TECH SINGAPORE (SALES) PTE LTD

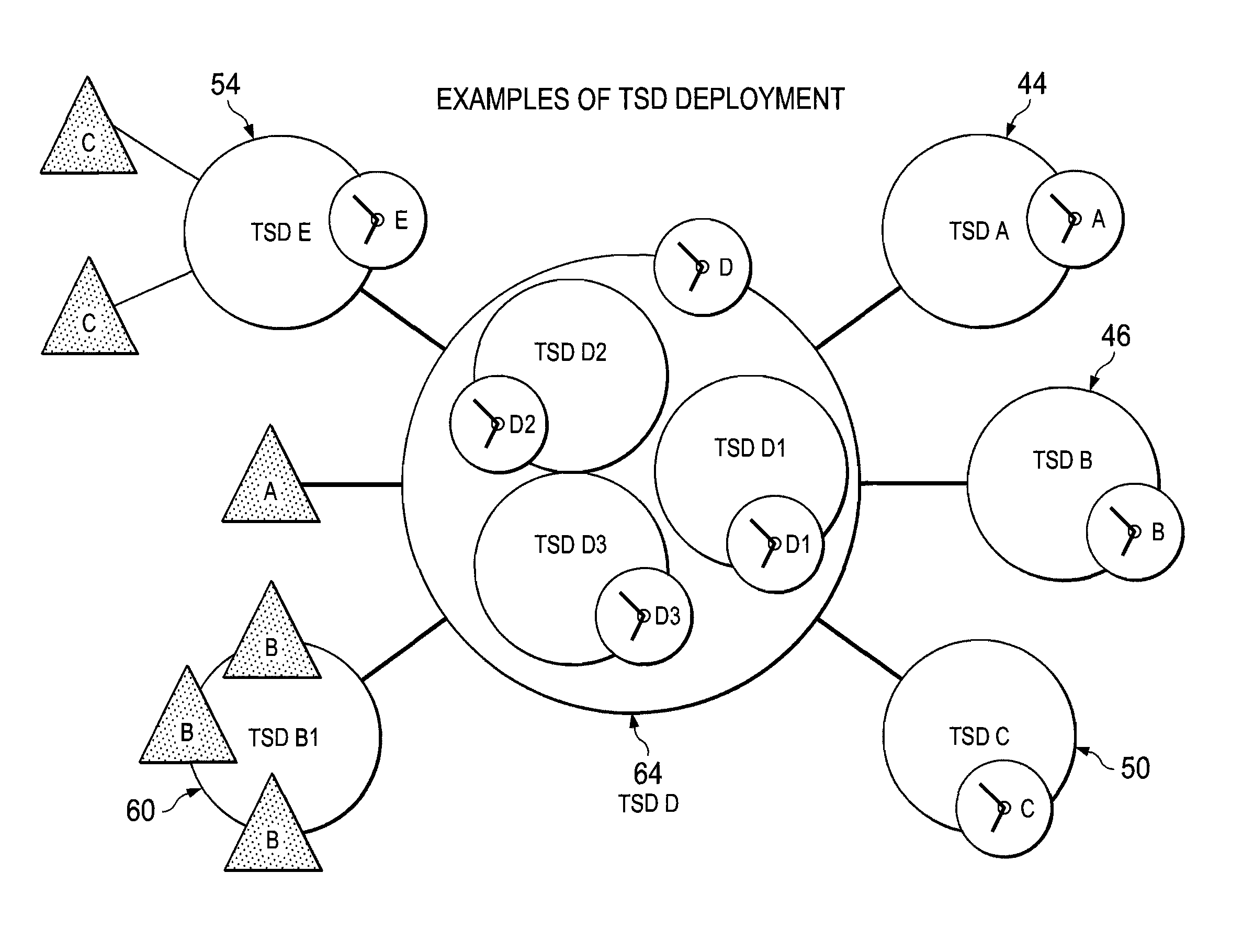

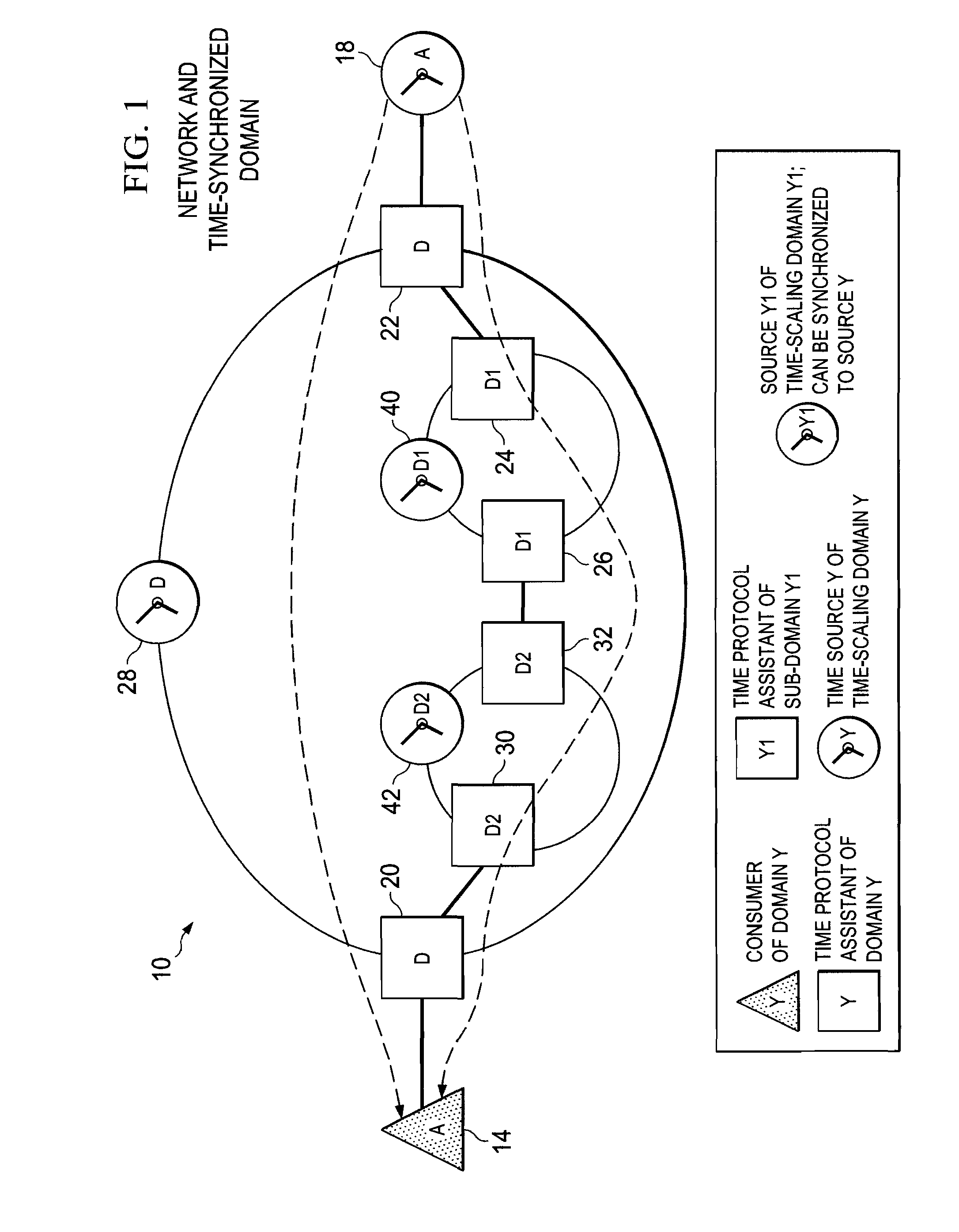

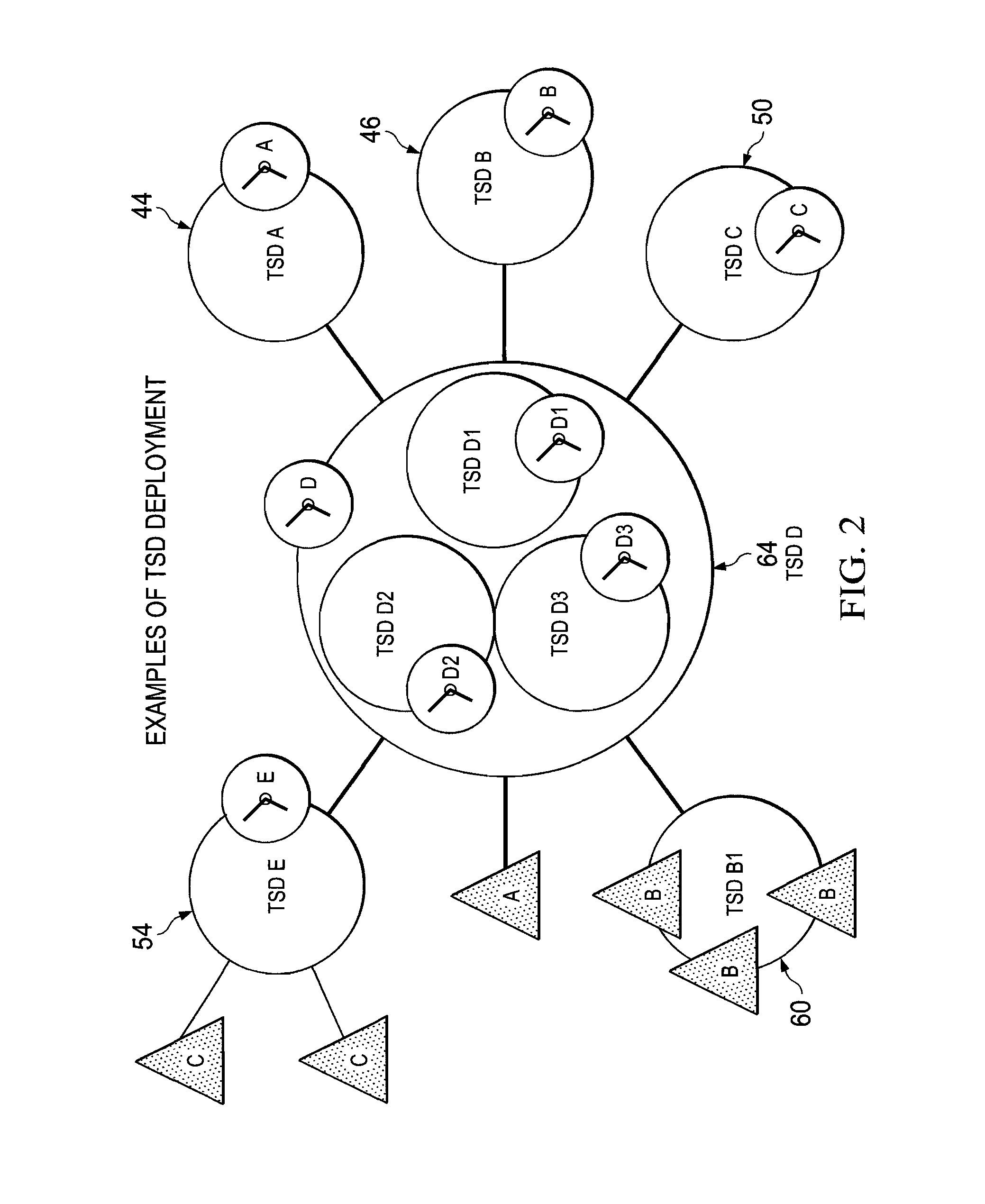

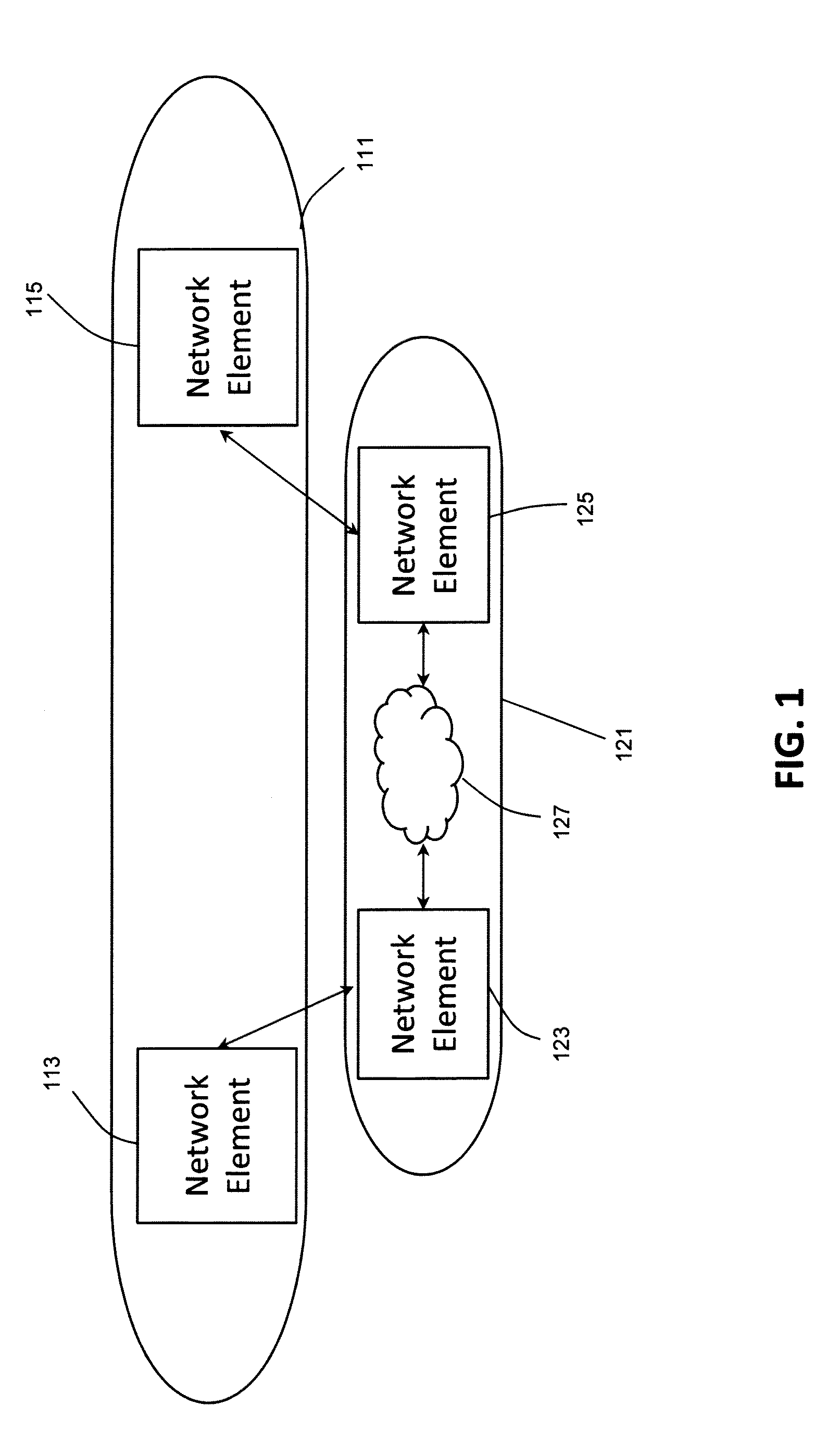

System and method for providing quality inter-domain network time transport

A method is provided in one example embodiment and includes providing a time protocol assistant associated with a time-synchronized domain (TSD). The TSD includes a set of nodes that are synchronized to a same time source. The TSD has defined egress and ingress edge points where bidirectional measurements can be made and the egress and ingress edge points are coupled to the time protocol assistant. The method also includes synchronizing one or more packets flowing through a network that includes the TSD through the same time source. In more specific embodiments, the nodes are synchronized to the same time source via the network and the same time source is a grandmaster clock that synchronizes one or more transparent clocks. In yet other embodiments, the transparent clocks manipulate precision time protocol (PTP) packets sent by the grandmaster clock.

Owner:CISCO TECH INC

Clock synchronization method and device

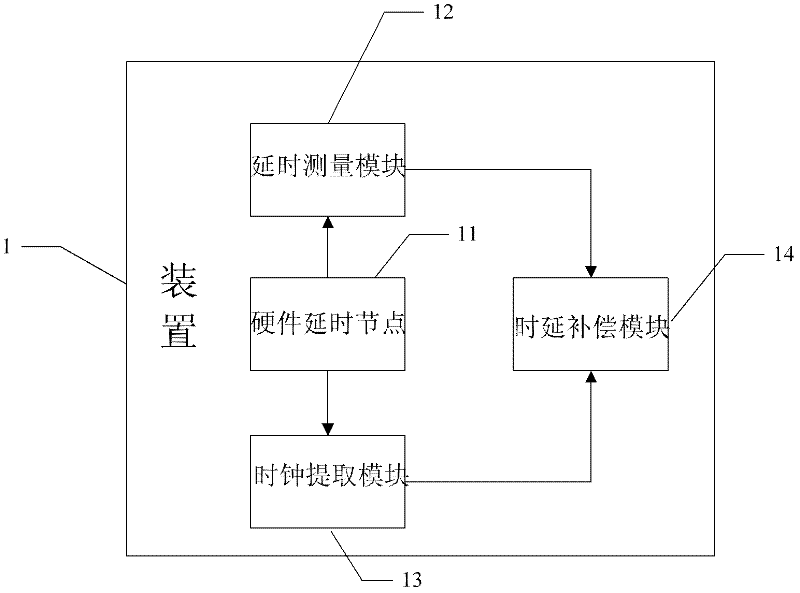

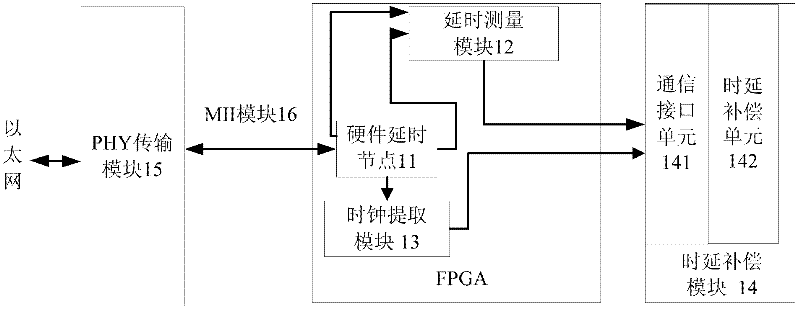

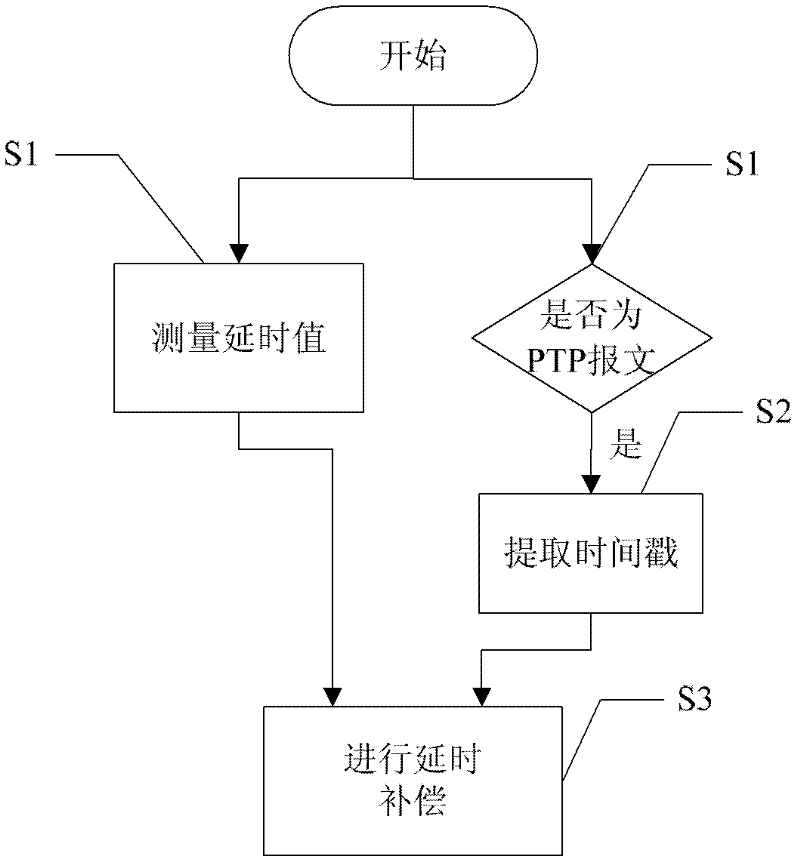

ActiveCN102244572AHigh synchronization accuracyAccurate delay valueTime-division multiplexData switching networksTimestampMessage passing

The invention discloses a clock synchronization device and a clock synchronization method. The device comprises a delay measurement module, a clock extraction module and a delay compensation module, wherein the delay measurement module is used for measuring a delay value of a message passing through a hardware delay node in real time, and transmitting the delay value to the delay compensation module; the clock extraction module is used for extracting a timestamp stamped before a precision time protocol message enters the hardware delay node when the message is determined to be the precision time protocol message, and transmitting the timestamp to the delay compensation module; and the delay compensation module is used for correspondingly performing delay compensation according to the received delay value and the received timestamp. Compared with the delay value, computed as a fixed value, of the precision time protocol (PTP) message passing through a certain hardware delay node, the delay value, measured in real time, of the PTP message passing through the certain hardware delay node is more precise. Therefore, corresponding timestamp regulation can be performed according to the precise delay value and the extracted timestamp, and the synchronization accuracy of the precision time protocol message is further improved.

Owner:ZTE CORP

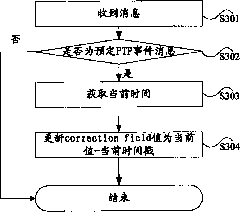

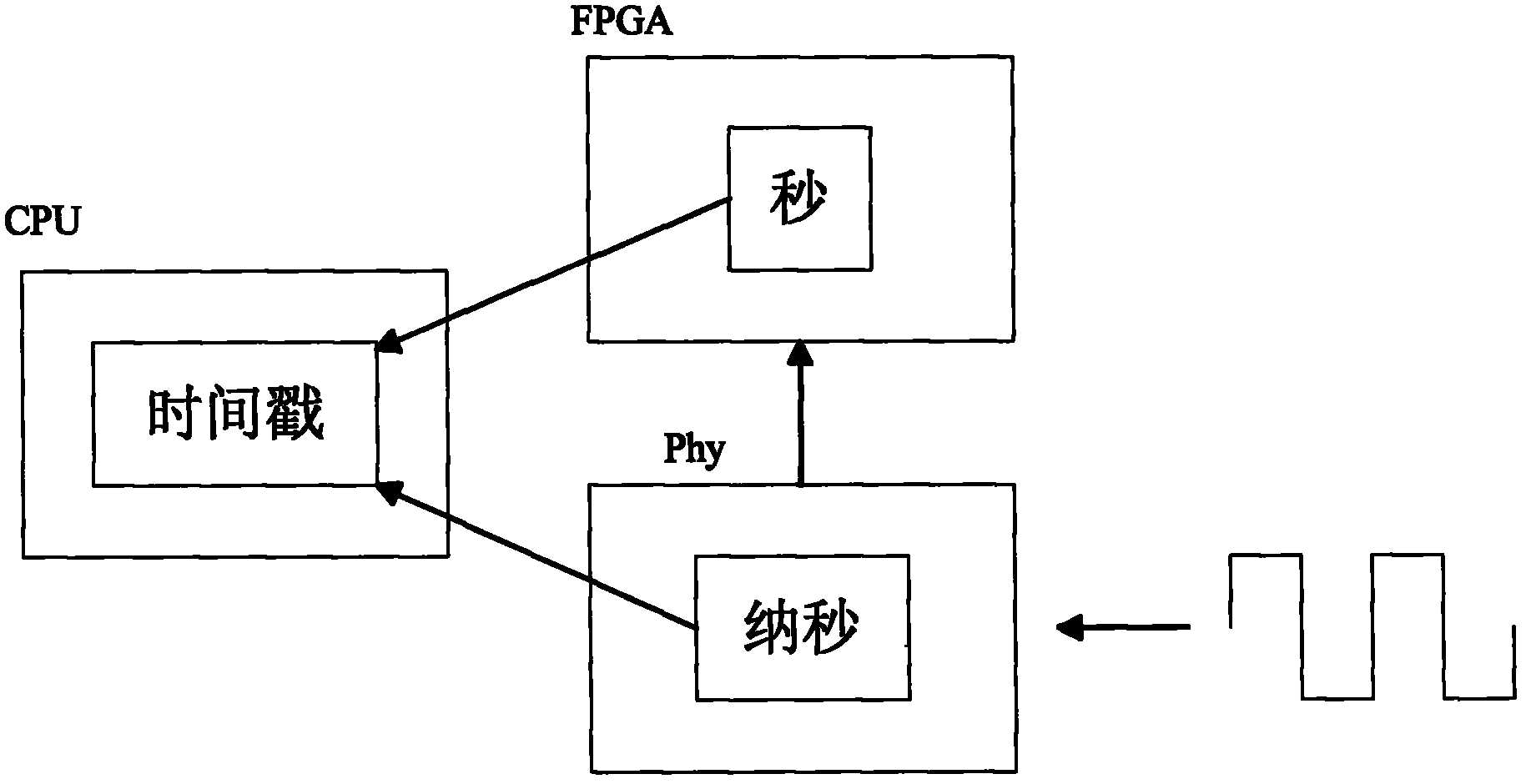

Method for realizing precision time protocol (PTP) with nanosecond-level precision

ActiveCN102195768AHigh precisionImprove accuracySynchronising arrangementCommunications systemTimestamp

The invention discloses a method for realizing a precision time protocol (PTP) with nanosecond-level precision. The method comprises the following steps of: identifying a PTP message and recording a leaving or arrival timestamp of the PTP message in a physical layer (PHY) chip; realizing frequency synchronization by using a synchronization Ethernet (SyncE) technology in a physical layer; and managing the timestamp in a way of combining the PHY chip and a field programmable gate array (FPGA), and ensuring the consistency of time in the PHY chip and FPGA maintenance time at the arrival of the PTP message by adopting a software processing method. By the technical scheme provided by the invention, the requirements of a communication system on time synchronization precision can be met, and the synchronization precision of the PTP reaches a nanosecond level.

Owner:北京神州数码云科信息技术有限公司

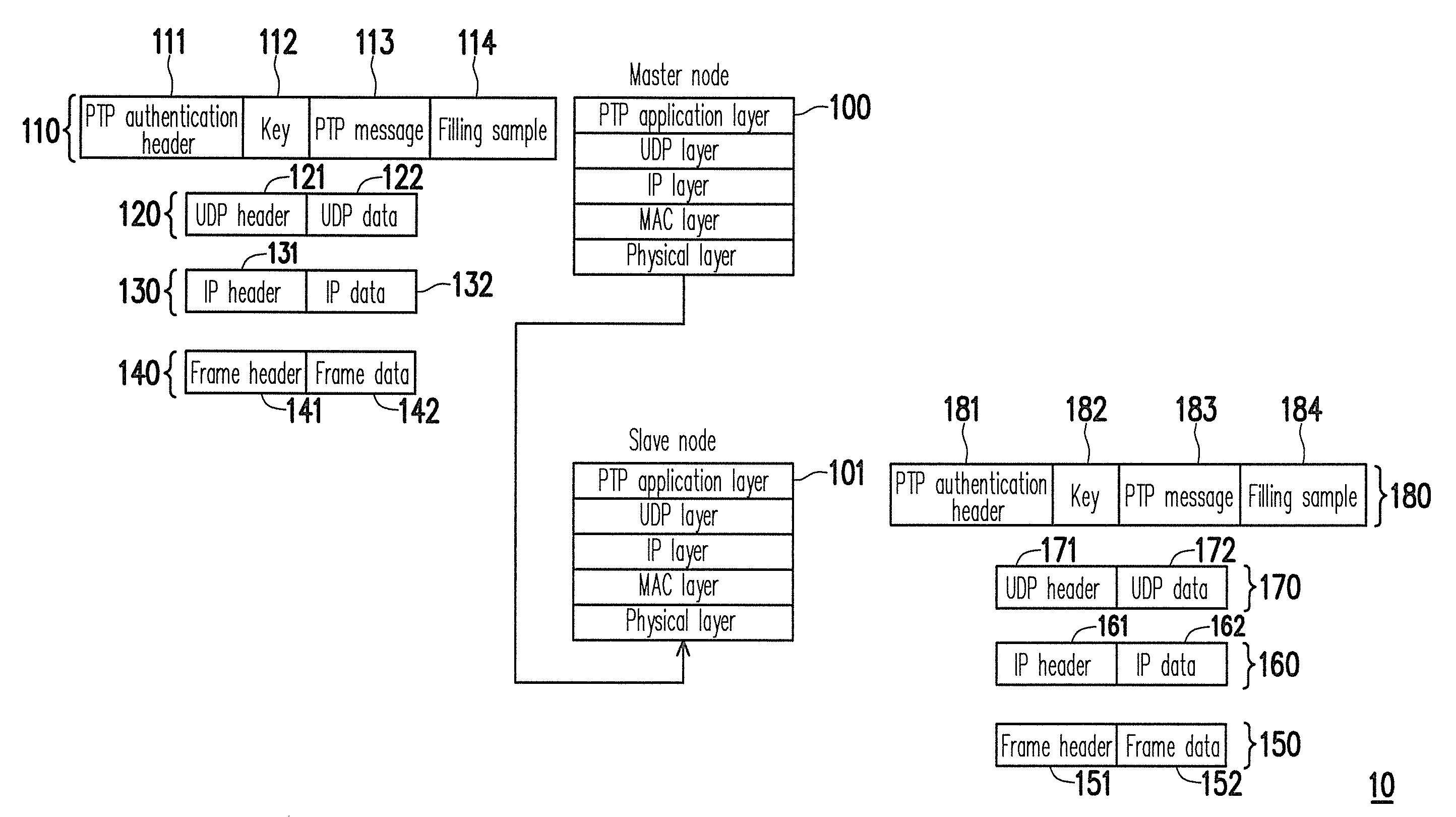

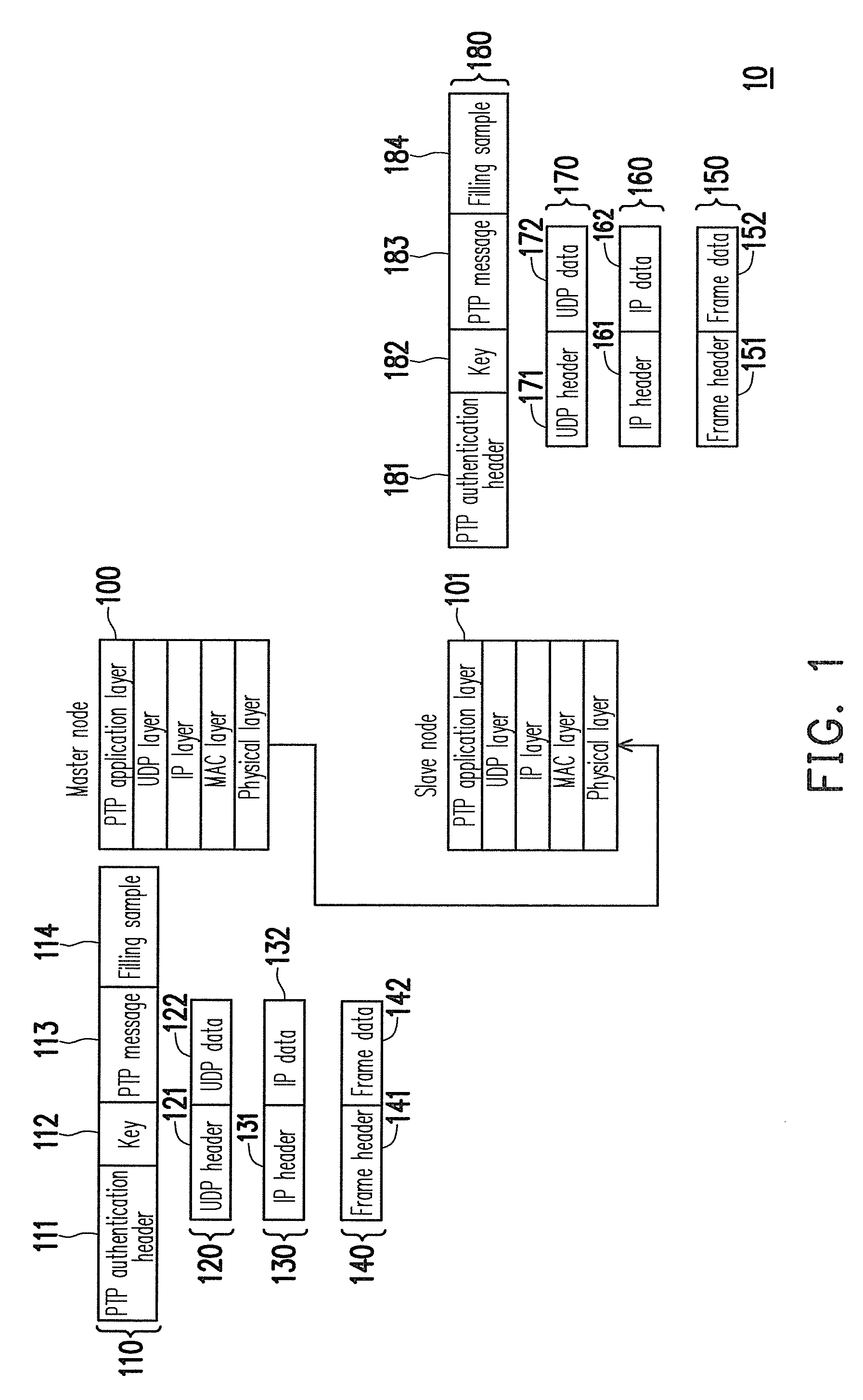

Method and apparatus for encrypting/decrypting packet data of precise time synchronization protocol and time synchronization system

ActiveUS20100153742A1High transparencyImprove securityEncryption apparatus with shift registers/memoriesUser identity/authority verificationComputer hardwareTime Protocol

A method and an apparatus for encrypting / decrypting packet data of a precise time synchronization protocol and a time synchronization system are illustrated. The method is suitable for the time synchronization system using a precise time protocol. The time synchronization system includes a master node and a slave node, wherein the slave node synchronizes its time with the master node. In the method for encrypting / decrypting packet data of the precise time synchronization protocol, an encryption / decryption hardware device is disposed on the hardware protocol layer of each of the master node and the slave node. The hardware protocol layer is under the data link layer, and includes the data link layer. A synchronization message is encrypted by using the encryption / decryption hardware devices of the master node to generate a frame data, and the frame data is decrypted by using the encryption / decryption hardware devices of the slave node to obtain the synchronization message.

Owner:IND TECH RES INST

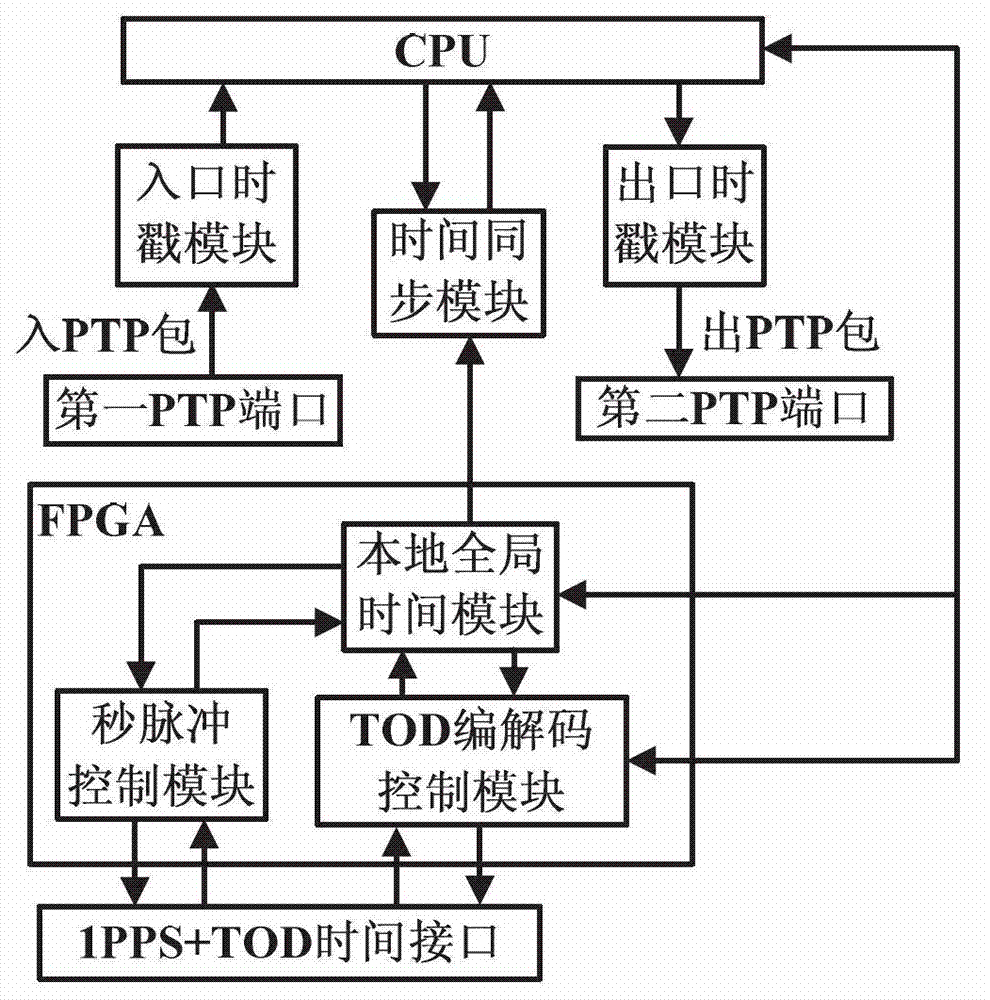

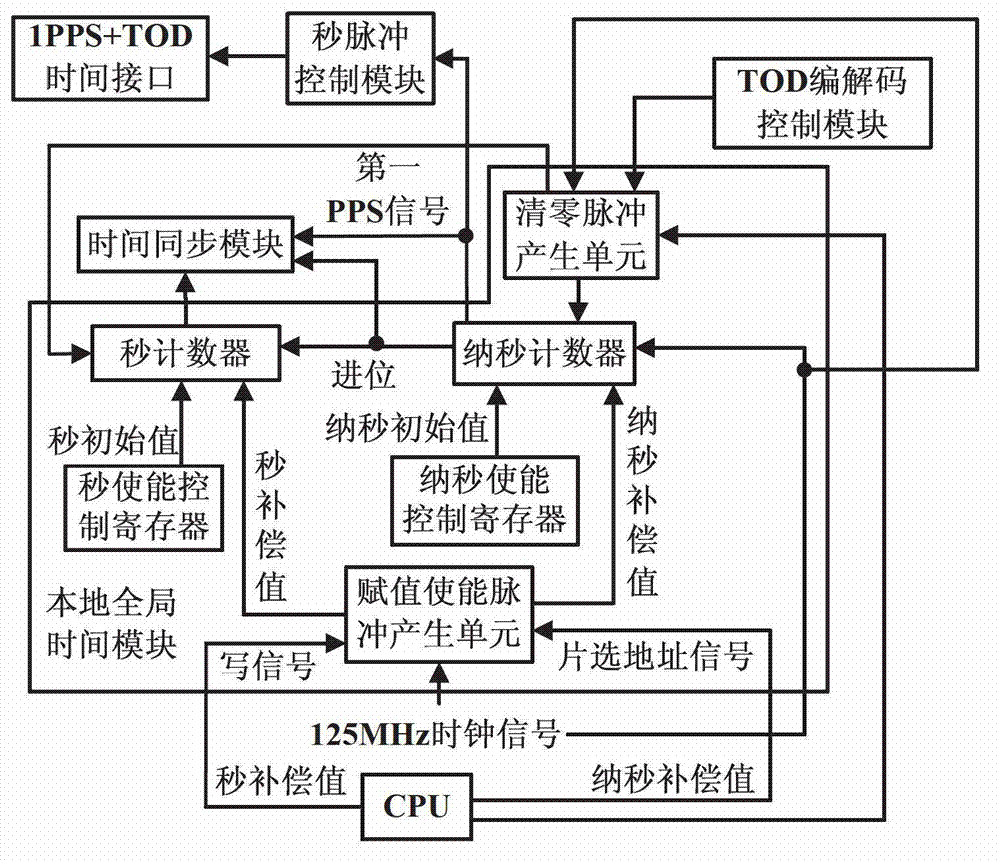

System time synchronization device and method in packet transport network

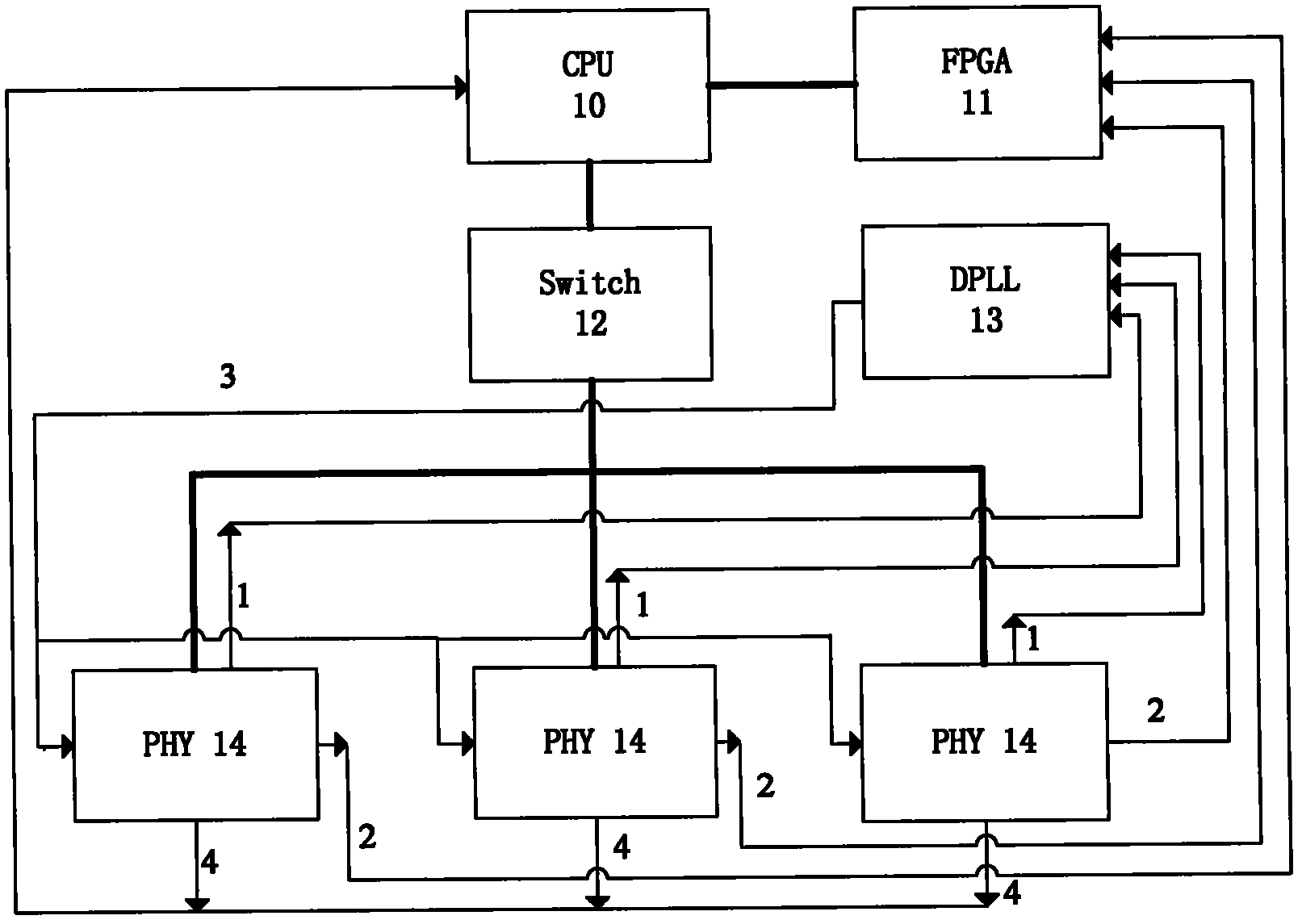

ActiveCN102868515AImprove reliabilityAchieving High Precision TimingTime-division multiplexSynchronising arrangementEntry timeOptical communication

The invention discloses a system time synchronization device and method in a packet transport network, relating to packet transport networks in optical communication. The device comprises a CPU (central processing unit), a time synchronization module, an FPGA (field-programmable gate array), a 1PPS+TOD (1pulse per second+time of day) time interface, an entry time stamp module, an exit time stamp module, a first PTP (precision time protocol) port and a second PTP port, wherein the FPGA is connected with the CPU through the time synchronization module; the first PTP port is connected with the CPU through the entry time stamp module; the second PTP port is connected with the CPU through the exit time stamp module; and the FPGA is also respectively connected with the CPU and the 1PPS+TOD time interface. The device and the method have the following advantages: through combination of software and hardware, nanosecond precision system time synchronization between master and slave stations in the packet transport network can be effectively and quickly implemented, and high precision timing of the whole network can be implemented.

Owner:FENGHUO COMM SCI & TECH CO LTD

Method and devices for synchronization using linear programming

This invention relates to methods and devices for synchronization using linear programming, especially over packet networks using, for example, the IEEE 1588 Precision Time Protocol (PTP). Timing protocol messages are exposed to artifacts in the network such as packet delay variations (PDV) or packet losses. Embodiments of the invention provide a two-dimensional linear programming technique for estimating clock offset and skew, particularly from two-way exchange of timing messages between a master and a slave device. Some embodiments include a skew and offset adjustable free-running counter for regenerating the master time and frequency at the slave device.

Owner:BRITISH TELECOMM PLC +2

Method and devices for compensating for path asymmetry

This invention relates to methods and devices for compensating for path asymmetry, particularly with reference to time and frequency synchronization. The invention has particular application where time and frequency synchronization over packet networks using, for example, the IEEE 1588 Precision Time Protocol (PTP) is being carried out. Typically communication path delays between a time server (master) and a client (slave) are estimated using the assumption that the forward delay on the path is the same as the reverse delay. As a result, differences between these delays (delay asymmetries) can cause errors in the estimation of the offset of the slave clock from that of the master. Embodiments of the invention provide techniques and devices for compensating for path delay asymmetries that arise when timing protocol messages experience dissimilar queuing delays in the forward and reverse paths.

Owner:BRITISH TELECOMM PLC +2

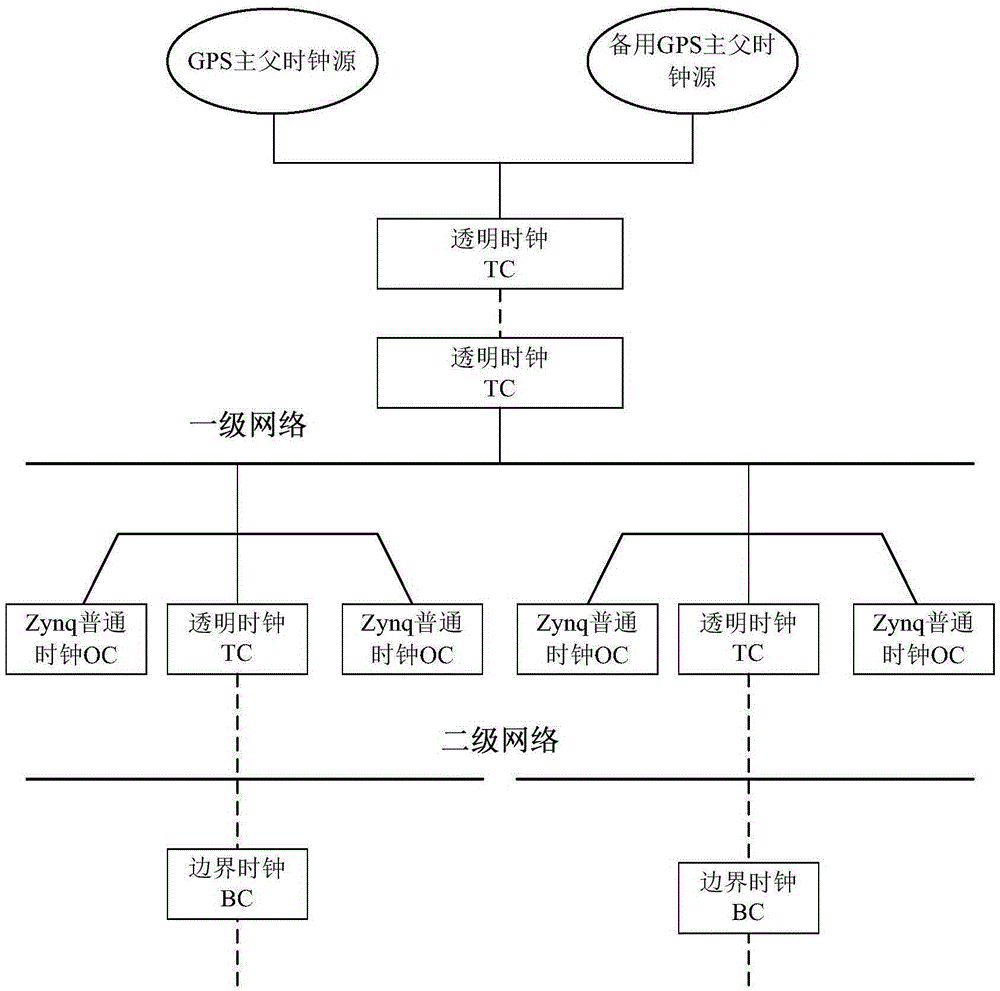

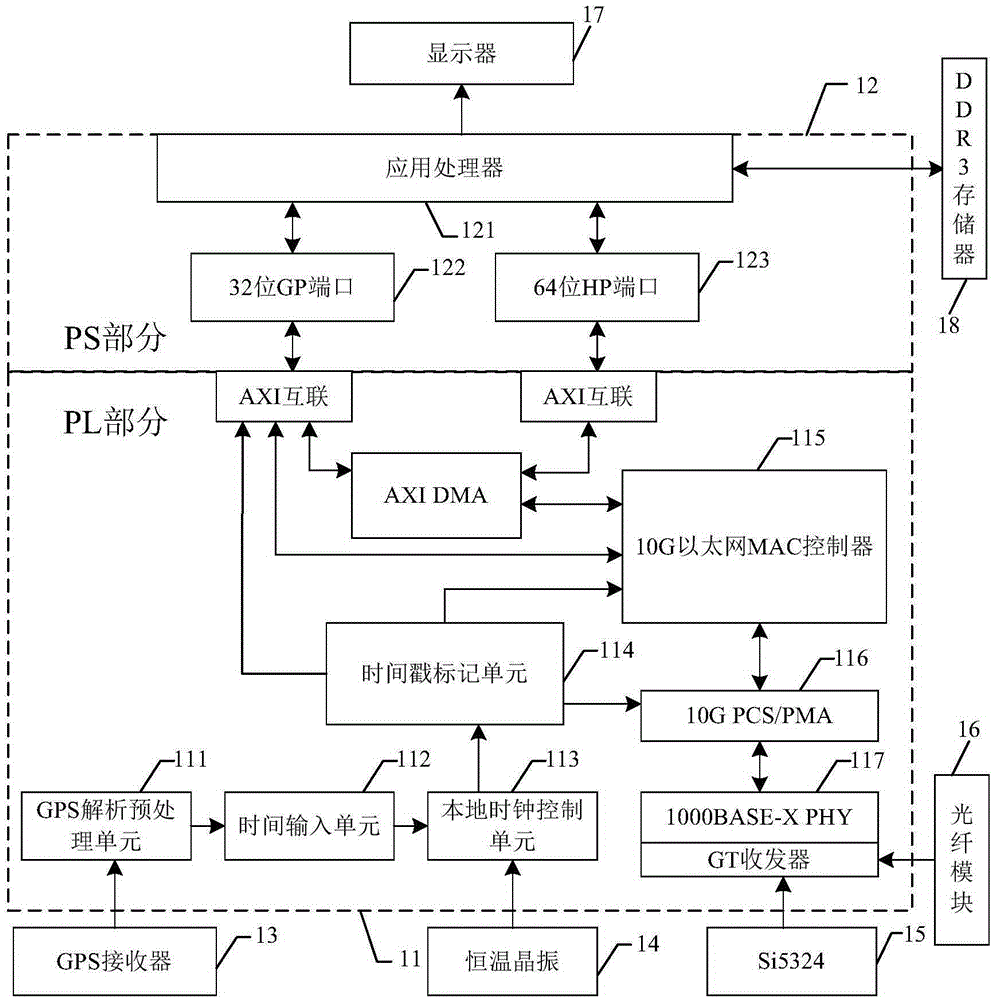

SOPC (System on a Programmable Chip) networking based sub-microsecond level clock synchronizing method and system

ActiveCN105429725ASynchronous high precisionGuaranteed accuracy requirementsTime-division multiplexSlave clockNetwork switch

The invention provides an SOPC (System on a Programmable Chip) networking based sub-microsecond level clock synchronizing method. The clock synchronizing method comprises the steps of synchronizing UTC (Universal Time Coordinated) of a remote reference primary parent clock with UTC from an external GPS (Global Positioning System) clock or a Big Dipper system clock; synchronizing each node of a local first-level PTP (Precision Time Protocol) domain with the remote reference primary parent clock through a network switching device which supports a transparent clock function; receiving an optimal primary clock from a network at the same level by each Zynq platform based slave clock which supports IEEE158V2 protocol and gigabit Ethernet for time synchronization and frequency synchronization; when a PTP domain at the next level synchronizes with the primary parent clock through a border clock, performing clock synchronization by a primary clock at the upper level; and during the period that the PTP domain at the same level masters an independent clock synchronization control right, selecting the optimal primary clock as the primary clock of the network at the same level through an optimal primary clock algorithm. The invention also provides an SOPC networking based sub-microsecond level clock synchronizing system which adopts the clock synchronizing method.

Owner:CENT SOUTH UNIV

Method and devices for time and frequency synchronization

This invention relates to methods and devices for time and frequency synchronization, especially over packet networks using, for example, the IEEE 1588 Precision Time Protocol (PTP). Timing protocol messages are exposed to artifacts in the network such as packet delay variations (PDV) or packet losses. Embodiments of the invention provide a recursive least squares mechanism for clock offset and skew estimation. A major potential advantage of such estimation is that it does not require knowledge of the statistics of the measurement noise and process noise. An implementation using a digital phase locked loop based on direct digital synthesis to provide both time and frequency signals for use at the slave (time client) is also provided.

Owner:KHALIFA UNIV OF SCI & TECH & RES KUSTAR +2

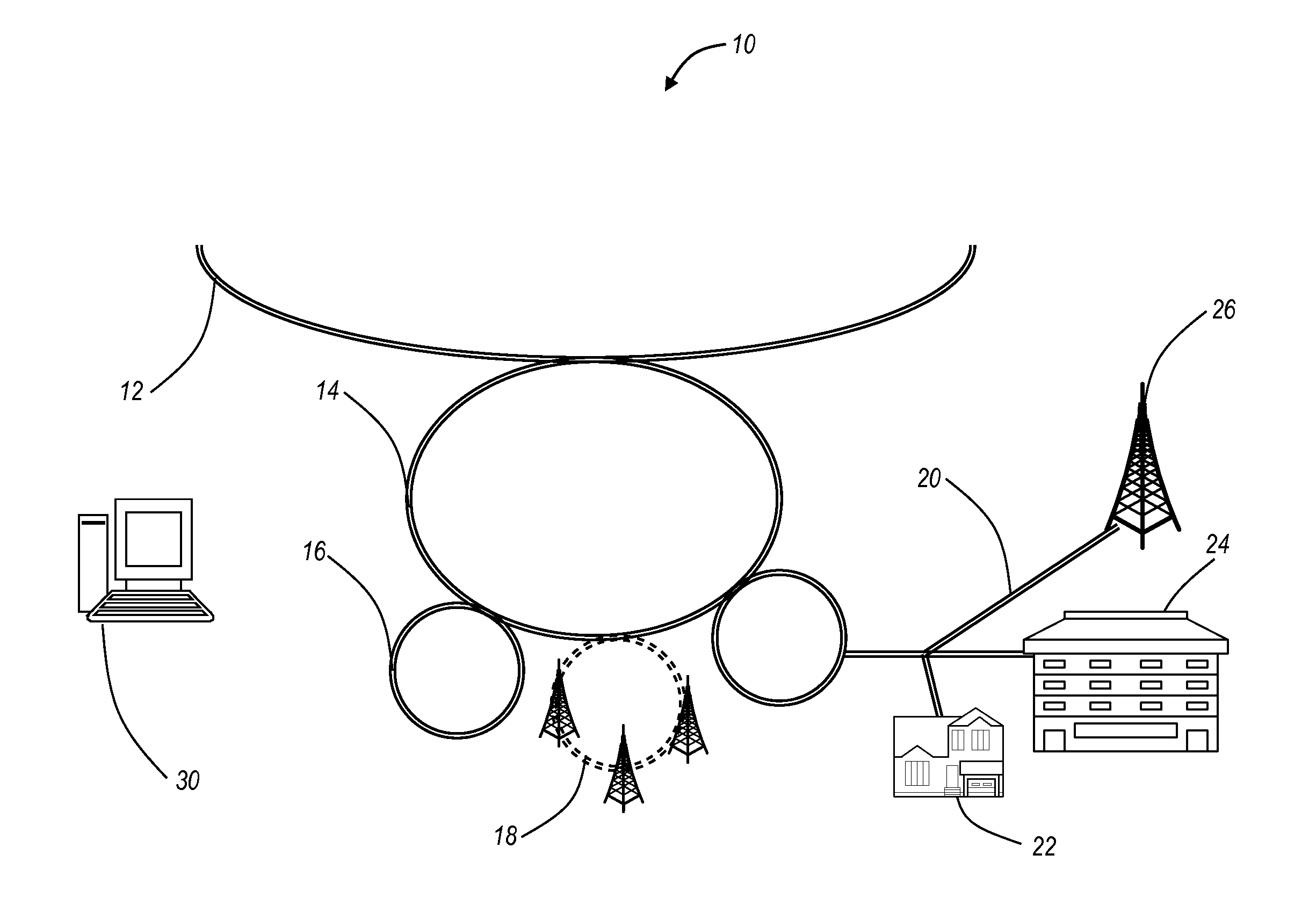

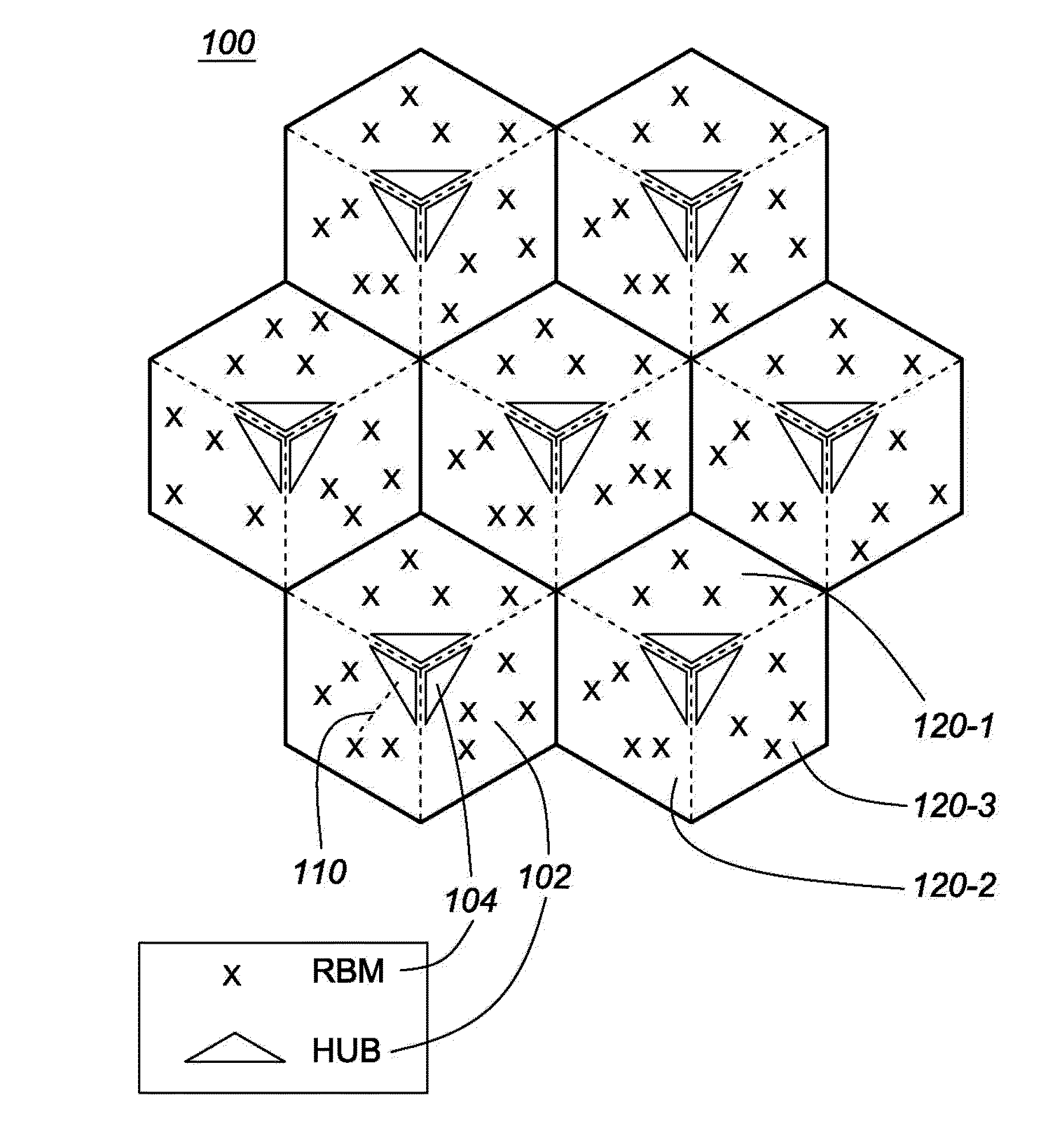

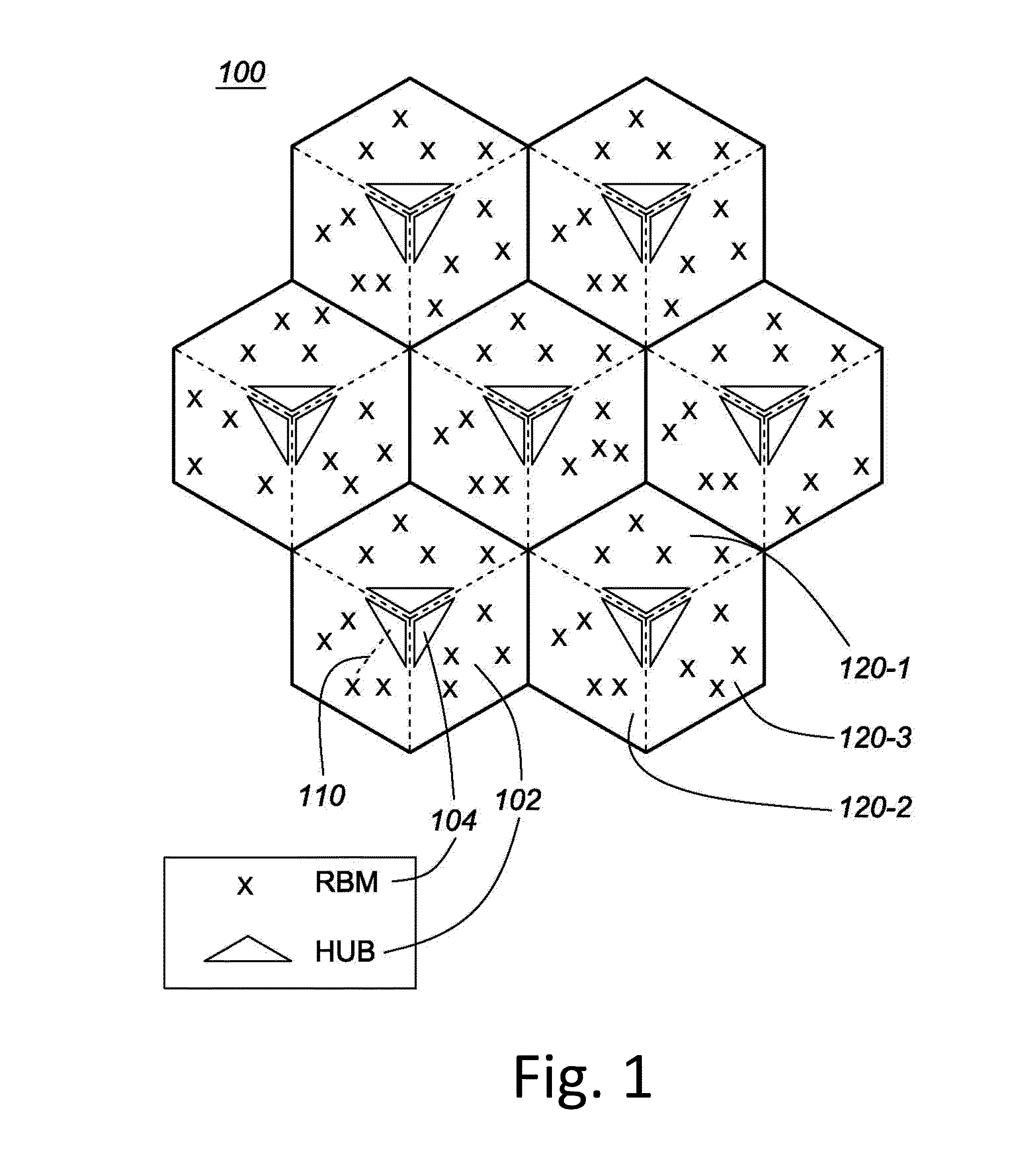

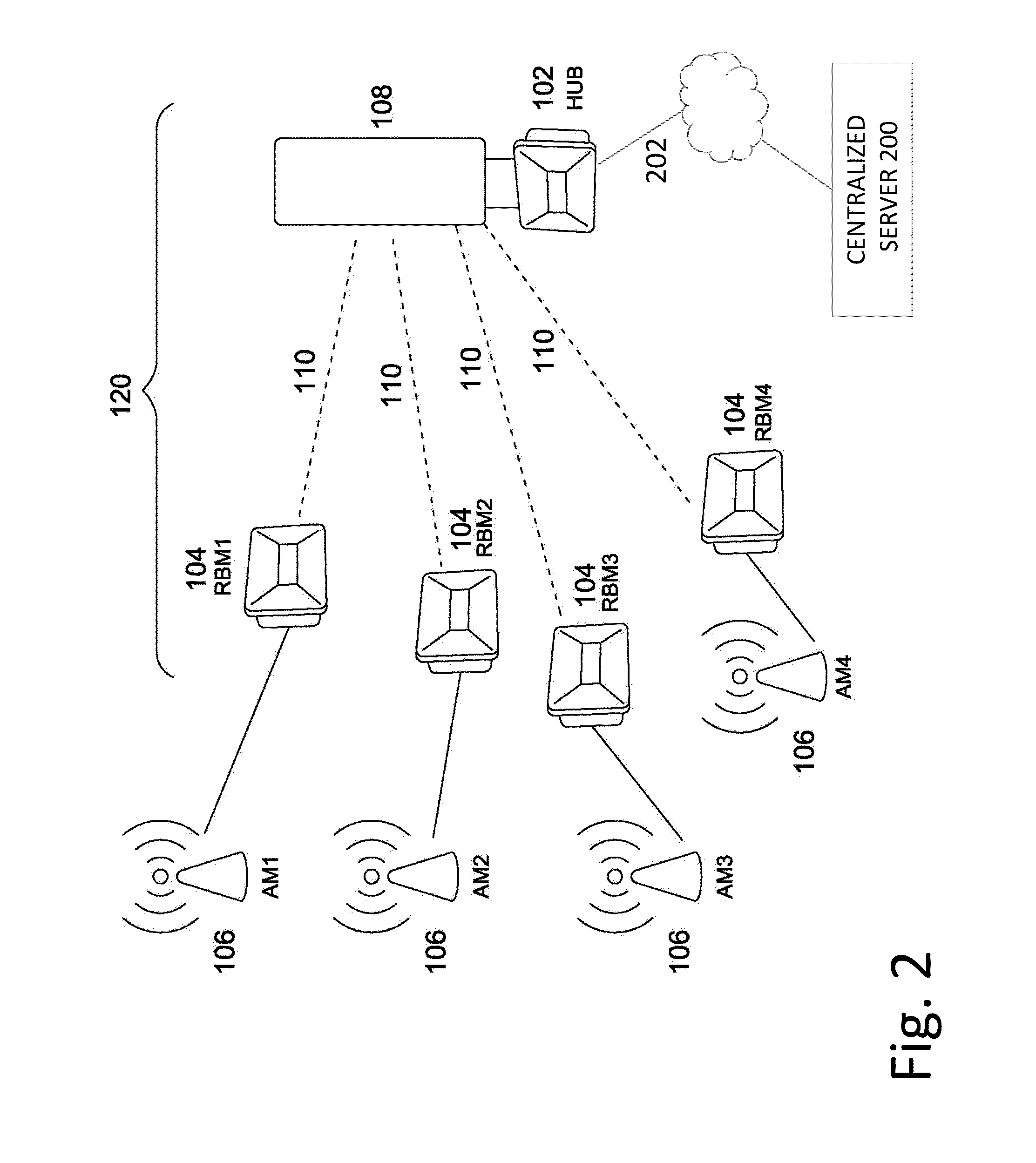

System and method for clock synchronization in a wireless backhaul network using IEEE 1588 precision time protocol

A method and system is disclosed for clock synchronization in a wireless backhaul network, based on the IEEE1588 Precision Time Protocol (PTP). The network comprises a plurality of hubs, each hub serving one or more remote backhaul modules. Each hub comprises a slave clock, which communicates with a master clock through forward and reverse links. The method comprises, for each hub, estimating the frequency drift {circumflex over (α)} and offset {circumflex over (β)} from the forward and reverse links between the master and slave clock, estimating the accuracy of {circumflex over (α)} and {circumflex over (β)}, determining the least congested link, and adjusting the frequency of the slave clock based on {circumflex over (α)} and {circumflex over (β)} from the least congested link. A fixed or variable time window size is selected to achieve a desired accuracy of {circumflex over (α)} and {circumflex over (β)}. The method may comprise estimating a maximum holdover time for maintaining synchronization with a desired confidence level.

Owner:BLINQ NETWORKS

Network distributed packet-based synchronization

A transparent clock may be provided between edge nodes of a non-precision time protocol network, with an arrival time of a packet at an edge of the non-precision time protocol network carried in a reserved field of a packet.

Owner:MICROSEMI STORAGE SOLUTIONS

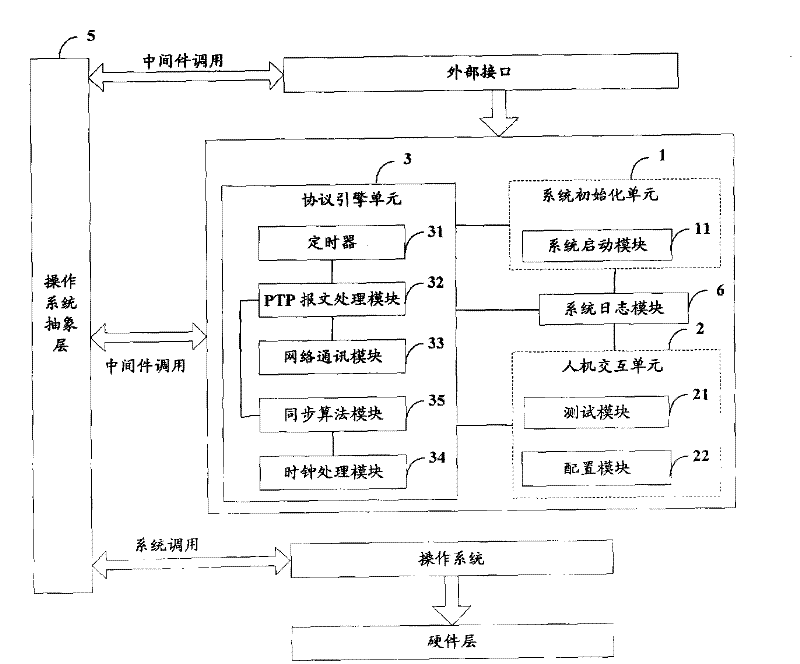

Realizing device of accurate time synchronization protocol

InactiveCN102447553AAchieve high-precision synchronizationResolve out of syncSynchronising arrangementCommunication unitNetwork clock

The invention is applicable in the technical field of network communication, and provides a realizing device of accurate time synchronization protocol, the device comprises a system initialization unit, initializing the realizing device of PTP (precision time protocol), preparing for running of PTP(precision time protocol); a human-computer interaction unit, providing one or more interactive interfaces, providing interact between users and the realizing device of the PTP(precision time protocol); a protocol engine unit, running PTP(precision time protocol); a hardware communication unit, stamping time for all PTP(precision time protocol) messages of engine unit organization of the protocol , transmitting the PTP(precision time protocol) messages with stamp between the master clock device and the vice clock device. The invention of realizing device of PTP(precision time protocol) runs the PTP(precision time protocol) in the network, realizing high-precision synchronization of the network clock, and solving all kinds of problems caused by error of clock synchronization or asynchronization in the current industrial control.

Owner:EVOC INTELLIGENT TECH

Method and device for achieving clock time synchronization

ActiveCN103888237AIncrease reflectionHigh synchronization accuracySynchronising arrangementClock timeTimestamp

The invention discloses a method and device for achieving clock time synchronization, and relates to the Ethernet technology. The method comprises the steps of estimating the clock jitter and the clock frequency deviation with the difference of sending and receiving timestamp of a synchronous message packet and the difference of sending and receiving timestamp of a response message packet in a precision time protocol (PTP) message packet as observed values respectively to obtain the phase difference of a master clock and a slave clock, and carrying out the synchronization adjustment on the slave clock according to the estimated phase difference. The invention further discloses the device for achieving the clock time synchronization. According to the technical scheme, the state quantity is obtained by calculating measuring values respectively based on the kalman filtering algorithm and the combination (O+D and O-D) of the phase difference and the path delay, the estimated value for the clock synchronization phase difference is obviously far more superior to the estimated value, worked out through the single measuring value of the phase difference serving as the state value, for the clock synchronization phase difference , the phase difference can be reflected better and the synchronous precision between the master clock and the slave clock is greatly improved.

Owner:RAISECOM TECH

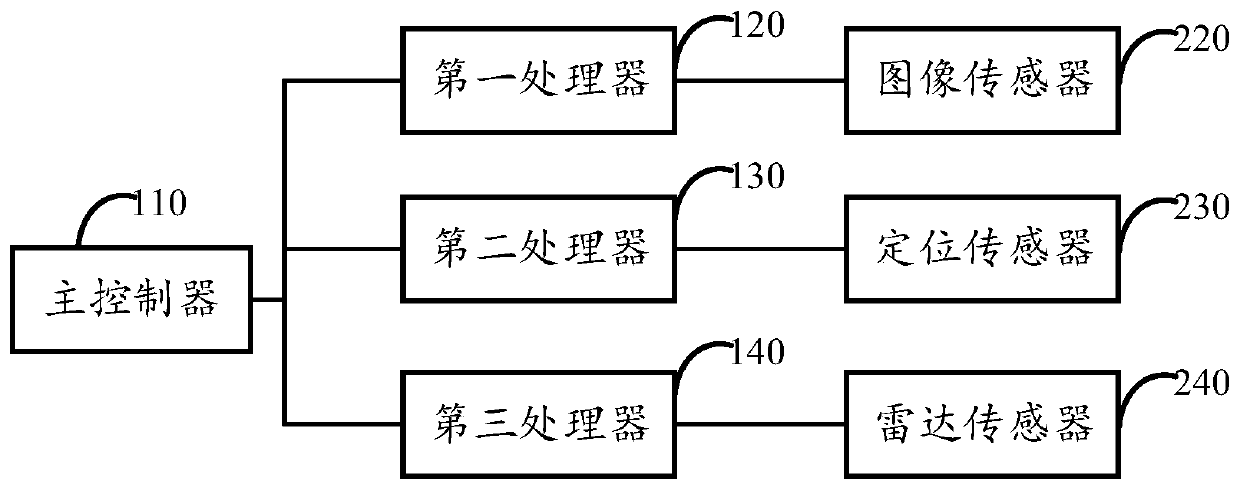

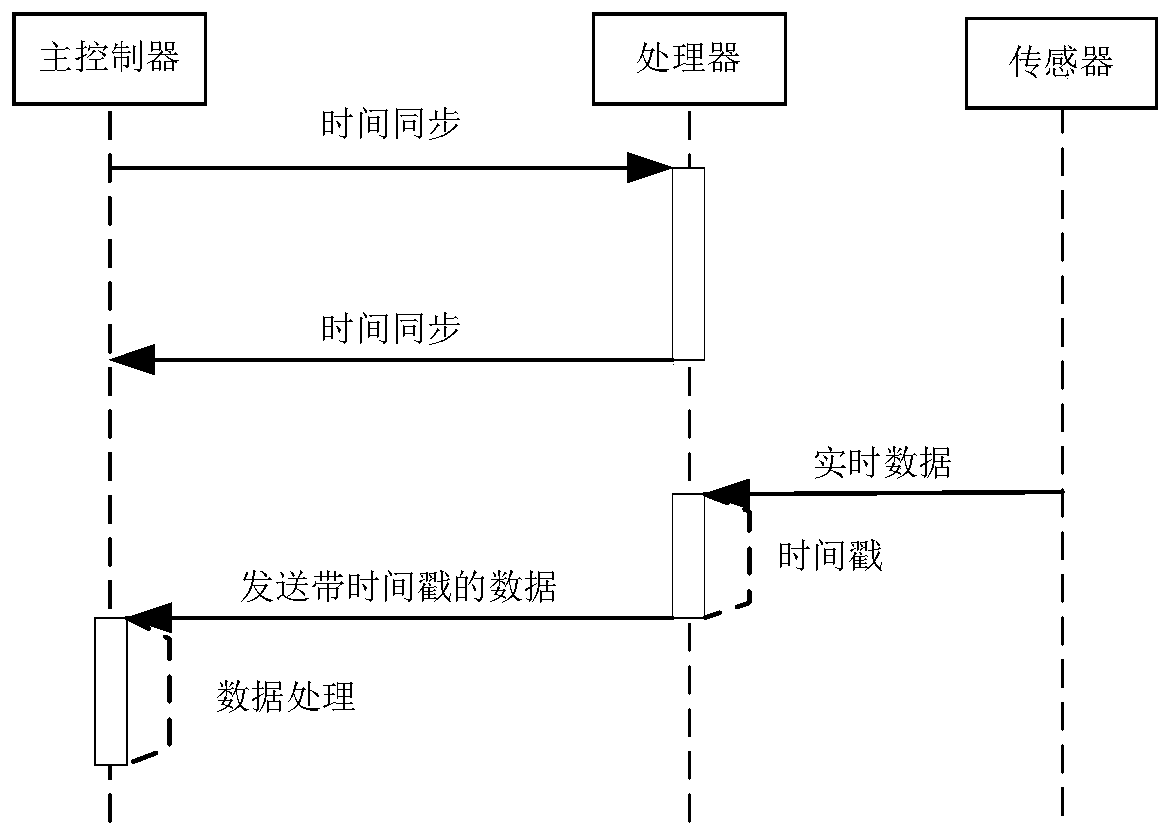

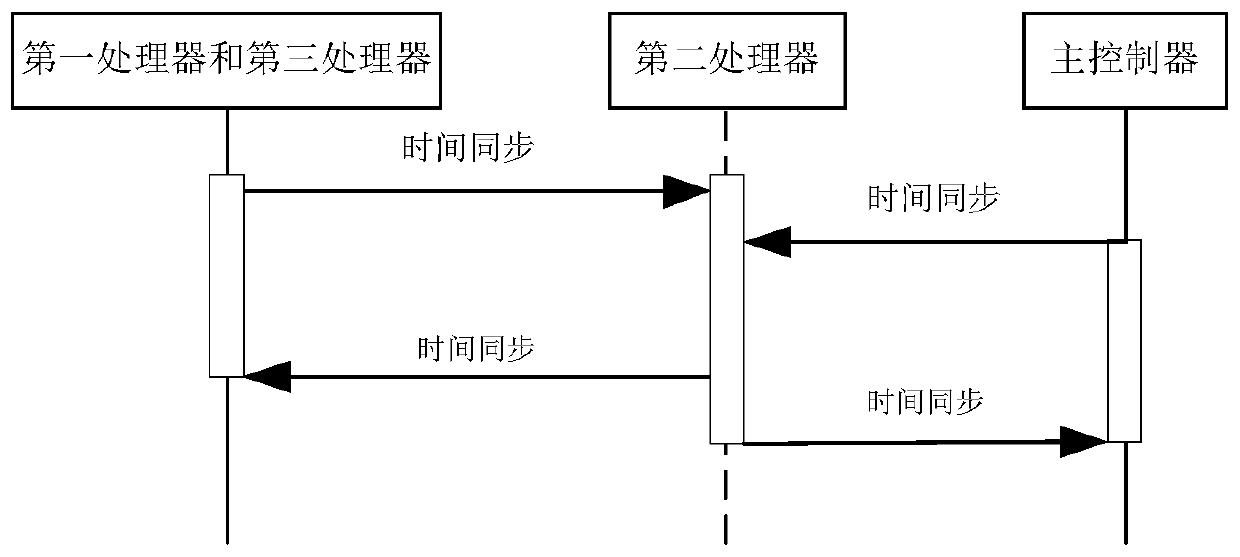

Vehicle-mounted terminal system and synchronous data acquisition method and device

ActiveCN109905194AStrong timestamp consistencyStrong consistencyTime-division multiplexTimestampRadar

The embodiment of the invention discloses a vehicle-mounted terminal system and a synchronous data acquisition method and device. In the system, an image sensor, a positioning sensor and a radar sensor acquire data according to associated moments; The first processor, the second processor and the third processor are used for respectively acquiring data acquired by a sensor connected with the firstprocessor, the second processor and the third processor, respectively determining timestamps of the acquired data, and respectively sending the acquired data and the corresponding timestamps to the main controller; The method comprises the following steps of: acquiring data by each sensor according to mutually associated moments; wherein the main controller or the second processor, using the first processor and the third processor as to-be-time-service equipment, and adjusting the system time of the to-be-time-service equipment according to the interaction information with the time service equipment on the basis of a precision time protocol (PTP), so that the clock of the to-be-time-service equipment is synchronous with the clock of the time service equipment; and enabling the main controller or the second processor to determine whether the main controller or the second processor is time service equipment according to a preset signal of the positioning sensor. By applying the scheme provided by the embodiment of the invention, the data with higher time synchronization precision of each sensor can be obtained.

Owner:MOMENTA SUZHOU TECH CO LTD

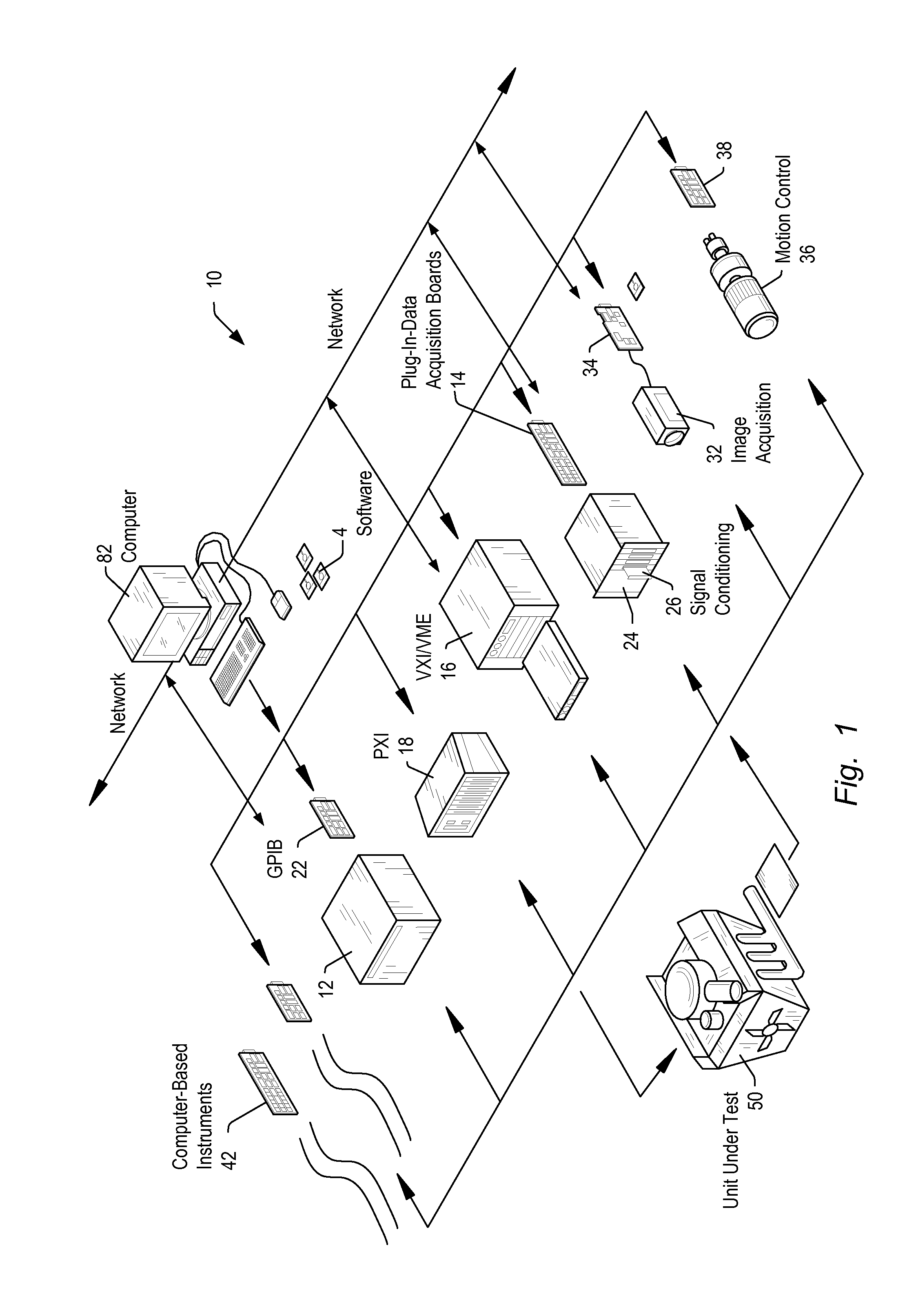

Cross Controller Clock Synchronization

ActiveUS20110276820A1Easy to controlSynchronisation information channelsTime-division multiplexData acquisitionEngineering

A system may include a plurality of subsystems, e.g. instrumentation units housed in separate chassis, each chassis including multiple instrumentation devices, e.g. data acquisition cards. Each subsystem may generate a local reference clock, which may be phase aligned and locked with respect to one or more similar reference clocks of other subsystems, via a high-level precision time protocol (PTP). Each instrumentation device within a given subsystem may generate its own sample clock based on the local reference clock, and may generate its own trigger clock based on its own sample clock. All trigger clocks may be synchronized with respect to each other through a future time event issued using the PTP, and each instrumentation device may then use its trigger clock to synchronize any received trigger pulses, which may also be issued through future time events using the PTP. This results in synchronizing the received triggers across all participating instrumentation devices across all participating subsystems, ensuring that data acquisition is properly synchronized across the multiple subsystems.

Owner:NATIONAL INSTRUMENTS

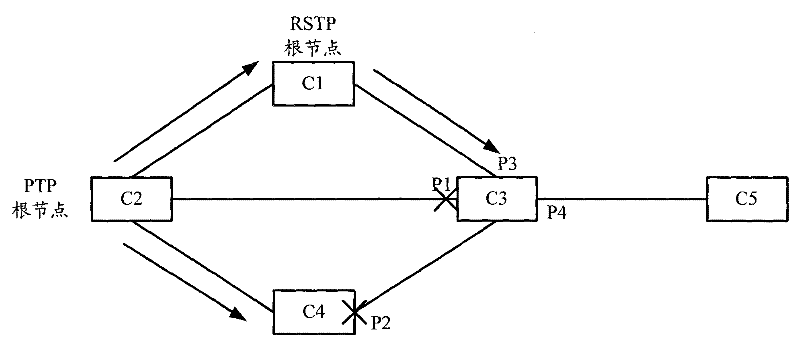

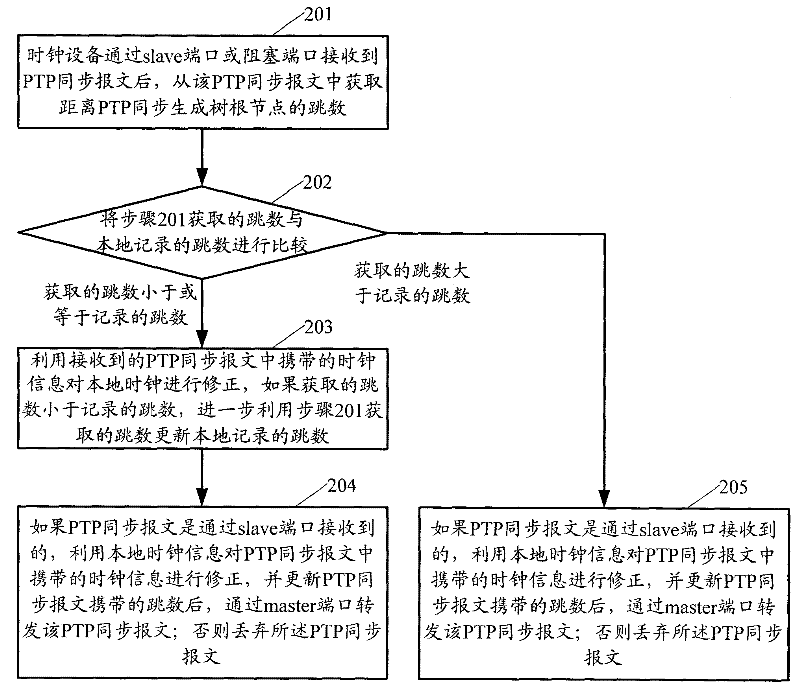

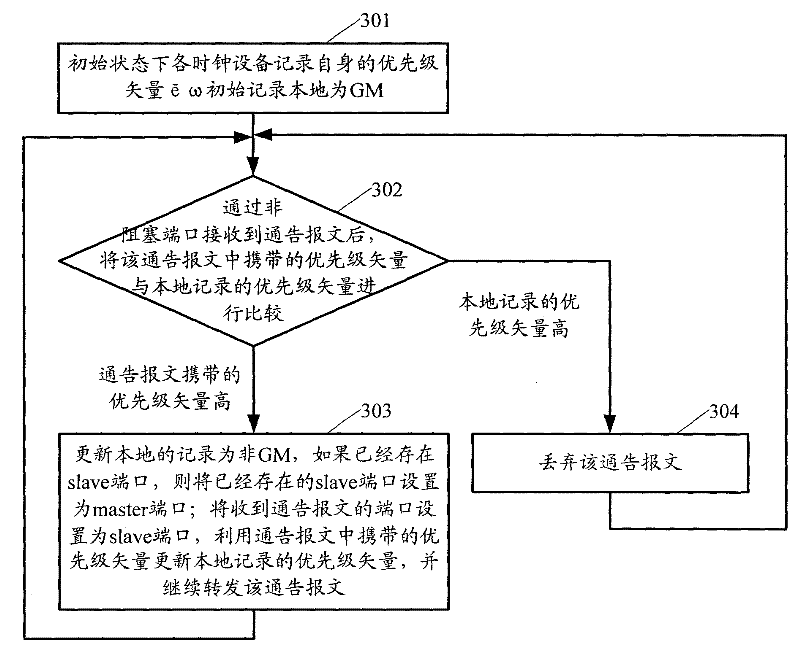

Time synchronization method and clock device

ActiveCN102195766AReduce error accumulationHigh precisionSynchronising arrangementReal-time computingPrecision Time Protocol

The invention provides a time synchronization method and a clock device, the limitation of a block port on a precision time protocol (PTP) synchronization message is cancelled, a local clock is amended according to the PTP synchronization message transmitted from an optimal path, as the hop count of routing of the PTP synchronization message is minimal, the cumulative error is also minimal and the time synchronization precision is further improved. Furthermore, when the PTP synchronization message is received through a slave port and the clock device has a master port, after clock information carried in the PTP message is amended, the master port is used for forwarding the PTP synchronization message so as to enable the follow-up clock device to conveniently perform precision time synchronization.

Owner:NEW H3C TECH CO LTD

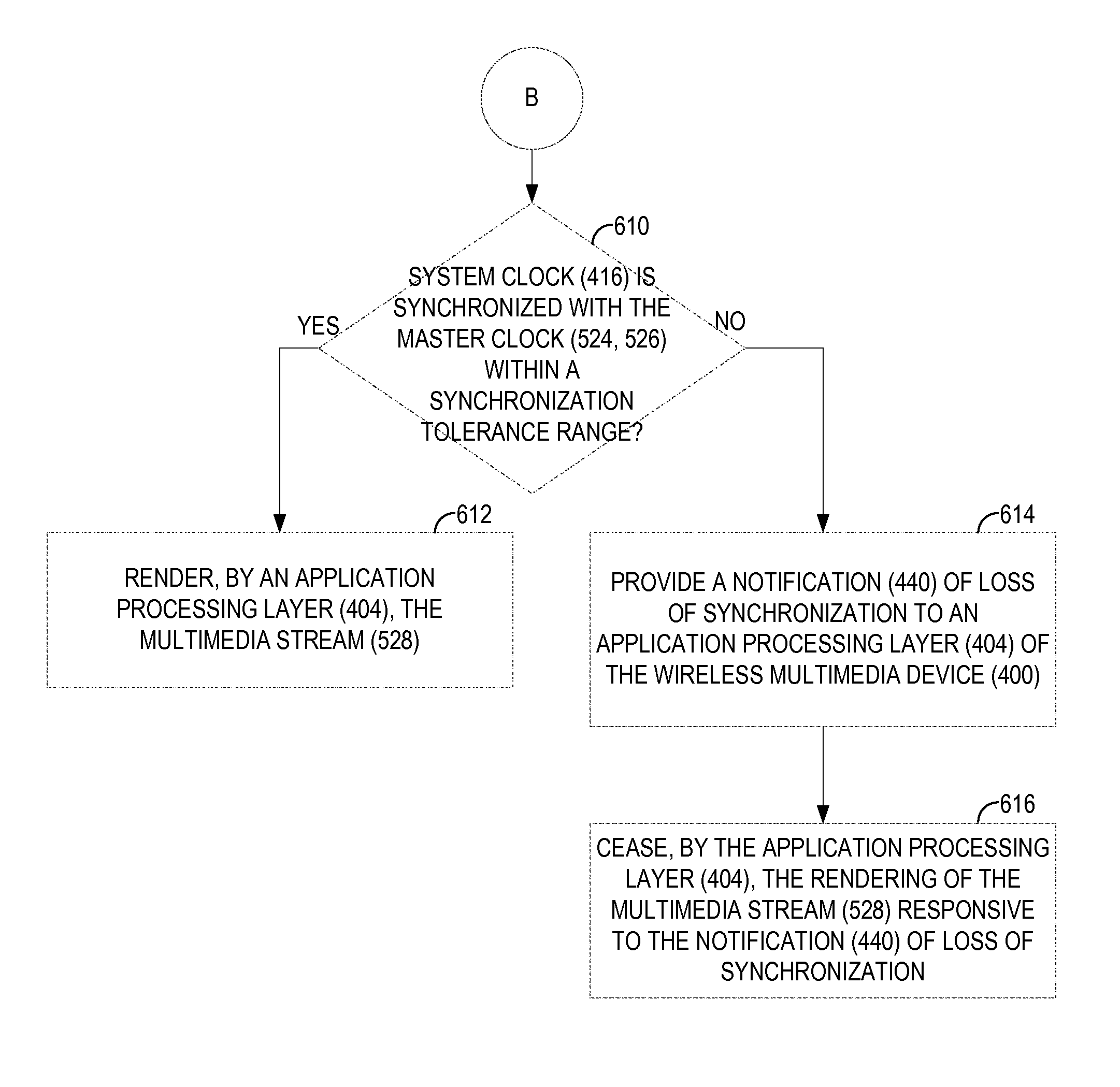

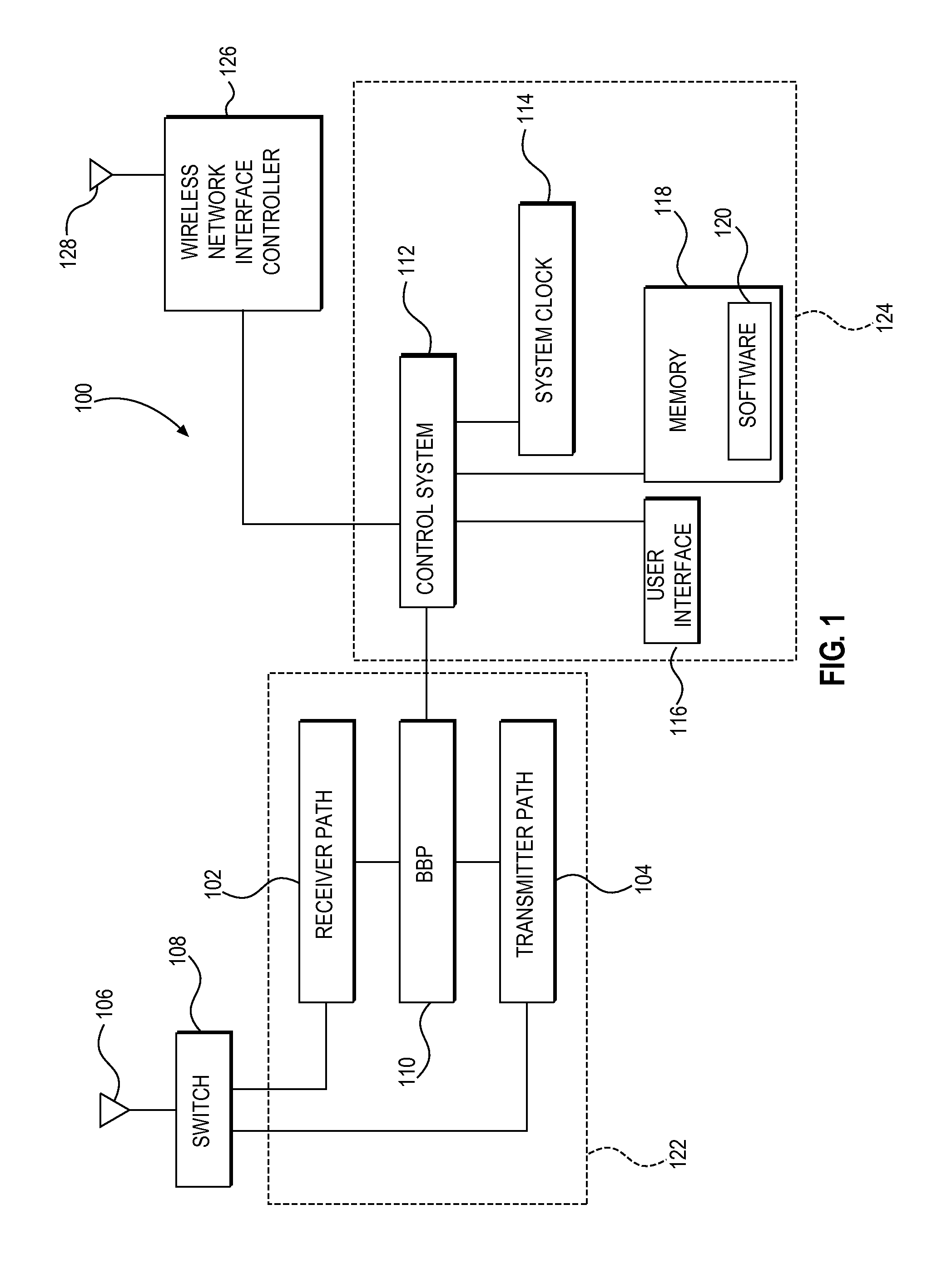

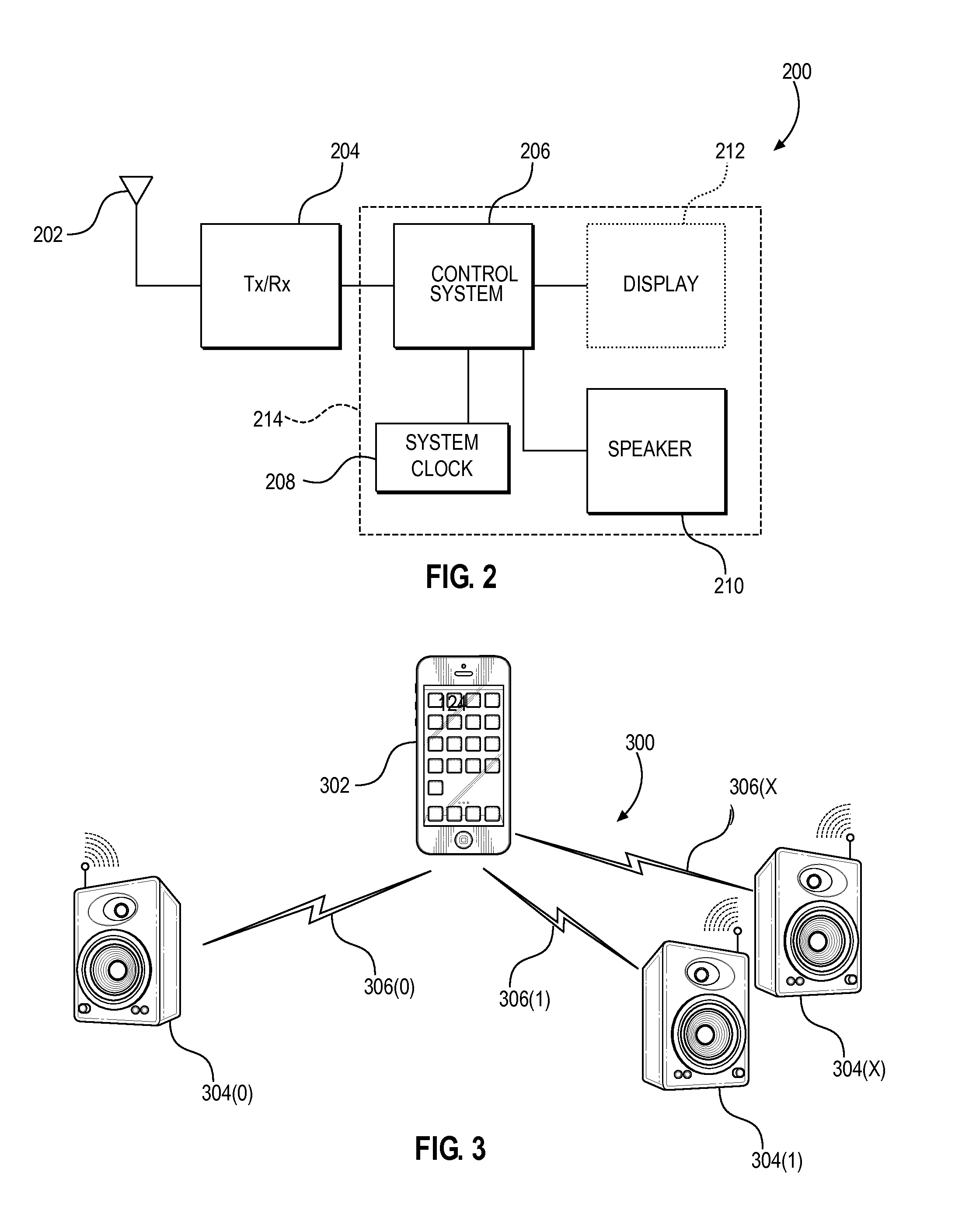

Providing precision timing protocol (PTP) timing and clock synchronization for wireless multimedia devices

InactiveUS20170055235A1Synchronisation arrangementTime-division multiplexControl systemPrecision timing protocol

Providing Precision Timing Protocol (PTP) timing and clock synchronization for wireless multimedia devices is disclosed. In one aspect, a primary wireless multimedia device comprising a timing synchronization control system is provided. The timing synchronization control system is configured to apply a PTP Best-Master-Clock (BMC) algorithm logic to select a master clock from among a system clock of the primary wireless multimedia device, one of one or more connected wireless multimedia devices, or one of one or more external nodes. If the timing synchronization control system selects the system clock of the primary wireless multimedia device, a clock signal of the system clock is provided to the connected wireless multimedia devices as the master clock. If the timing synchronization control system selects a connected wireless multimedia device or an external node as the master clock, the timing synchronization control system synchronizes the system clock with the master clock.

Owner:QUALCOMM INC