Method and device for achieving clock time synchronization

A clock time, clock technology, applied in the field of Ethernet, can solve the problems of inconsistency and error of two-way delay

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

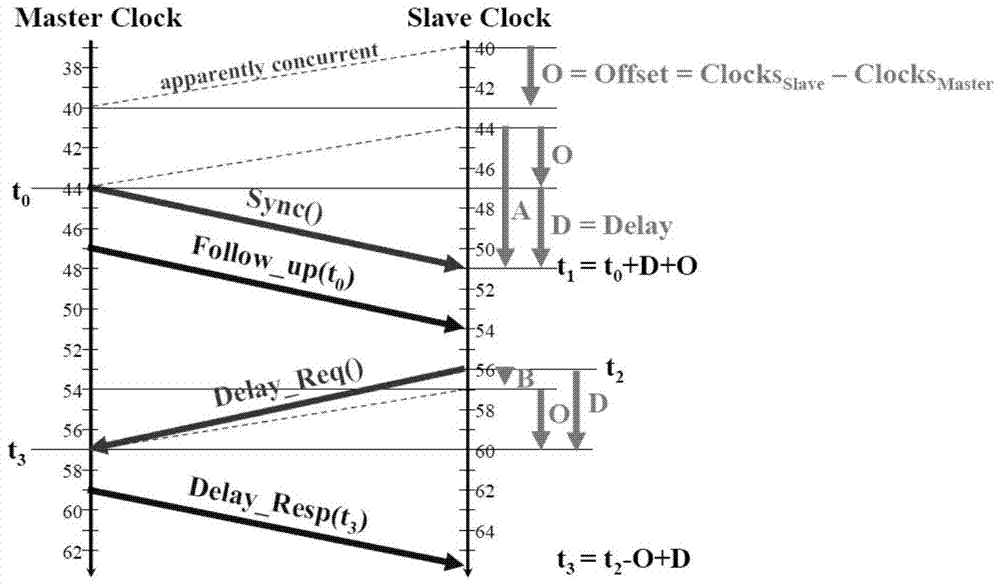

Problems solved by technology

Method used

Image

Examples

Embodiment 1

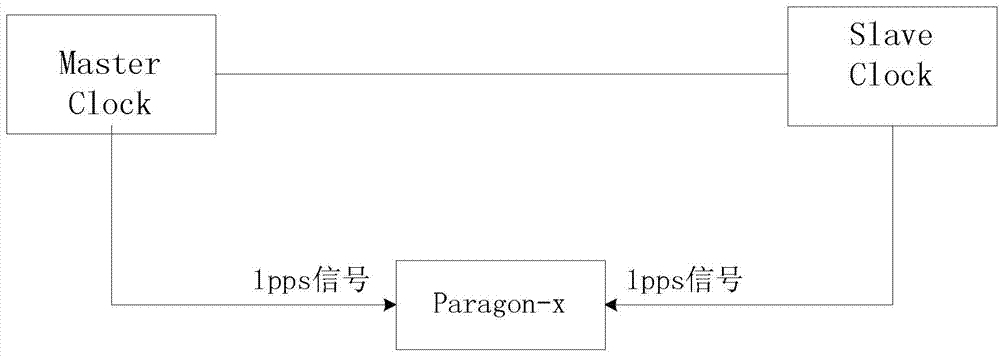

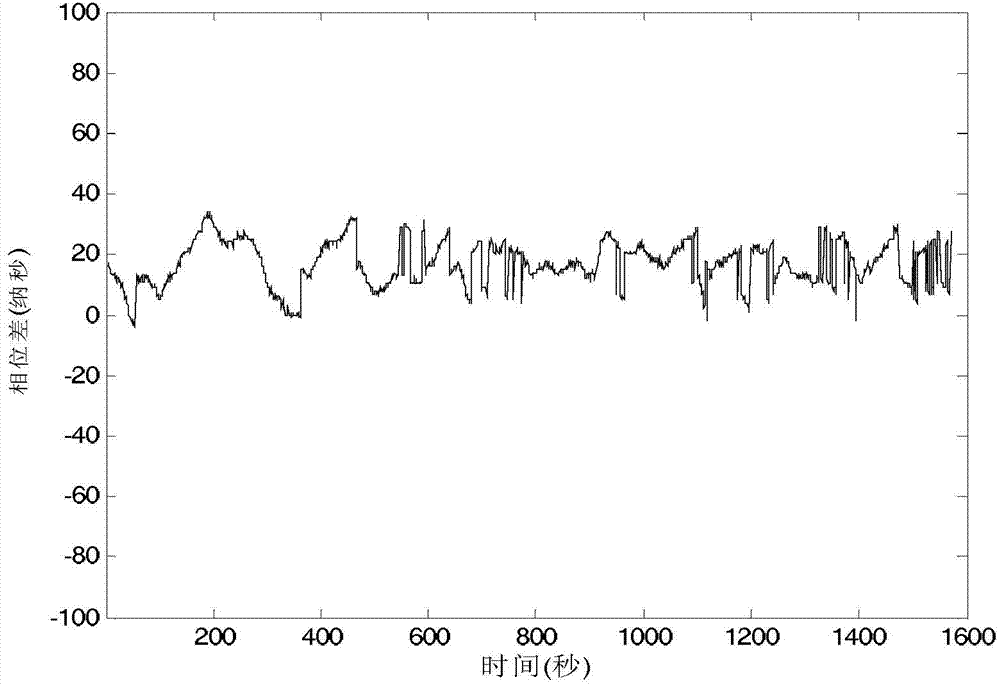

[0056] The inventor realizes the purpose of this application by using the Kalman filter algorithm, which is based on the statistical law of noise and estimates the current state of time synchronization between Master Clock and Slave Clock according to the principle of minimum estimation error, so as to be used for clock synchronization adjustment. It depends on the test model such as figure 2 shown. Specifically, the Kalman filter algorithm uses the state equation to determine the time synchronization state of the Master Clock and Slave Clock (see equation (1)) and the measurement equation to determine the measurement vector of the time synchronization state of the Master Clock and Slave Clock (see equation (2)) to realise:

[0057] X(k)=F(k,k-1)X(k-1)+W(k) (1)

[0058] Y(k)=HX(k-1)+V(k) (2)

[0059] Among them, X(k) is the state vector;

[0060] Y(k) is the measurement vector of the state;

[0061] F(k, k-1) is the transition matrix from the k-1th time synchronization s...

Embodiment 2

[0104] This embodiment provides a device for implementing clock time synchronization, which estimates the current time synchronization state of the Master Clock and Slave Clock based on the statistical law of noise and the principle of minimum estimation error, so as to be used for clock synchronization adjustment. The device includes at least the following modules:

[0105] The first module uses the difference between the sending and receiving timestamps of the synchronization message packet and the response message packet in the PTP message packet as the observed value to estimate the clock deviation, clock frequency deviation and aging rate, and obtain the phase difference between the master and slave clocks ;

[0106] In another embodiment, with the same basic structure of the above-mentioned device, the first module uses the difference between the synchronization message packet in the PTP message packet and the sending and receiving time stamp of the response message pack...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More