SOPC (System on a Programmable Chip) networking based sub-microsecond level clock synchronizing method and system

A clock synchronization, microsecond-level technology, applied in the field of network communication, can solve the problem of few method designs, achieve the effect of simplifying node equipment design, ensuring accuracy requirements, and improving synchronization accuracy

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0030] In order to make the technical problems, technical solutions and beneficial effects solved by the present invention clearer, the present invention will be further described in detail below in conjunction with the accompanying drawings and embodiments. It should be understood that the specific embodiments described here are only used to explain the present invention, not to limit the present invention.

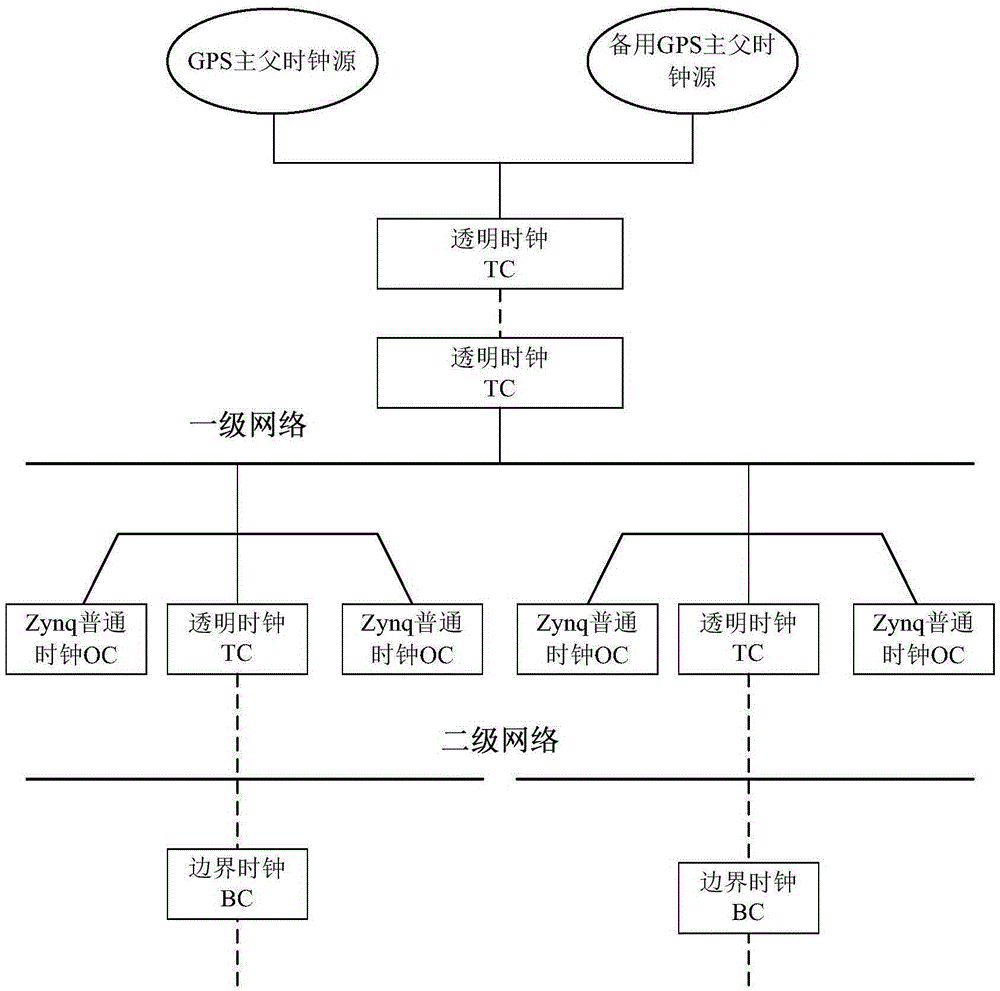

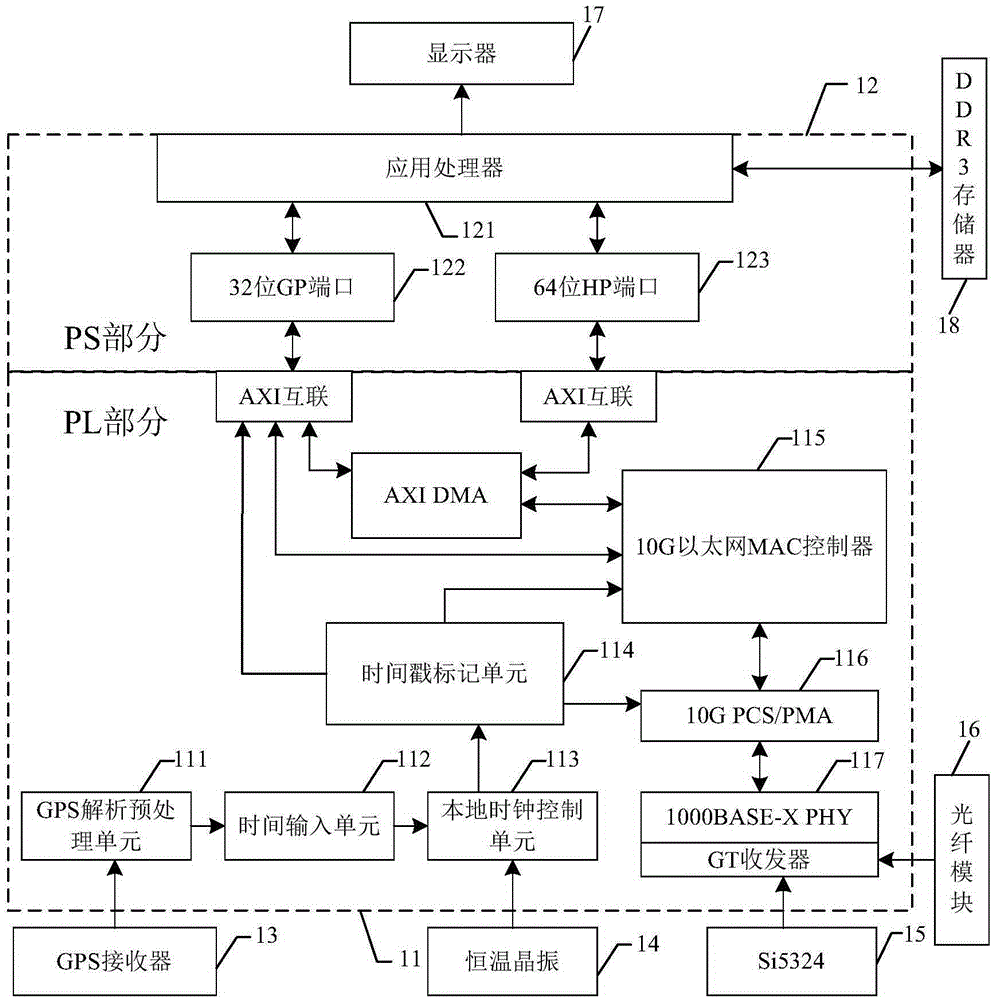

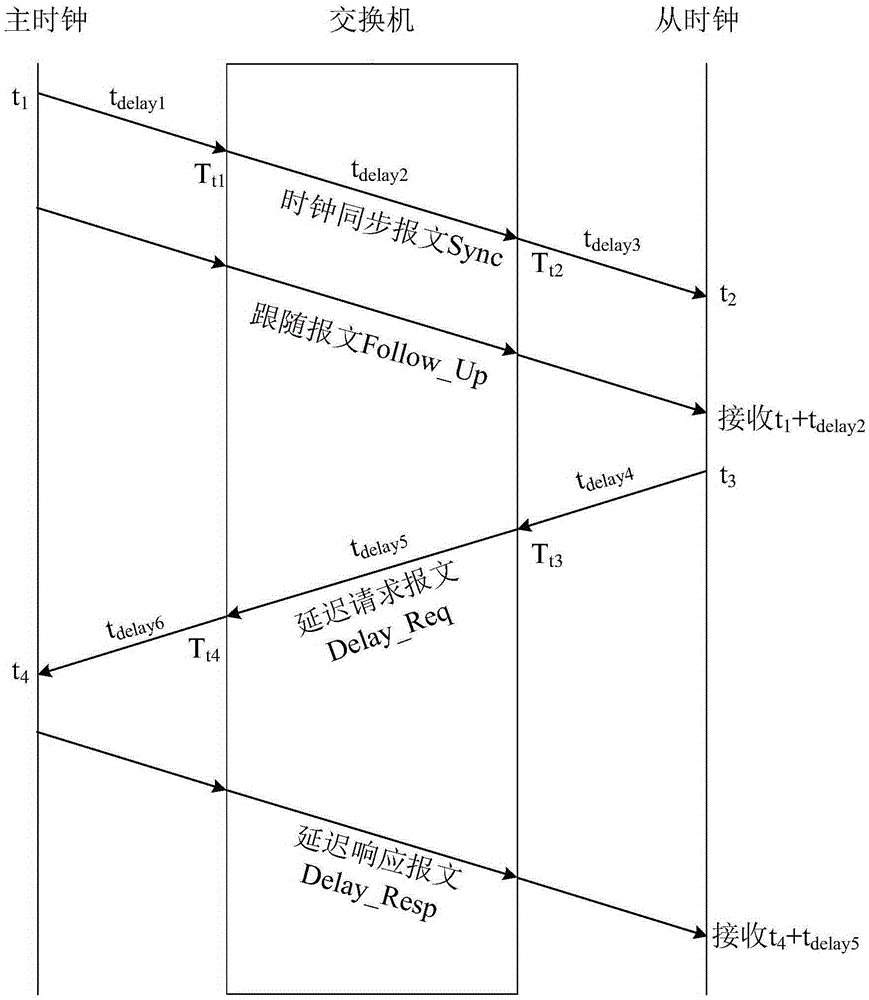

[0031] For the problems existing in the prior art, the present invention proposes a detailed design scheme for the clock synchronization system of a large-scale control system, based on the Zynq platform of the on-chip programmable system SOPC, the design of the clock synchronization module using the PTP protocol provides specific The implementation plan supports Gigabit Ethernet and optical fiber transmission. At the same time, the non-deterministic network delay is corrected, and the crystal oscillator drift of the slave clock node is also frequency compensated to achie...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More