Wafer mirror surface chamfering method, wafer manufacturing method, and wafer

A wafer and chamfering technology, applied in manufacturing tools, semiconductor/solid-state device manufacturing, machine tools suitable for grinding workpiece edges, etc., can solve problems such as dusting, and achieve the effect of suppressing edges

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment

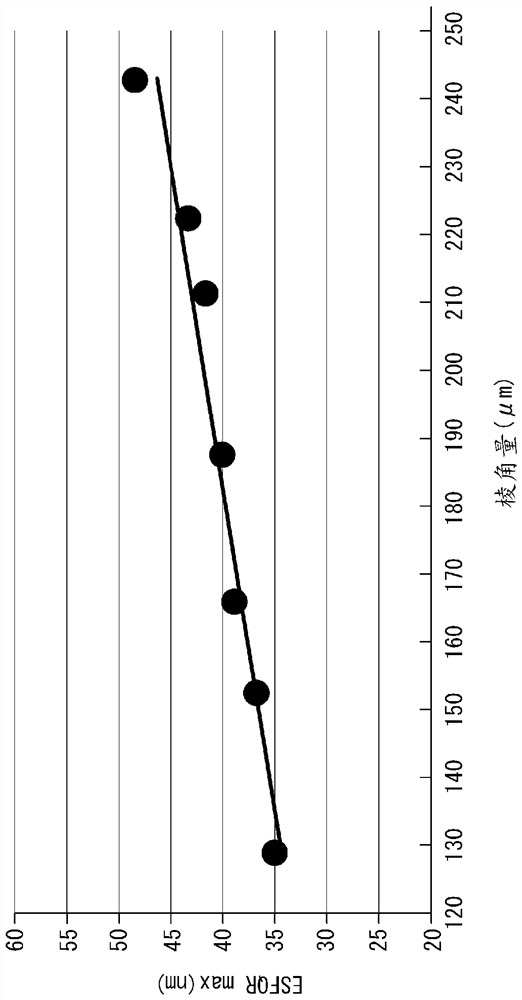

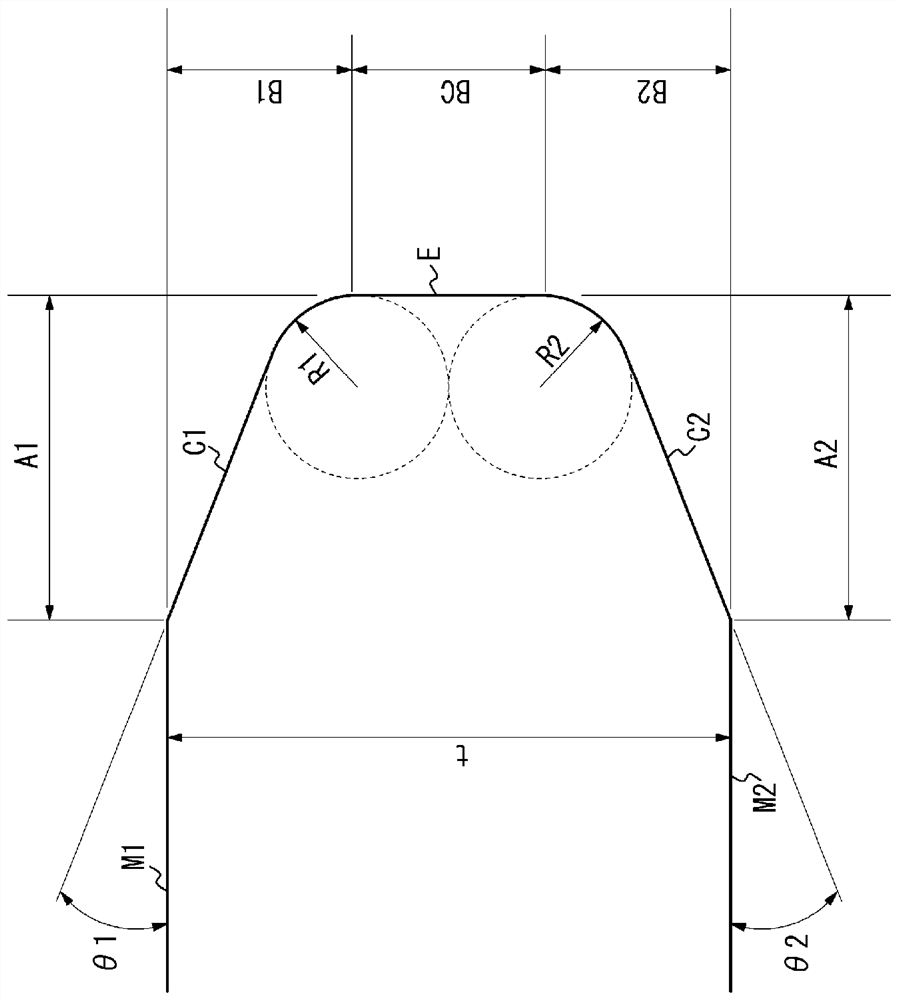

[0054] (Invention Example 1)

[0055] For a silicon wafer cut from a single crystal silicon ingot: 300 mm in diameter, chamfering, polishing, etching, and double-sided grinding were performed in this order to obtain 5 wafers with figure 1 A silicon wafer of the shape shown. Here, in the chamfering of the wafer, the target values of θ1 and θ2 were set to 22° by a chamfering processing apparatus using a #2000 resin grindstone. Also, t=776 μm, A1=240 μm, A2=240 μm, B1=213 μm, B2=213 μm, BC=350 μm, R1=230 μm, R2=230 μm.

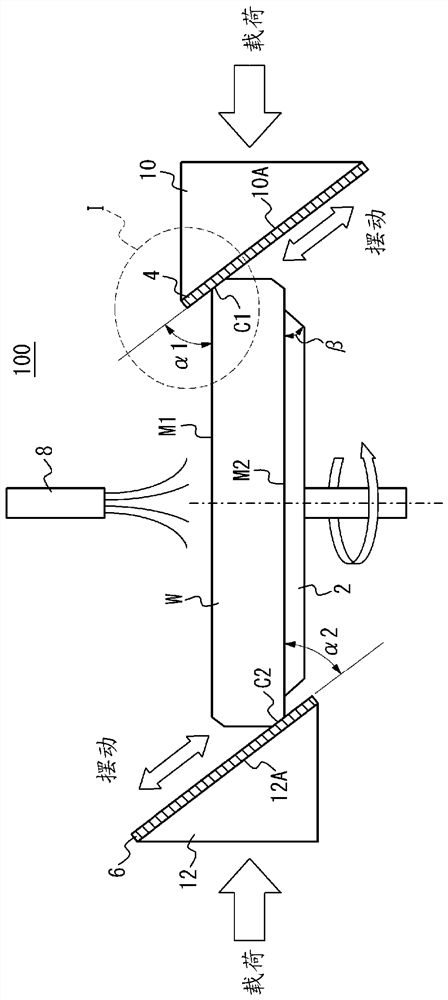

[0056] Next, use Figure 2A The shown mirror chamfering apparatus performs mirror chamfering on each silicon wafer under the following conditions.

[0057] α1, α2: 22°

[0058] β: 20°

[0059] Types of polishing pads 1 and 2: Polyurethane non-woven fabric

[0060] Compression rate of the first and second polishing pads: 5%

[0061] The thickness of the first and second polishing pads: 1.5mm

[0062] Swing speed of the 1st and 2nd polishing pad installat...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More