Method for establishing time sequence diagram in parallel based on geometrical information

A technology of geometric information and timing diagrams, applied in special data processing applications, instruments, electrical digital data processing, etc., can solve long-term problems and achieve the effect of shortening time

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0034] The preferred embodiments of the present invention will be described below in conjunction with the accompanying drawings. It should be understood that the preferred embodiments described here are only used to illustrate and explain the present invention, and are not intended to limit the present invention.

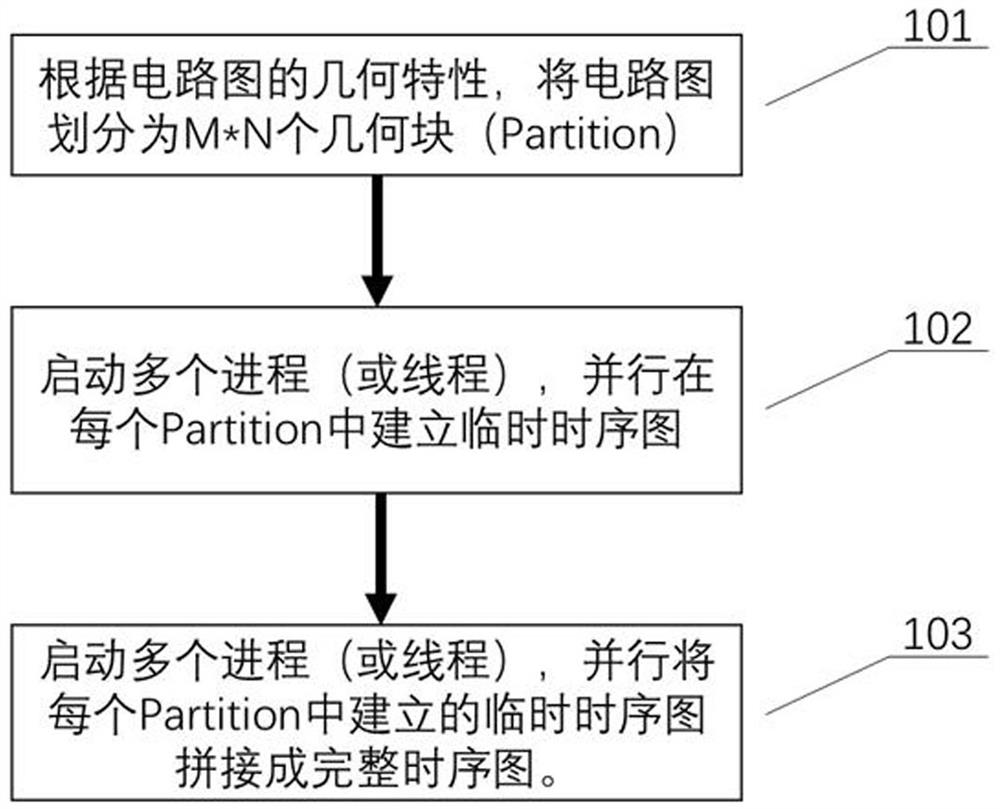

[0035] figure 1 For the flow chart of the method for establishing a sequence diagram in parallel based on geometric information according to the present invention, the following will refer to figure 1 , to describe in detail the method for building sequence diagrams in parallel based on geometric information in the present invention.

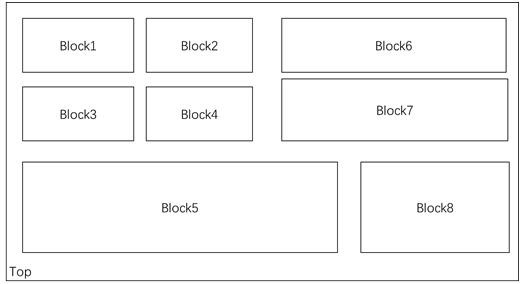

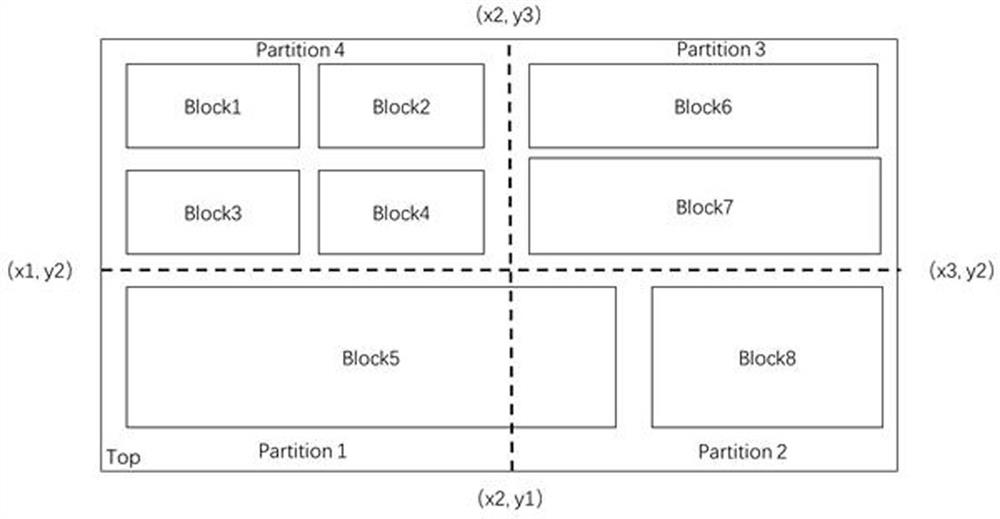

[0036] First, in step 101, the circuit diagram is divided into M*N geometric blocks according to the geometric characteristics of the circuit diagram.

[0037] In this embodiment, the user can specify the division method of the geometric block; estimate the division method of the geometric block through the geometric information of t...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More