High-speed parallel DDC and FIR filtering processing method based on FPGA

A filter processing, high-speed technology, applied in the field of signal processing, can solve problems such as inability to process data signals, and achieve the effect of improving efficiency

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0029] Below, the present invention will be further described in conjunction with the accompanying drawings and specific implementation methods. It should be noted that, under the premise of not conflicting, the various embodiments described below or the technical features can be combined arbitrarily to form new embodiments. .

[0030] The present invention provides a preferred embodiment, FPGA-based high-speed parallel DDC and FIR filtering processing architecture, applied to FPGA processors, can make FPGA processors realize the processing of data signals with arbitrary data sampling rates, and solve the problems of the prior art Due to the limitations of the FPGA processor's own internal hardware, it cannot handle the processing of data signals with high data sampling rates. More preferably, this embodiment is especially suitable for processing echo signals of radar equipment with a high data sampling rate.

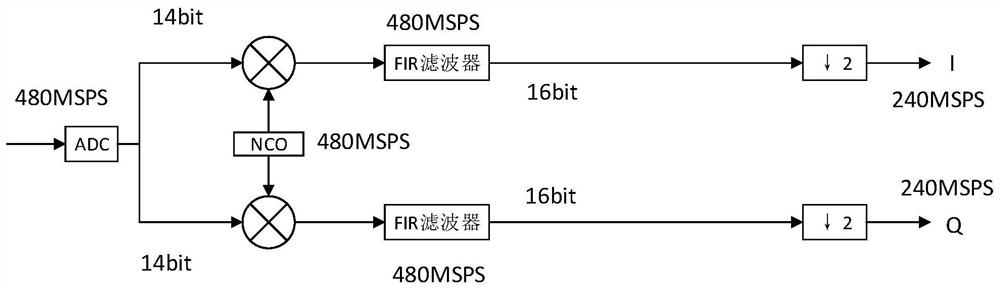

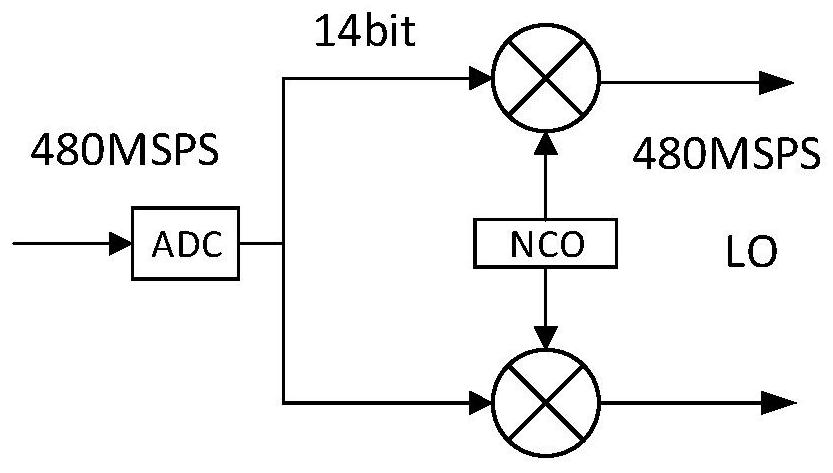

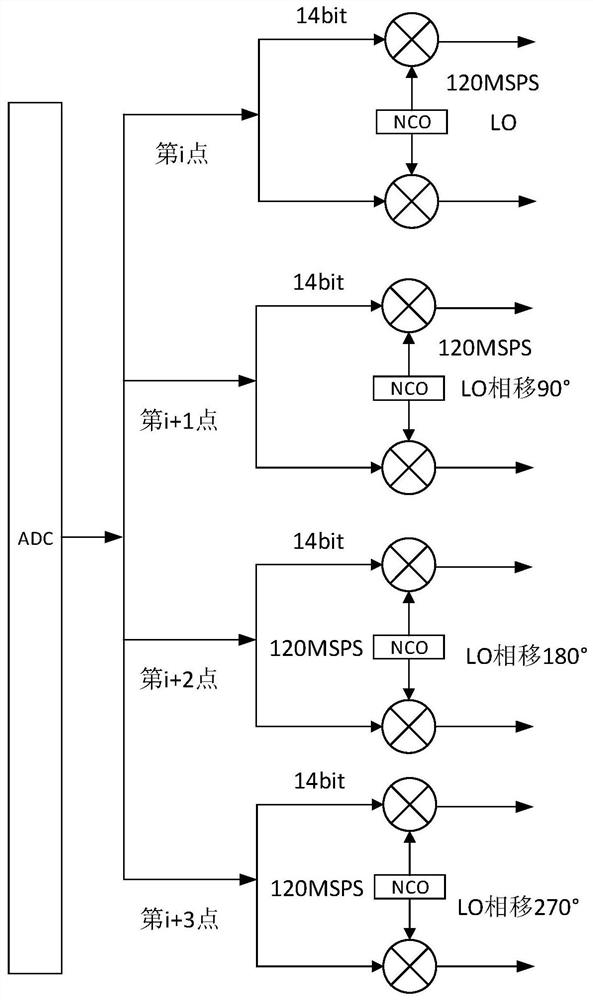

[0031] In order to better illustrate the FGPA-based high-speed pa...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More