Verification environment control method and device, platform, equipment and storage medium

A technology for verifying the environment and control devices, applied in hardware monitoring, instruments, electrical digital data processing, etc., can solve problems such as waste, affecting verification efficiency, and inability to quickly reproduce, and achieve the effect of reducing time loss and speeding up iterations

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0035] The technical solutions in the embodiments of the present application will be described below with reference to the drawings in the embodiments of the present application. In the description of the present application, the terms "first", "second" and the like are only used for distinguishing descriptions, and cannot be understood as indicating or implying relative importance.

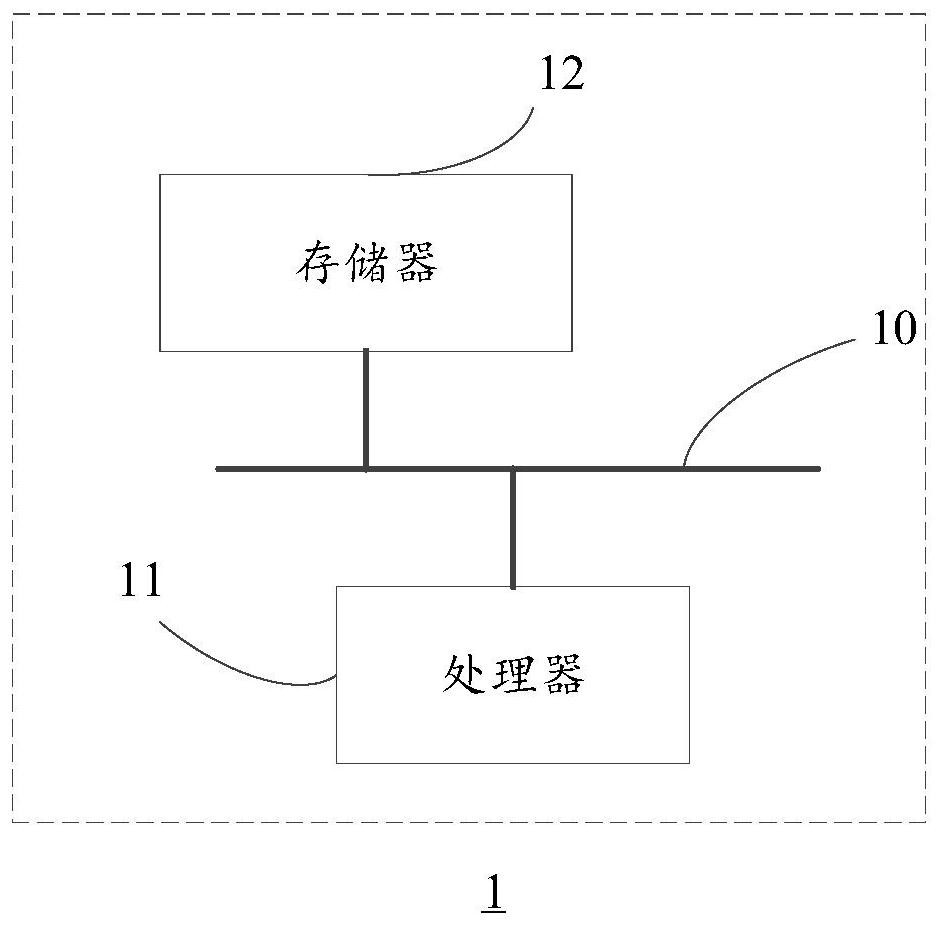

[0036] Such as figure 1 As shown, this embodiment provides an electronic device 1, including: at least one processor 11 and a memory 12, figure 1Take a processor as an example. Processor 11 and memory 12 are connected via bus 10 . The memory 12 stores instructions that can be executed by the processor 11, and the instructions are executed by the processor 11, so that the electronic device 1 can execute all or part of the process of the method in the following embodiments, so as to perform fault monitoring on the simulation operation of the verification environment and control.

[0037] In one...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com