Multi-channel DMA interactive design method based on PCIe bus

An interactive design, multi-channel technology, applied in the field of data transmission, can solve problems such as inflexibility, avoid stalls or crashes, and improve the efficiency of bus transmission

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0024] In order to make the purpose, technical solution and advantages of the present invention clearer, the specific implementation manners of the present invention will be further described in detail below in conjunction with the accompanying drawings and embodiments.

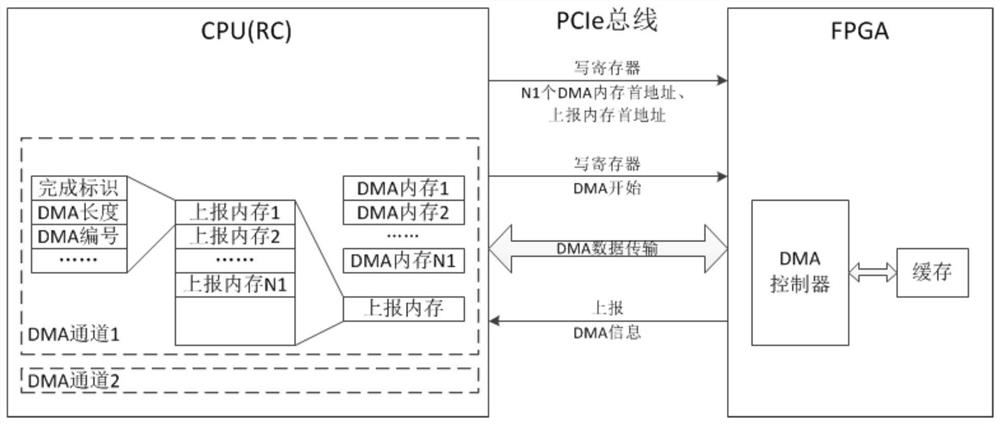

[0025] like figure 2 As shown, the main idea of the present invention is to allocate N1 memory blocks of 4MB size in the memory for use in turn as DMA memory space, and allocate one memory block of 4MB size as the report memory space for the interaction of DMA packet information, and report N1 small block spaces are sequentially divided in the memory space as reporting memory spaces corresponding to the N1 DMA memory spaces. The number N1 of the DMA memory space is set by the application software to the driver software, and the value of N1 is written into the corresponding register of the FPGA. During specific implementation, N1 can be set to 128 at most. After a DMA transfer is completed, the FPGA repor...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More