Multiprocessor peripheral multiplexing circuit and multiplexing method thereof

A technology of multiple processors and multiplexing circuits, applied in the direction of electrical digital data processing, instruments, register devices, etc., can solve problems such as multiple processor multiplexing, and achieve the effect of avoiding conflicts

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

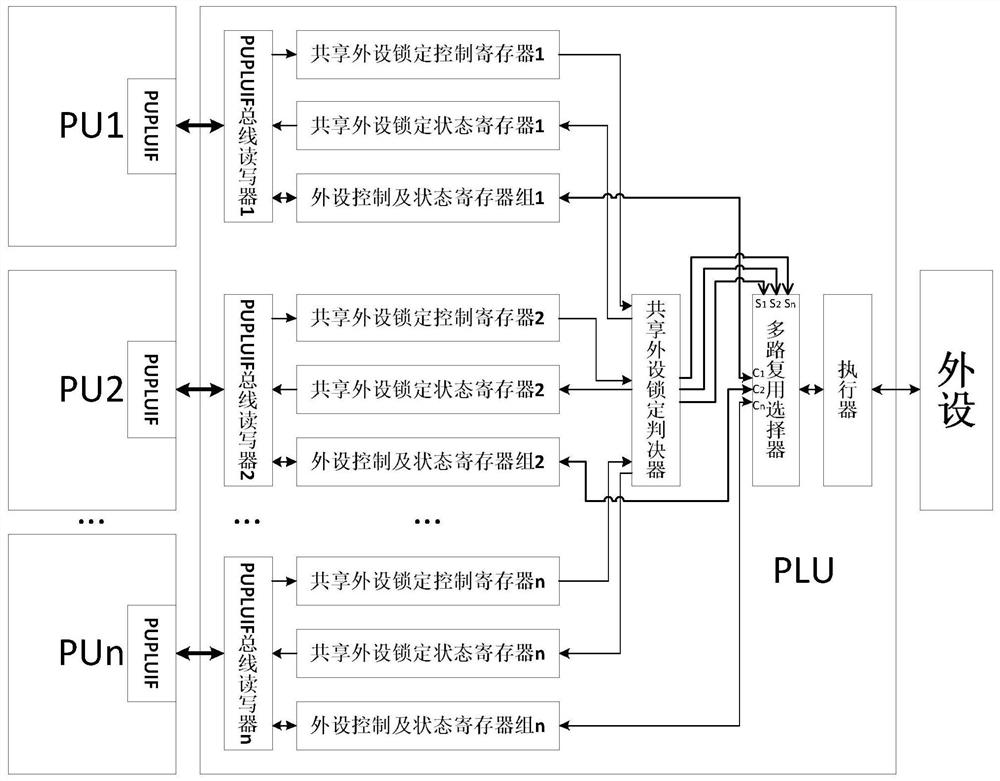

[0017] refer to figure 1 . In the exemplary preferred embodiment described below, a multiprocessor peripheral multiplexing circuit includes: a multiprocessor structure composed of programmable logic units PLU connected between n processing units PU1-PUn and peripherals , n processing units PU1~PUn correspond to the PUPLUIF bus reader-writer 1~PUPLUIF bus reader-writer n connected to the PLU, characterized in that: in the processing unit PLU, the PUPLUIF bus reader-writer 1-PUPLUIF bus reader-writer n are connected Corresponding to the shared peripheral lock control register, the shared peripheral lock status register and the peripheral control and status register group, wherein the shared peripheral lock control register and the shared peripheral lock status register are connected to the shared peripheral lock judger, the peripheral control and The state register group is connected to the multiplexing selector, and the multiplexing selector is connected in series with the act...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com