Automatic layout method and device based on Euler path algorithm

An Euler path and automatic layout technology, which is applied in computing, computer-aided design, CAD circuit design, etc., can solve the problem of low efficiency of integrated circuits, achieve the effect of automatic layout, reduce the area occupied by the layout, and reduce the time

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

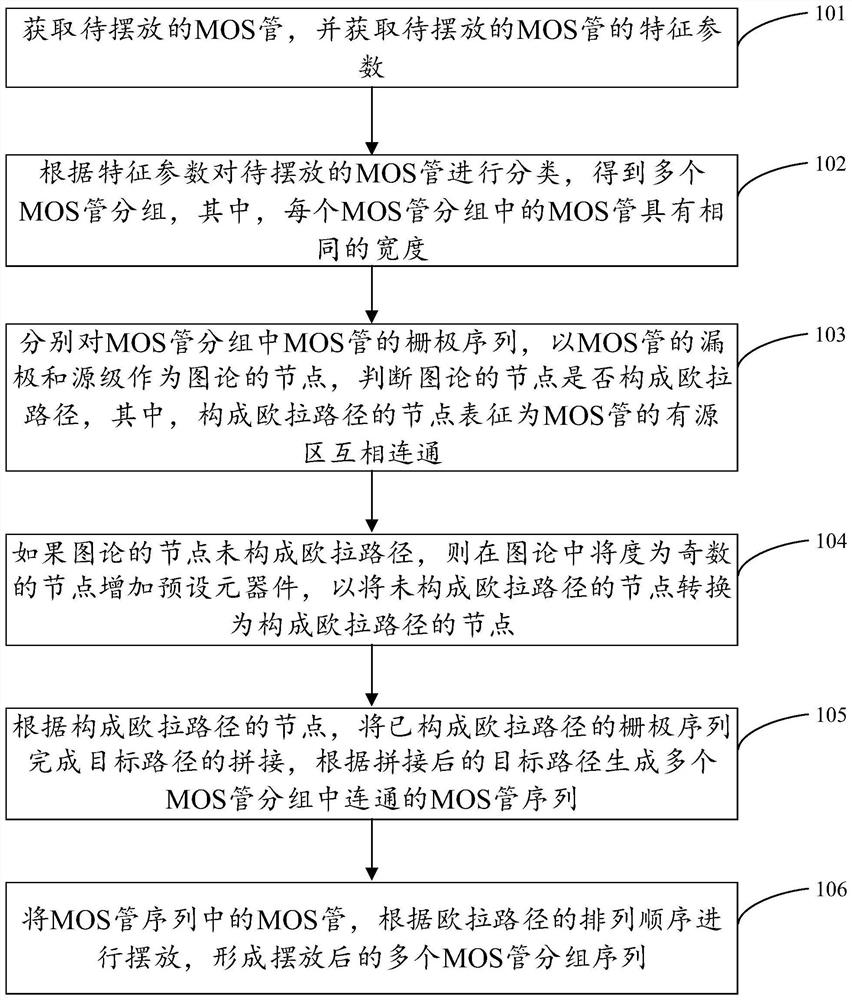

[0030] figure 1 It is a schematic flowchart of an automatic layout method based on the Euler path algorithm provided according to an embodiment of the present application, such as figure 1 As shown, can include:

[0031] Step 101 , acquiring the MOS tubes to be placed, and acquiring characteristic parameters of the MOS tubes to be placed.

[0032] Wherein, in the embodiment of the present application, the characteristic parameter of the MOS transistor may include: the gate width of the MOS transistor.

[0033] Step 102: Classify the MOS transistors to be placed according to the characteristic parameters to obtain multiple MOS transistor groups, wherein the MOS transistors in each MOS transistor group have the same width.

[0034] Wherein, in the embodiment of the present application, the above characteristic parameters of the MOS transistor may further include: a finger of the MOS transistor. And, in the embodiment of the present application, before classifying the MOS tran...

Embodiment 2

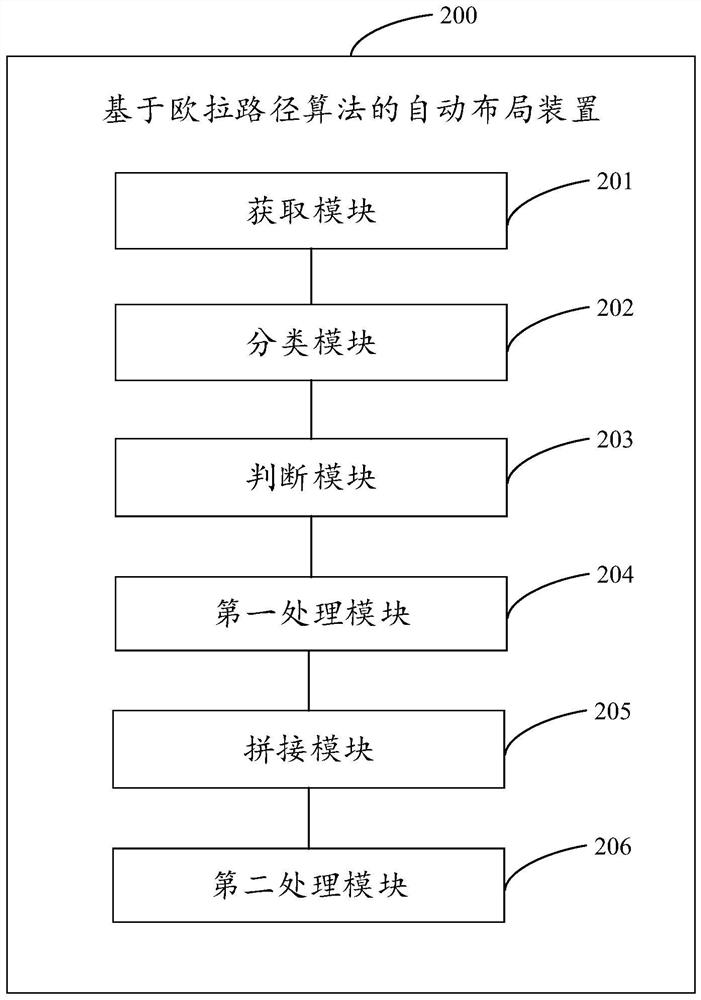

[0053] further, figure 2 It is a schematic structural diagram of an automatic layout device based on the Euler path algorithm provided according to an embodiment of the present application, as shown in figure 2 As shown, can include:

[0054] The obtaining module 201 is used to obtain the MOS tube to be placed, and obtain the characteristic parameters of the MOS tube to be placed;

[0055] The classification module 202 is used to classify the MOS transistors to be placed according to the characteristic parameters to obtain a plurality of MOS transistor groups, wherein the MOS transistors in each MOS transistor group have the same width;

[0056] The judging module 203 is used for respectively grouping the gate sequences of the MOS transistors in the MOS transistors, using the drain and source of the MOS transistors as the nodes of the graph theory, and judging whether the nodes of the graph theory constitute an Euler path. The nodes of the path are characterized by the int...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More