Automatic data layout method and device for heterogeneous fusion many-core architecture

A technology of automatic layout and data, applied in the computer field

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

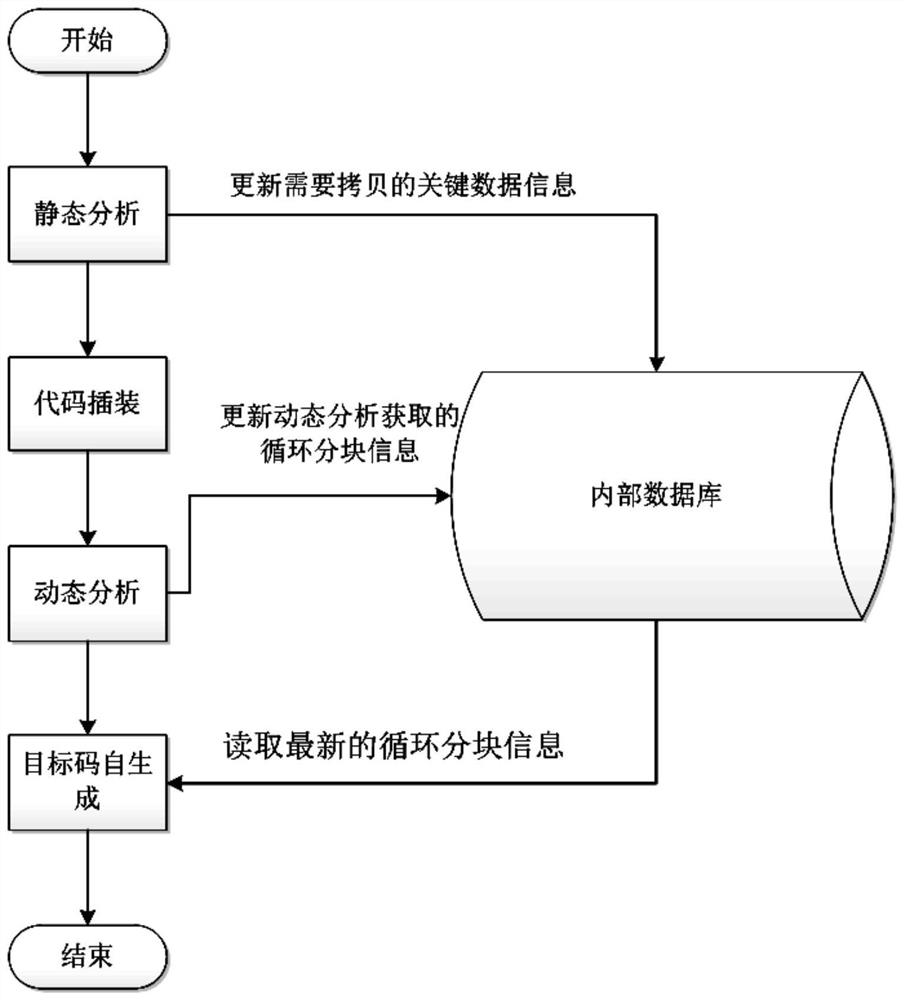

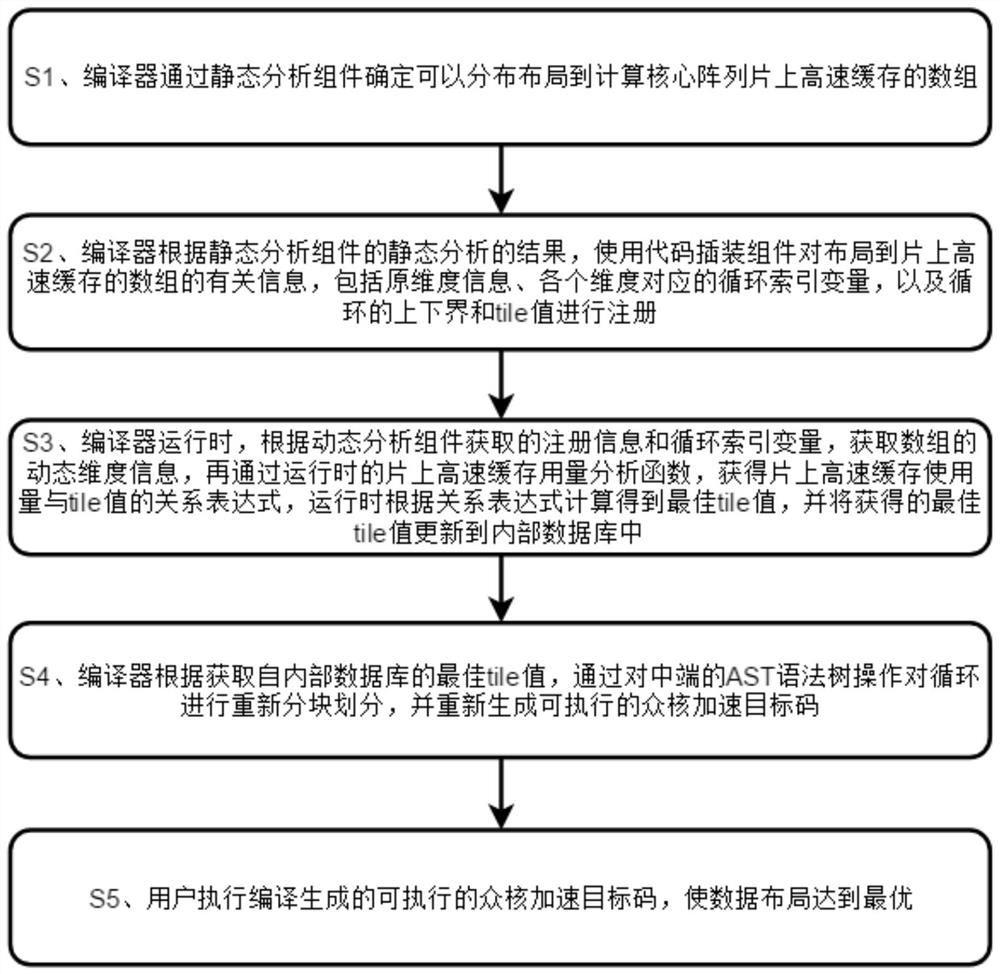

Method used

Image

Examples

Embodiment

[0025] Embodiment: A data automatic layout device for heterogeneous fusion many-core architecture, including the following components:

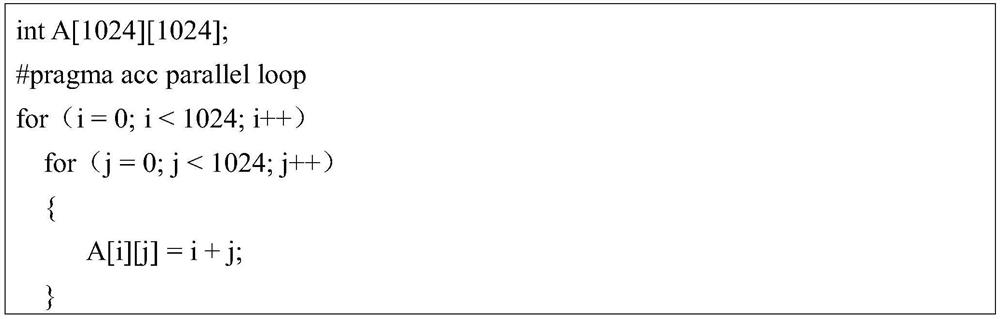

[0026] The static analysis component configured on the compiler is used to collect all array accesses in the acceleration area and analyze its data access form. If the access form of all access points of the array satisfies A[a*i+b], where A is the array name, a and b are constants, and i is a parallel loop variable, then the array belongs to the key data that needs to be arranged in the on-chip cache, and can be distributed and laid out in the on-chip cache;

[0027] The static analysis component is a functional module of the static analysis of the compiler. It mainly analyzes the array variables accessed in the acceleration area. First, it collects all array accesses in the acceleration area and analyzes its data access forms. If all access points access The forms all satisfy the form of A[a*i+b] (A is the array name, a and b are constants,...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More