Limited run branch prediction

A technology of transfer instructions and operation methods, applied in the direction of program control design, instruments, calculations, etc., can solve problems such as poor efficiency, and achieve the effect of high performance gain

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

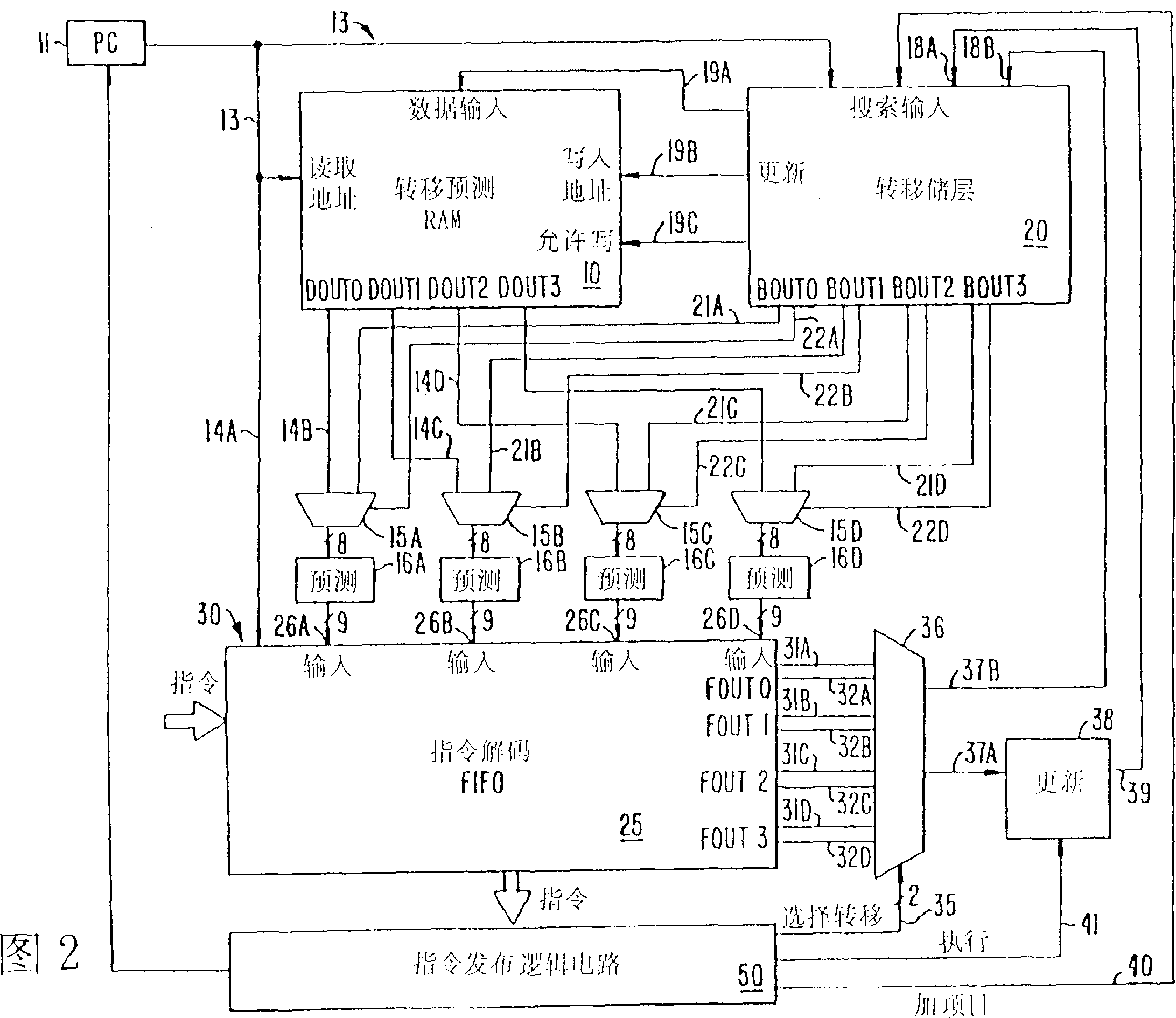

[0027] The preferred embodiment of the invention is associated with a superscalar processor. A superscalar processor fetches and issues multiple -- in this case as many as four -- instructions to the pipeline every clock cycle. Since not all processor elements are relevant to the present invention, some of these elements are not included in the description of the present invention. This is described in US Patent Application Serial No. 07 / 622,893, filed December 5, 1990, entitled "Processor Architecture" by Popescu et al.

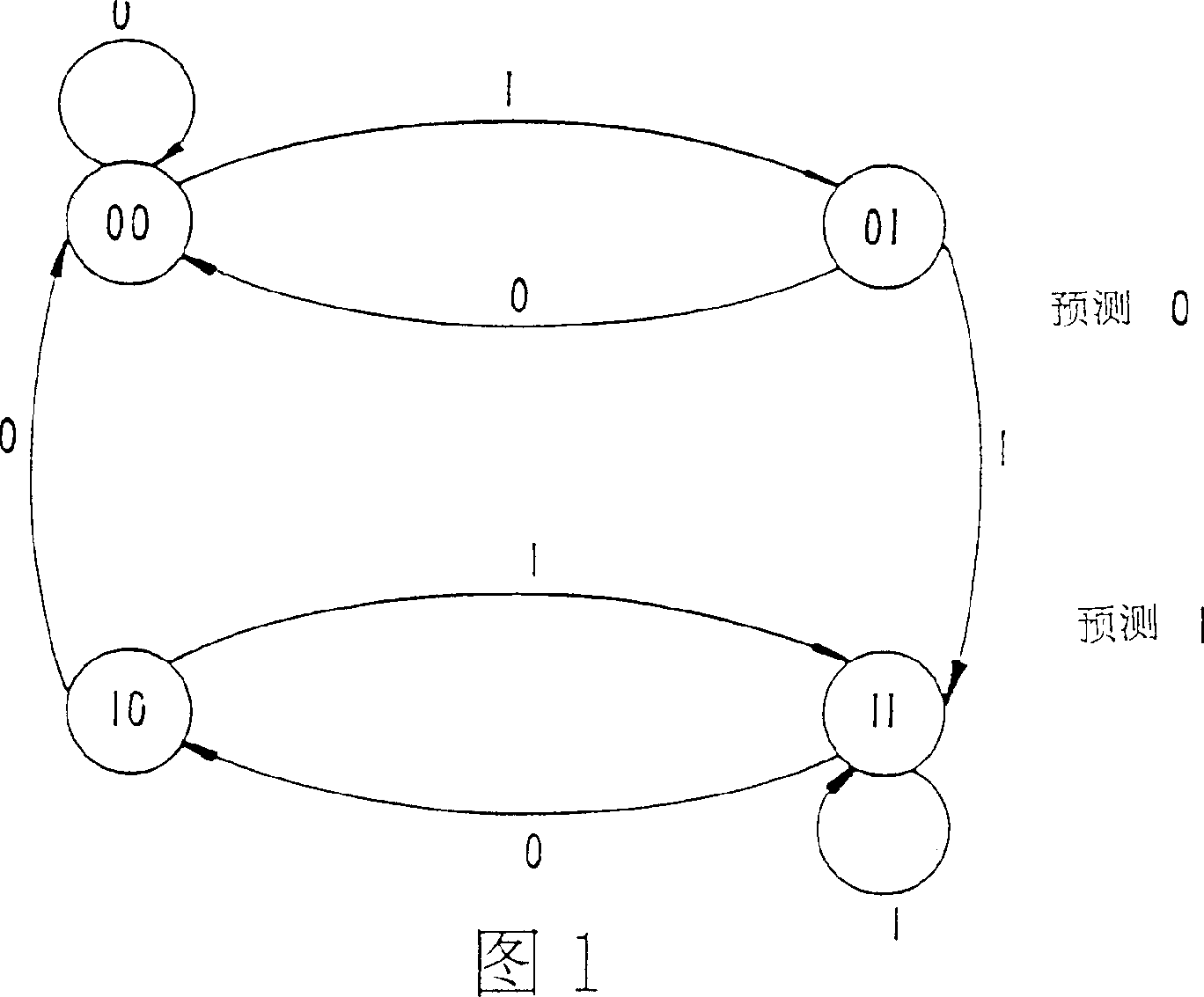

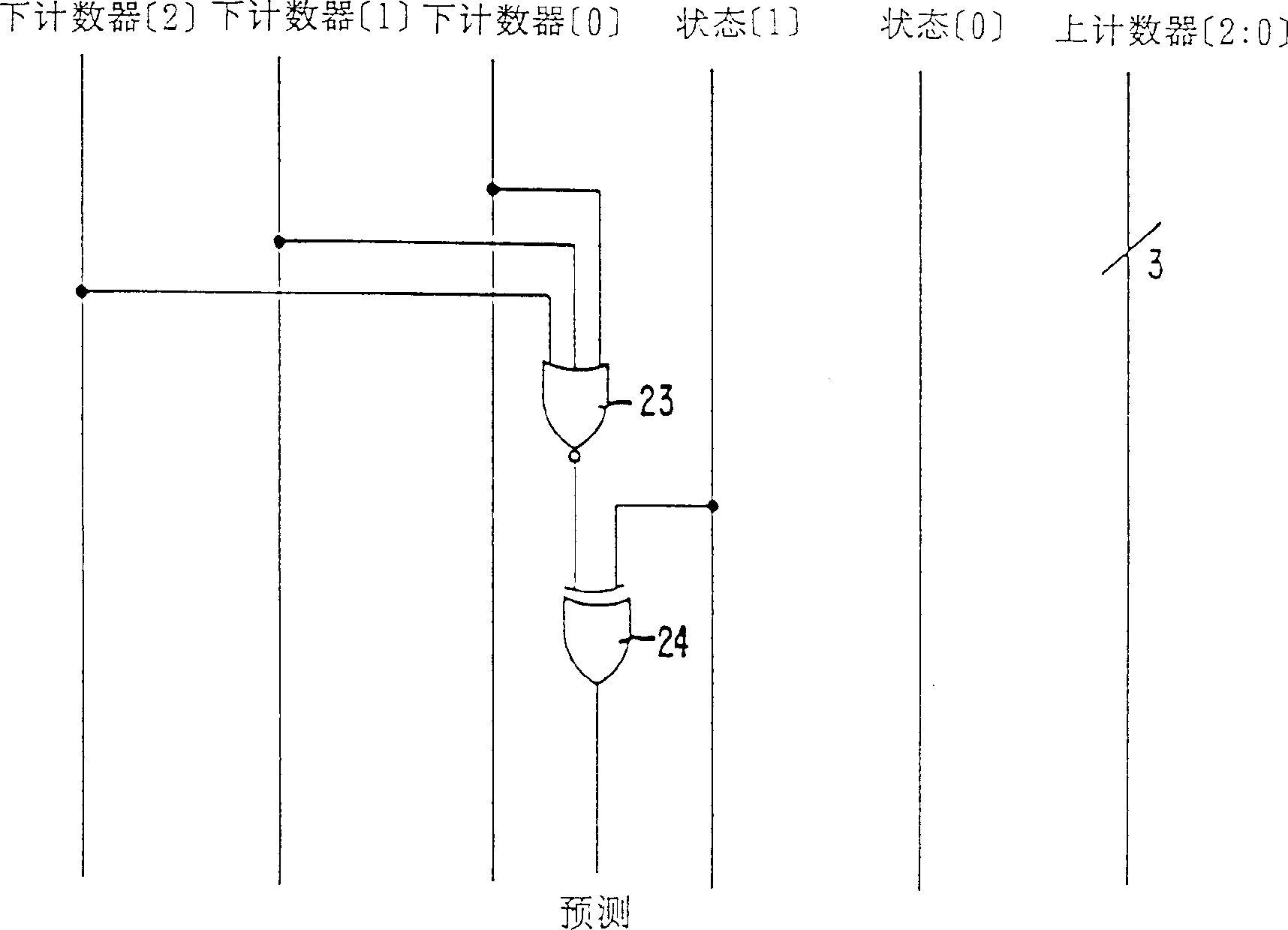

[0028] Regarding the prediction of branch instructions and the present invention, the execution history of all branches is stored in two structures, a branch prediction RAM 10 and a branch shelf 20 in the processor. Branch prediction RAM 10 stores the history of all branch executions up to the oldest pending predicted branch, but not including the oldest pending predicted branch itself. Branch store 20 maintains a history of all branch executions that are a ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More