Semiconductor equipment

A technology of semiconductors and components, applied in the field of semiconductor devices, can solve problems such as difficult clock signals

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

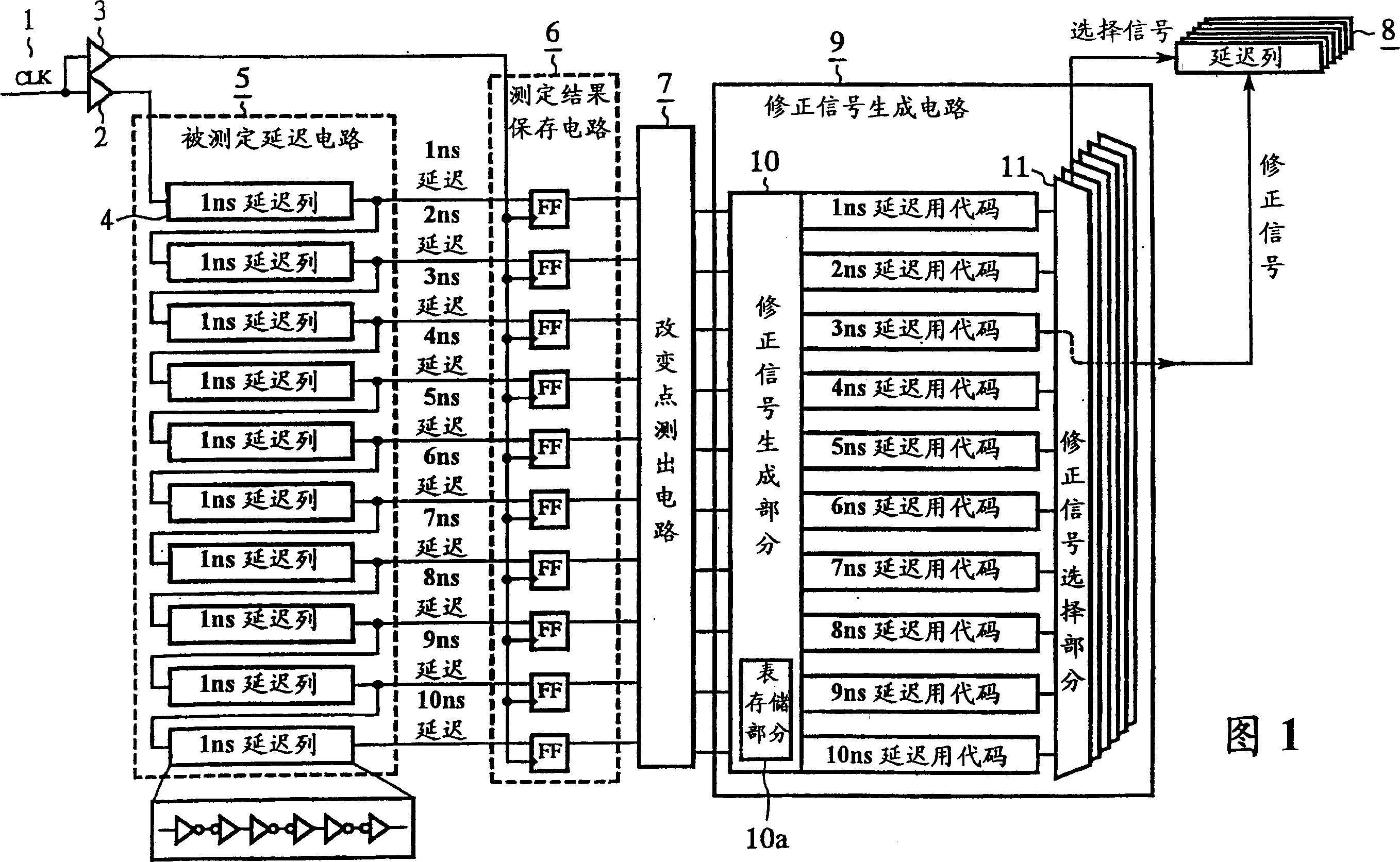

[0059] FIG. 1 is a configuration diagram of a delay adjustment circuit (semiconductor device) according to Embodiment 1 of the present invention. In the figure, 1 refers to the clock signal CLK whose period is determined, and 2 and 3 refer to the buffer units of the input clock signal CLK1.

[0060] 4 is a 1ns delay column (delay component), which is designed according to the requirement of adjusting the number of inverter chain elements to respectively achieve the 1ns set delay amount; 5 is the measured delay circuit (measured delay component), which is composed of multiple 1ns delays The columns 4 are connected in series, and after the clock signal CLK1 is input through the buffer unit 2, the phase of the clock signal CLK1 is changed by delaying the column 4 by 1 ns.

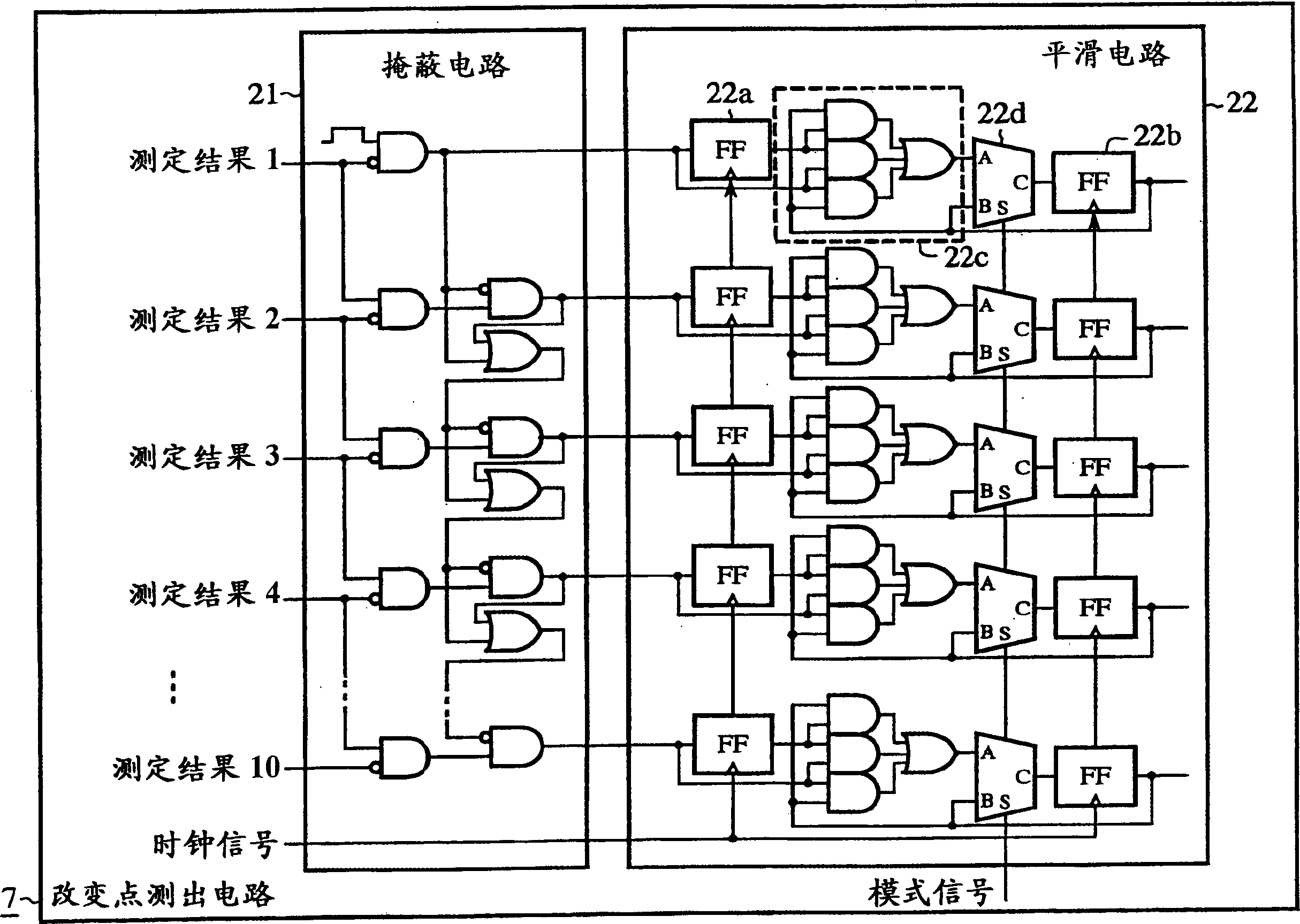

[0061] 6 is a measurement result storage circuit (measurement result storage unit), which is composed of a plurality of flip-flops (hereinafter referred to as FF) corresponding to each stage of the 1ns delay c...

Embodiment 2

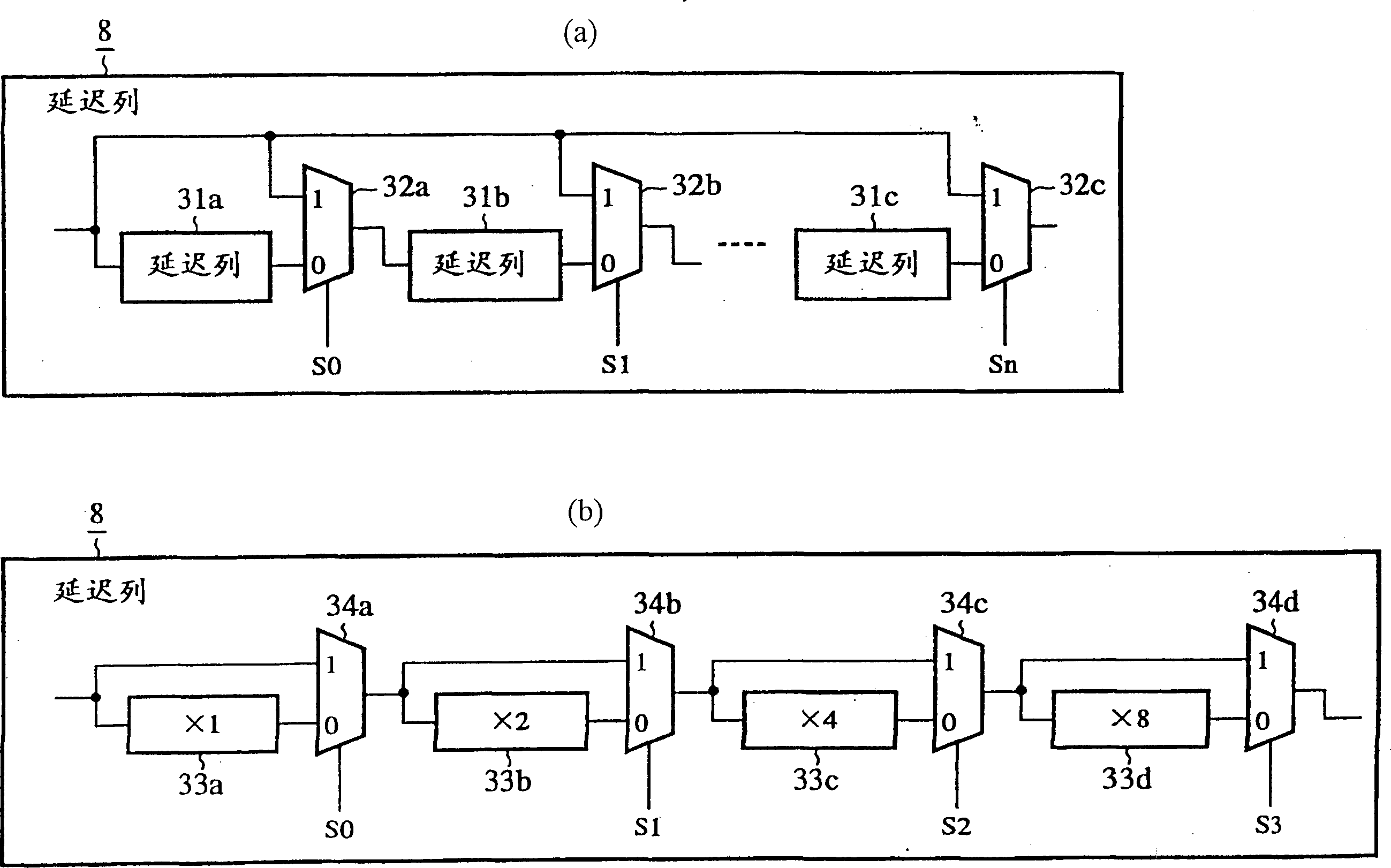

[0103] Fig. 7 (a) is the explanatory diagram of the look-up table used as the correction signal generating part of Embodiment 2 of the present invention, and Fig. 7 (b) is the explanatory diagram of the theoretical delay corresponding to the number of elements obtained according to the look-up table; Figure 8 It is a characteristic diagram of the theoretical delay amount corresponding to the number of elements represented by a curve.

[0104]The look-up table shown in Fig. 5 (a) of the above-mentioned embodiment 1 provides that the delay about 1-level transistors is 0.2 ns, and they are divided into 22 groups for each 5-level group from 20 levels to 125 levels to generate 0 ns~ 3ns correction signal case. Figure 5(a) shows the design-determined number of stages and the actual delay obtained by each group. When sampling the output delay of each fixed number of delay stages, the part with a large number of delay stages is The increment of each stage is small, and the increment...

Embodiment 3

[0109] 9 is a circuit diagram showing an application example of a non-overlapping two-phase clock signal generating circuit of the delay adjustment circuit according to Embodiment 3 of the present invention, and 40 in the figure is a non-overlapping two-phase clock signal generating circuit (non-overlapping two-phase clock signal generating means) . 41a to 41j refer to inverters, 42a and 42b refer to "NAND" circuits, and 43a to 43h are selectors (delay components) which are set as feedback delay columns of the non-overlapping two-phase clock signal generating circuit 40 and whose number of connections can be adjusted freely. ). 44 is a decoder circuit that decodes the correction signal generated by the correction signal generation circuit 9 and is switched by the selectors 43a to 43h. Other structures are the same as those shown in Figure 1.

[0110] Next, the operation will be described.

[0111] In the third embodiment, an application example of the non-overlapping two-ph...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More