Processor power management and bus optimization method

A power management and processor technology, applied in the direction of program loading/starting, program control devices, etc., can solve problems such as complicated boot procedures and prolonged system boot time

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

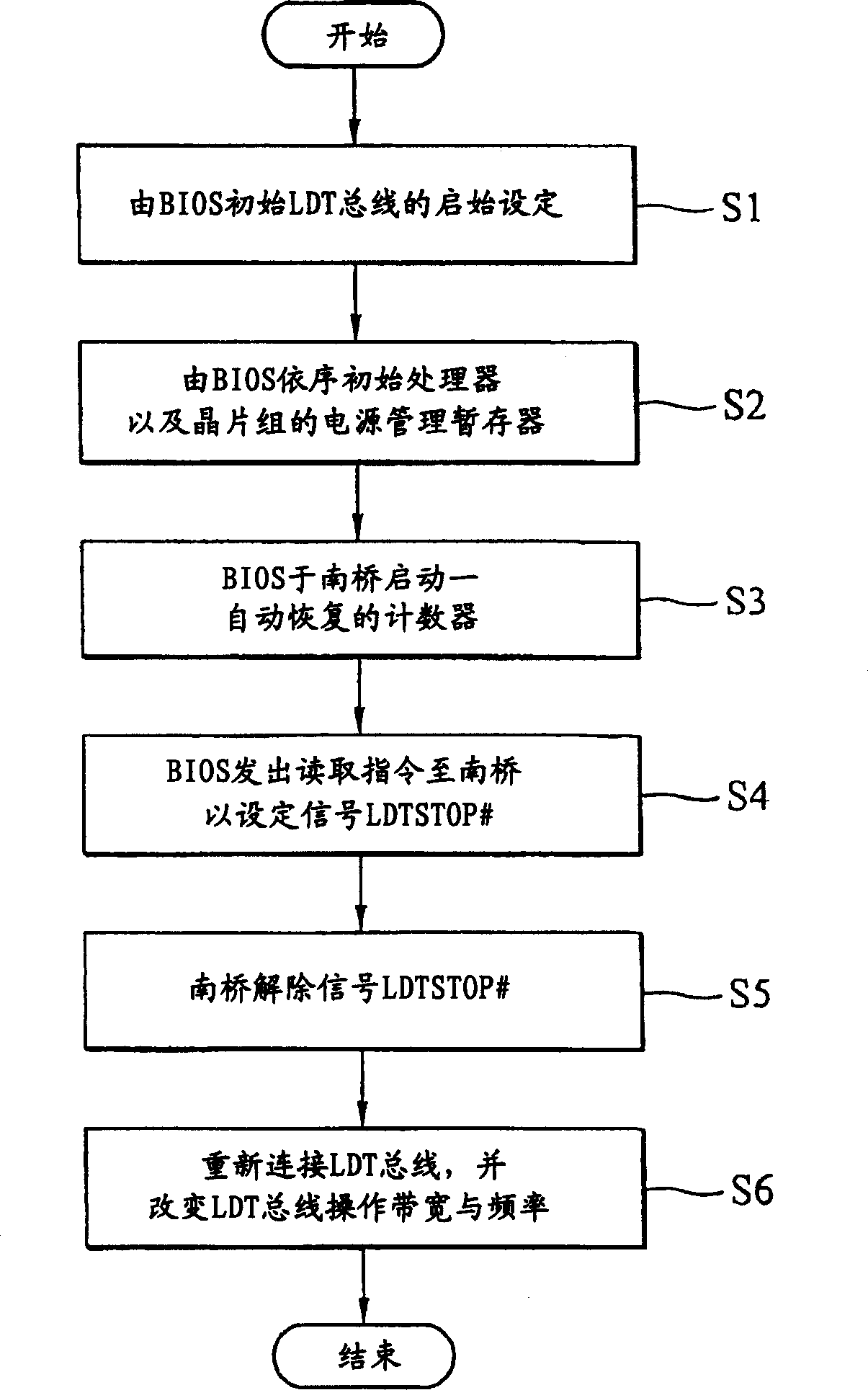

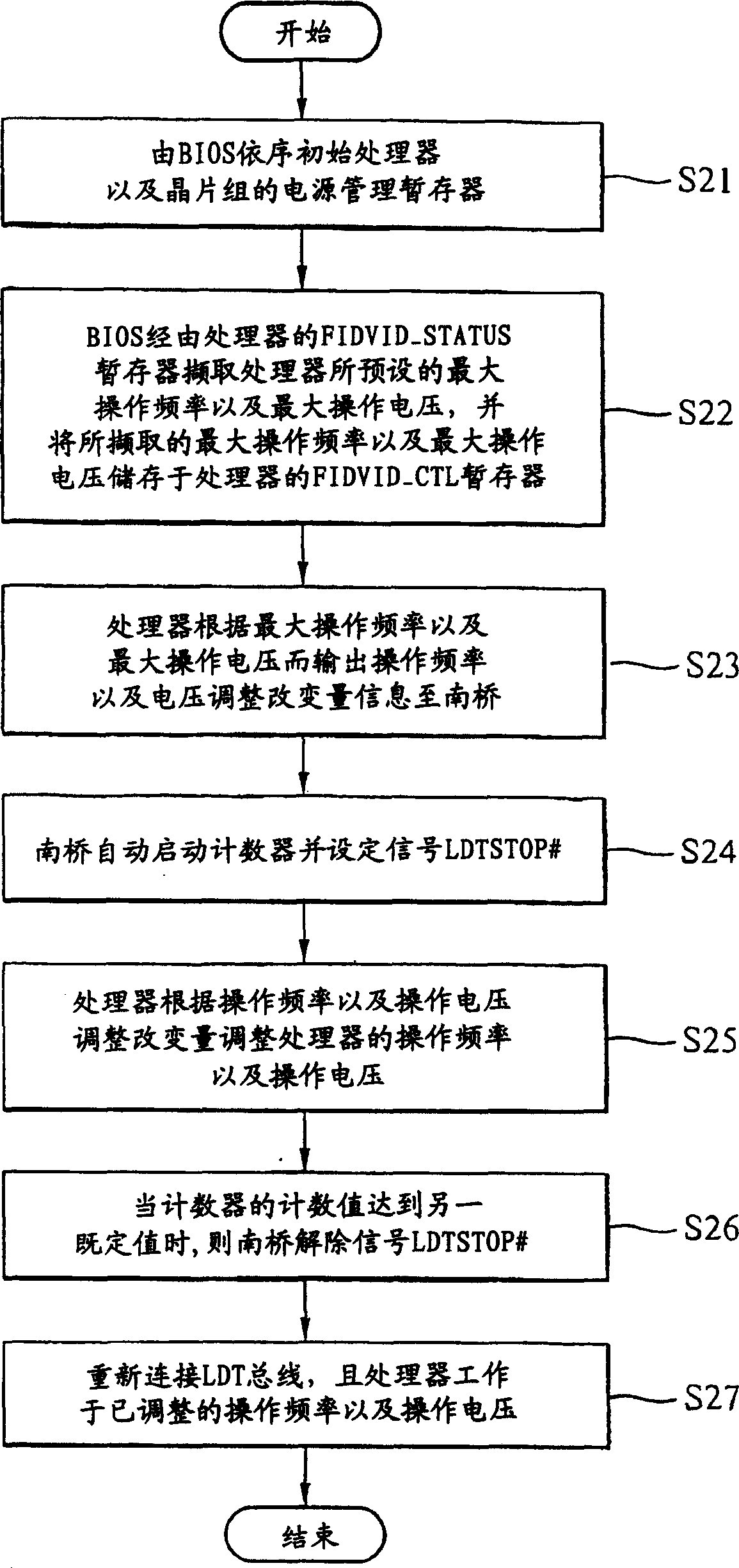

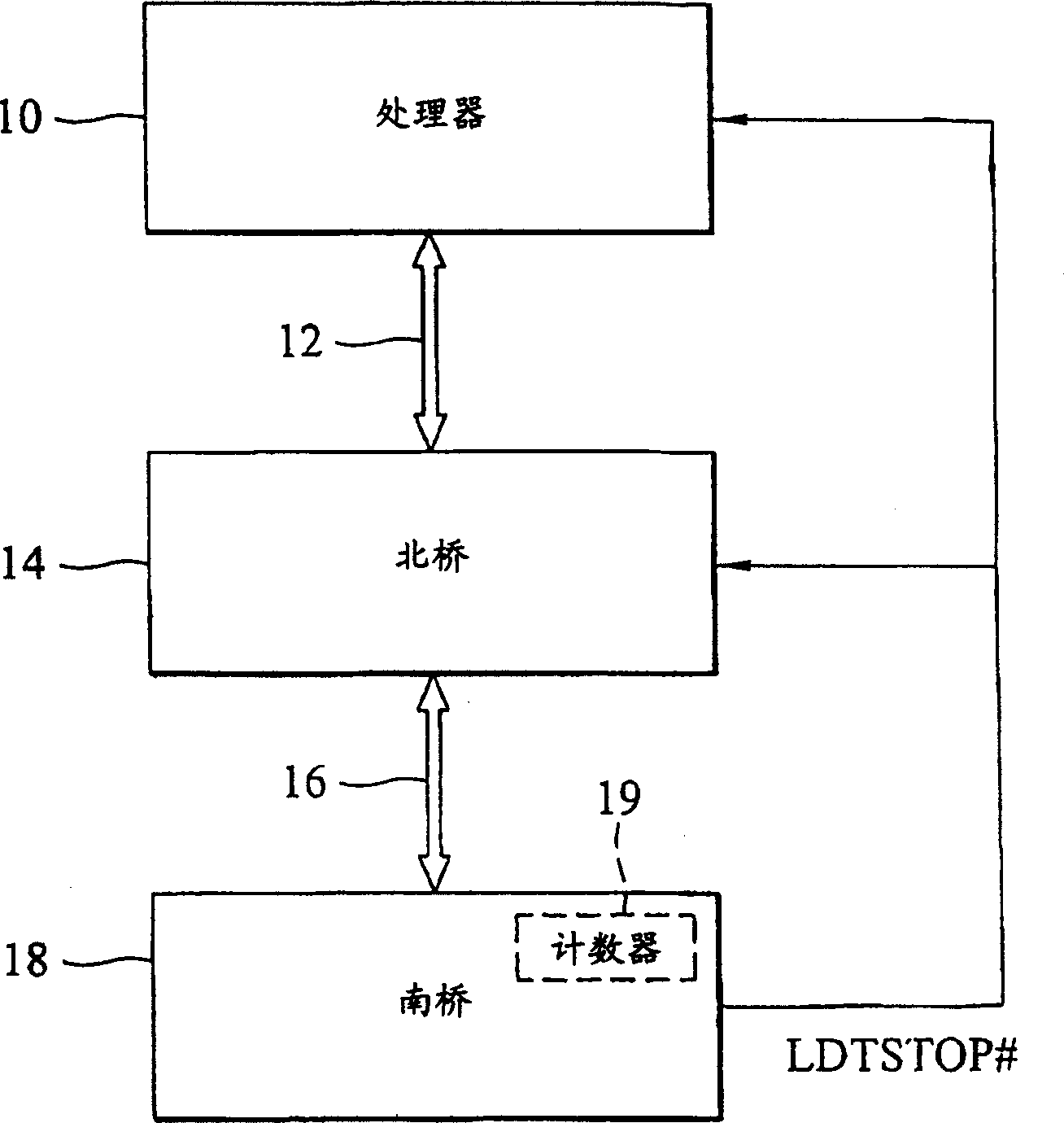

[0025] refer to image 3 , image 3 It is a diagram showing the architecture of a computer system with an LDT bus. As shown in the figure, there is an LDT bus 12 between the processor 10 and the north bridge 14 . Here, the processor is the K8 CPU manufactured by AMD as an example. There is another bus 16 between the north bridge 14 and the south bridge 18 . When the processor power management program and the bus optimization program are to be executed, the LDT bus 12 between the processor 10 and the north bridge 14 must perform interruption and reconnection actions. It is controlled by the level change of the signal LDTSTOP#. The level of the signal LDTSTOP# is the first level in the normal situation (take the high level as an example), when the south bridge pulls down the level of the signal LDTSTOP# to the second level (take the low level as an example), the It is called the assert signal LDTSTOP#, and when both the processor 10 and the north bridge 14 receive the asser...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More