Carry save adder and its system

A technology of adder and full adder, applied in the field of carry-storage adder, which can solve problems such as delay

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

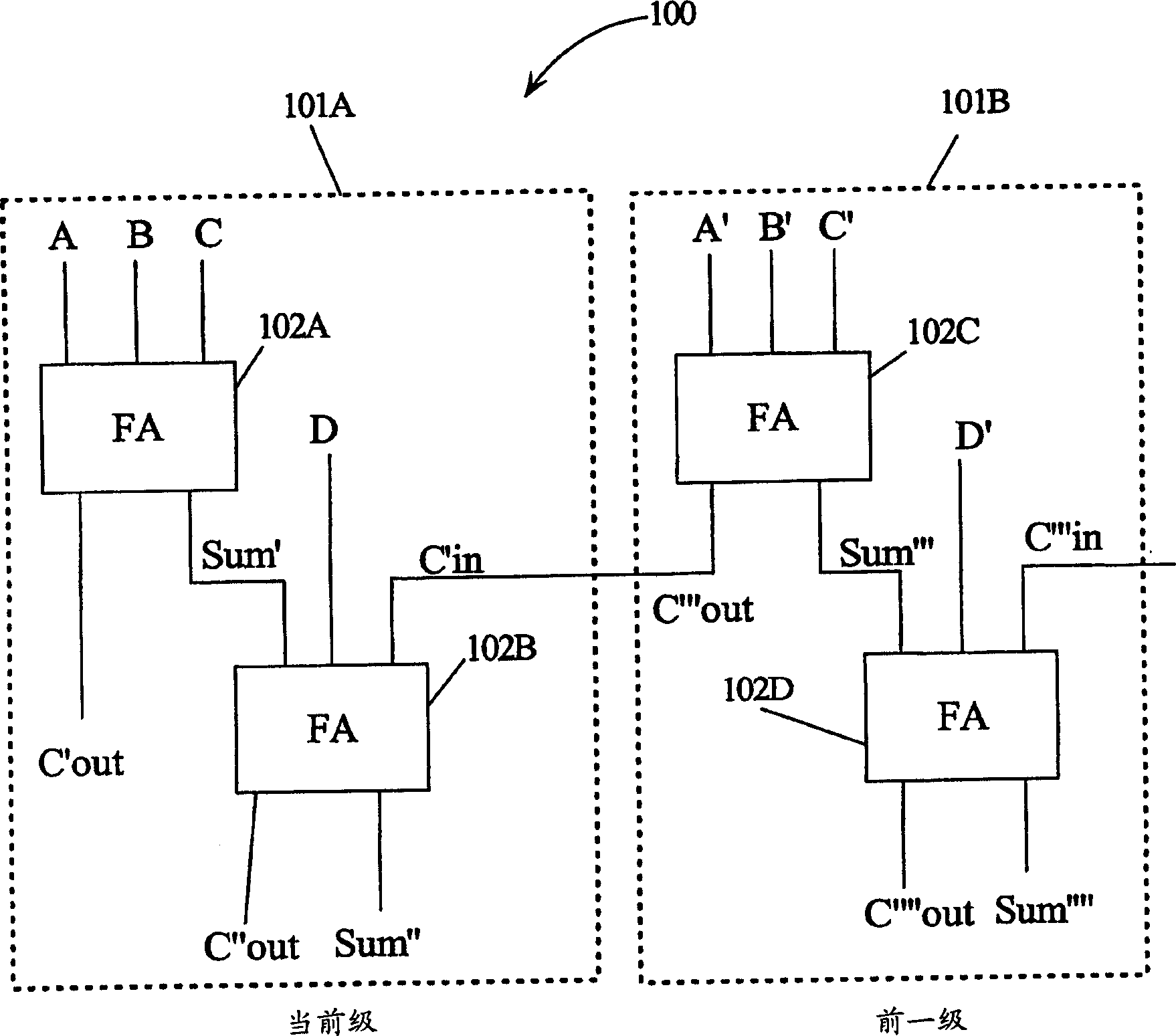

[0018] The present invention includes a 4-to-2 carry store adder configured to output sums and carry bits. In one embodiment of the present invention, the 4-to-2 store adder may include a lower order full adder coupled to a higher order full adder. The carry-save adder may also include a logic unit coupled to the higher-order full adder, wherein the logic unit is configured to generate a carry, which is to be input to the higher-order full adder, which will typically be received from a carry-save adder at a previous stage generate. By generating this carry (input bit) at the current stage, rather than at the previous stage, the delay of the input bit to the high order full adder is reduced. By reducing the delay of the input bit being input to the higher order full adder, the delay of the output sum and the carry of the higher order full adder is reduced, thereby improving the performance of the carry store adder.

[0019] Although the invention is described with reference t...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More