Sense mechanism for microprocessor bus inversion

一种总线、反相器的技术,应用在快速估测一数据输出位群组的状态改变领域,能够解决耗损处理时间等问题

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

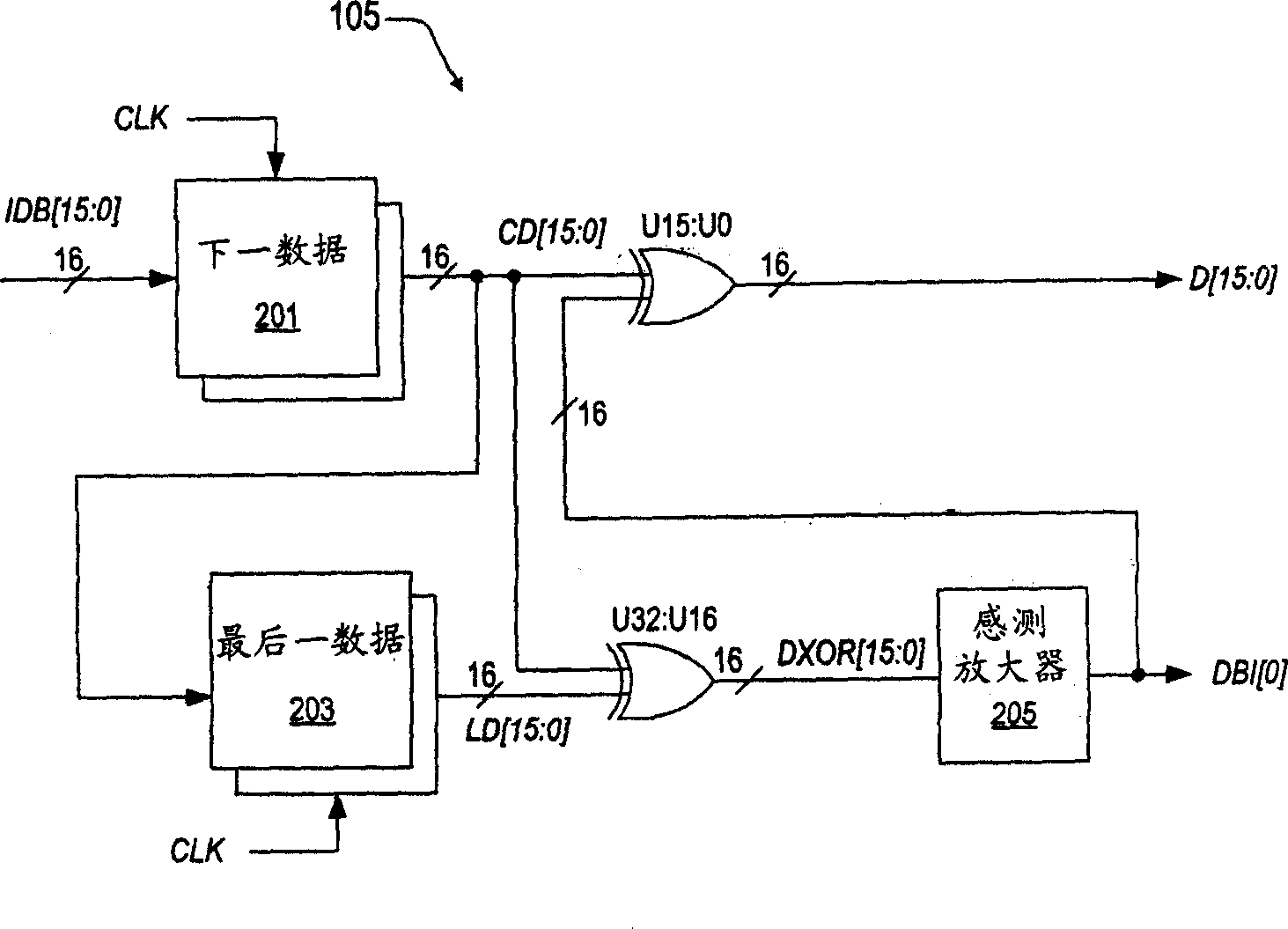

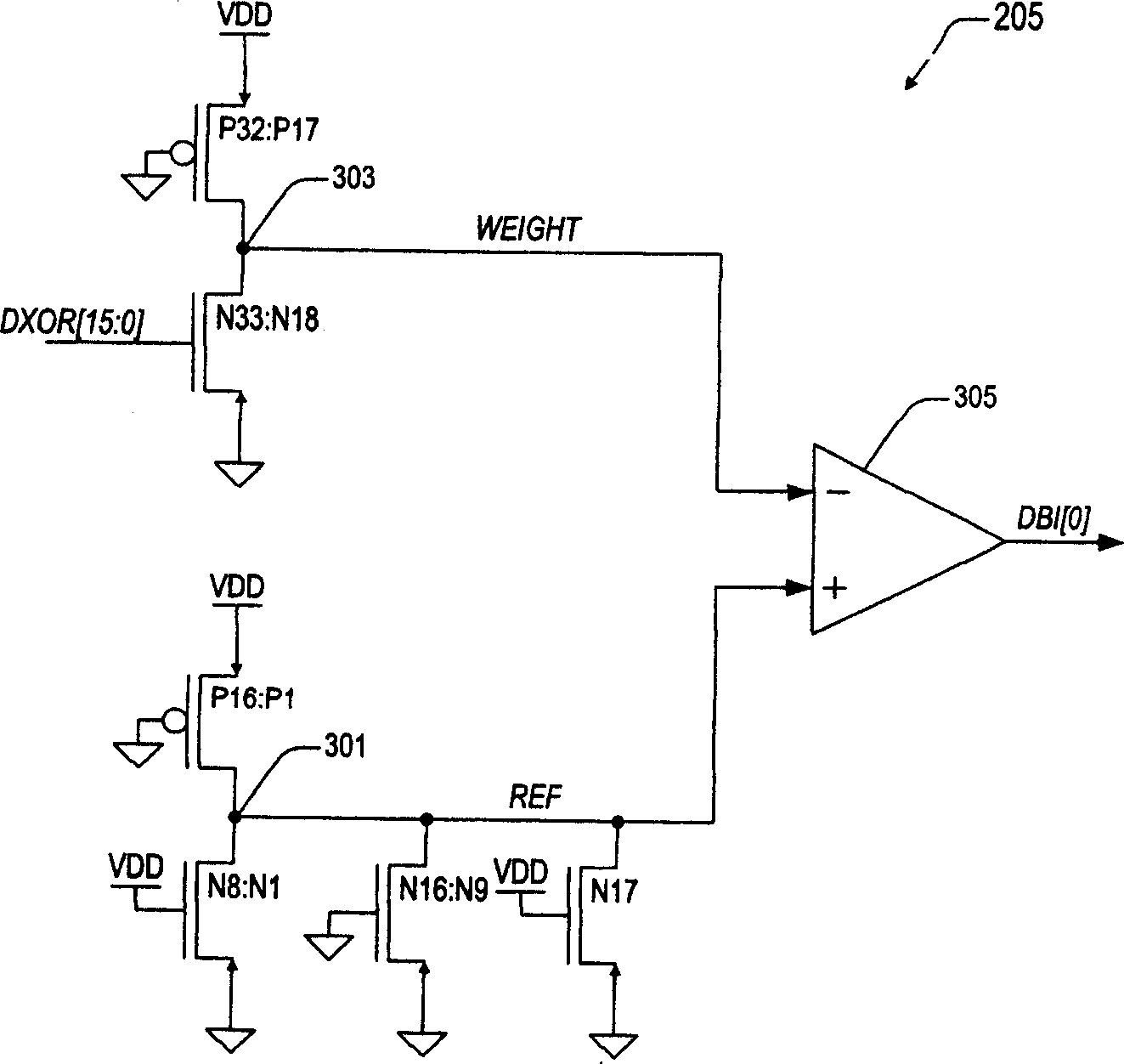

[0023] The present invention estimates the change state of a data bus bit group based on the judgment of the known data bus inversion, which is beneficial to limit the noise on the data bus of logic circuits such as microprocessors or processors, such as It must be restricted according to the x86 protocol. Therefore, the present invention proposes a microprocessor bus inversion sensing mechanism, which can reduce the time required for judging bit state changes due to the use of an analog adder. The following will cooperate with Figure 1 to Figure 3 The sensing mechanism is explained as follows.

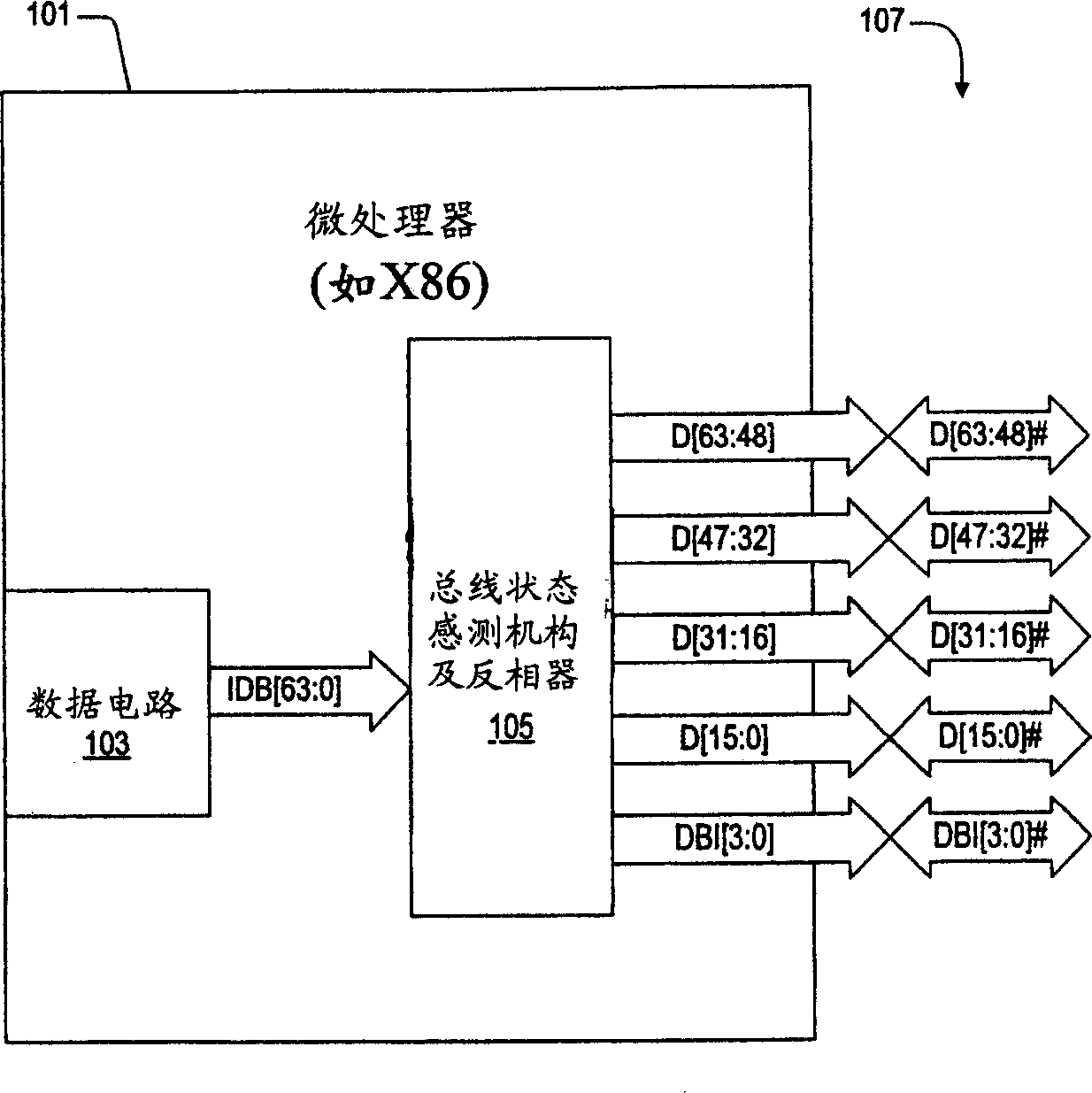

[0024] figure 1 A simplified block diagram of a microprocessor incorporating an example of a bus inversion sensing mechanism in accordance with an embodiment of the present invention. refer to figure 1, the microprocessor 101 can be an x86 series microprocessor, but the present invention can be any logic circuit that can perform data bus inversion. The microprocessor 101 is a chi...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More