Circuit and method for testing embedded dram circuits

A memory and tester technology, applied in the field of circuits, embedded dynamic random access memory circuits

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0030] Please refer to the attached drawings and the detailed description of the preferred embodiments of the present invention. In the following description, known functions or structures are not described in detail to avoid obscuring the content of the present case.

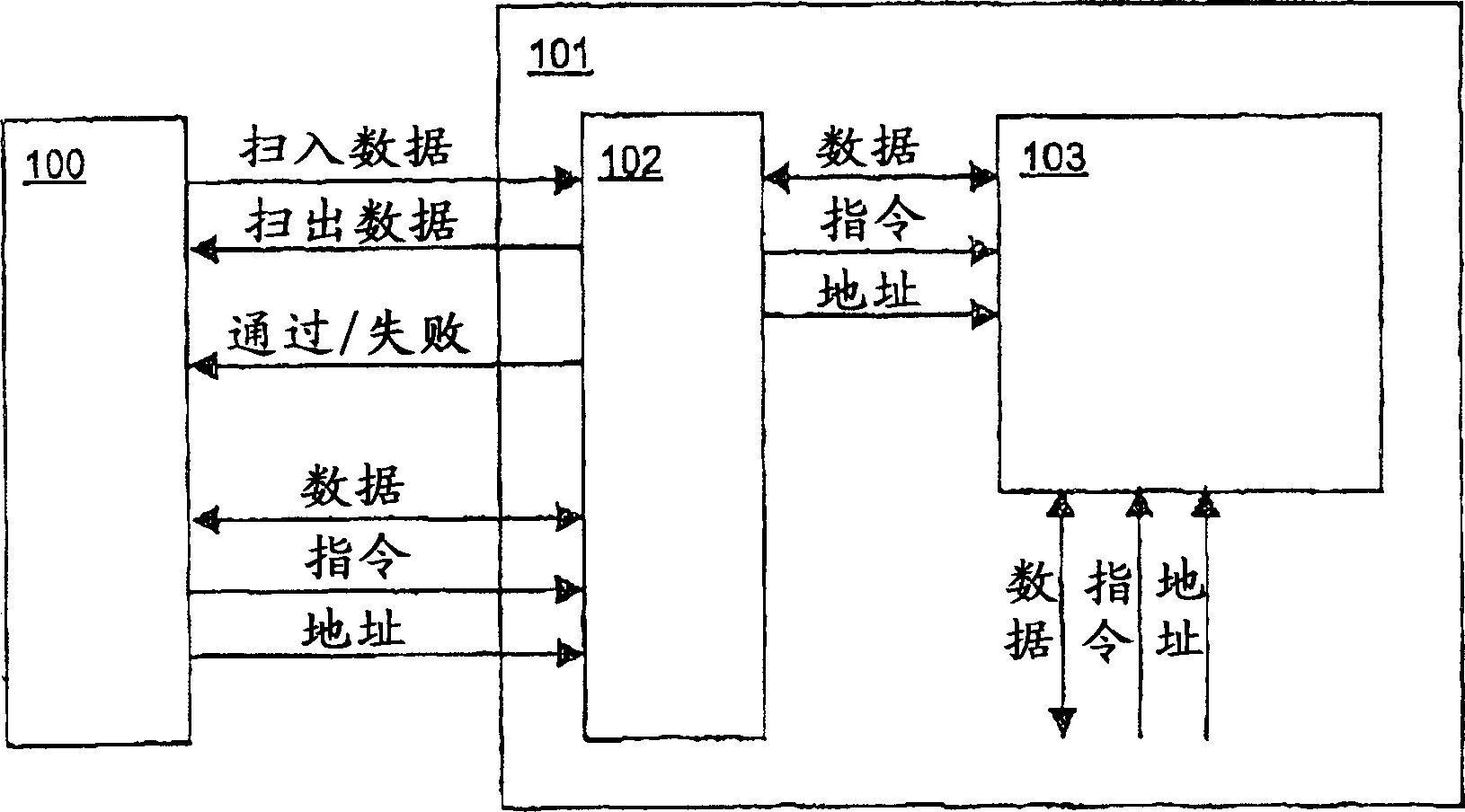

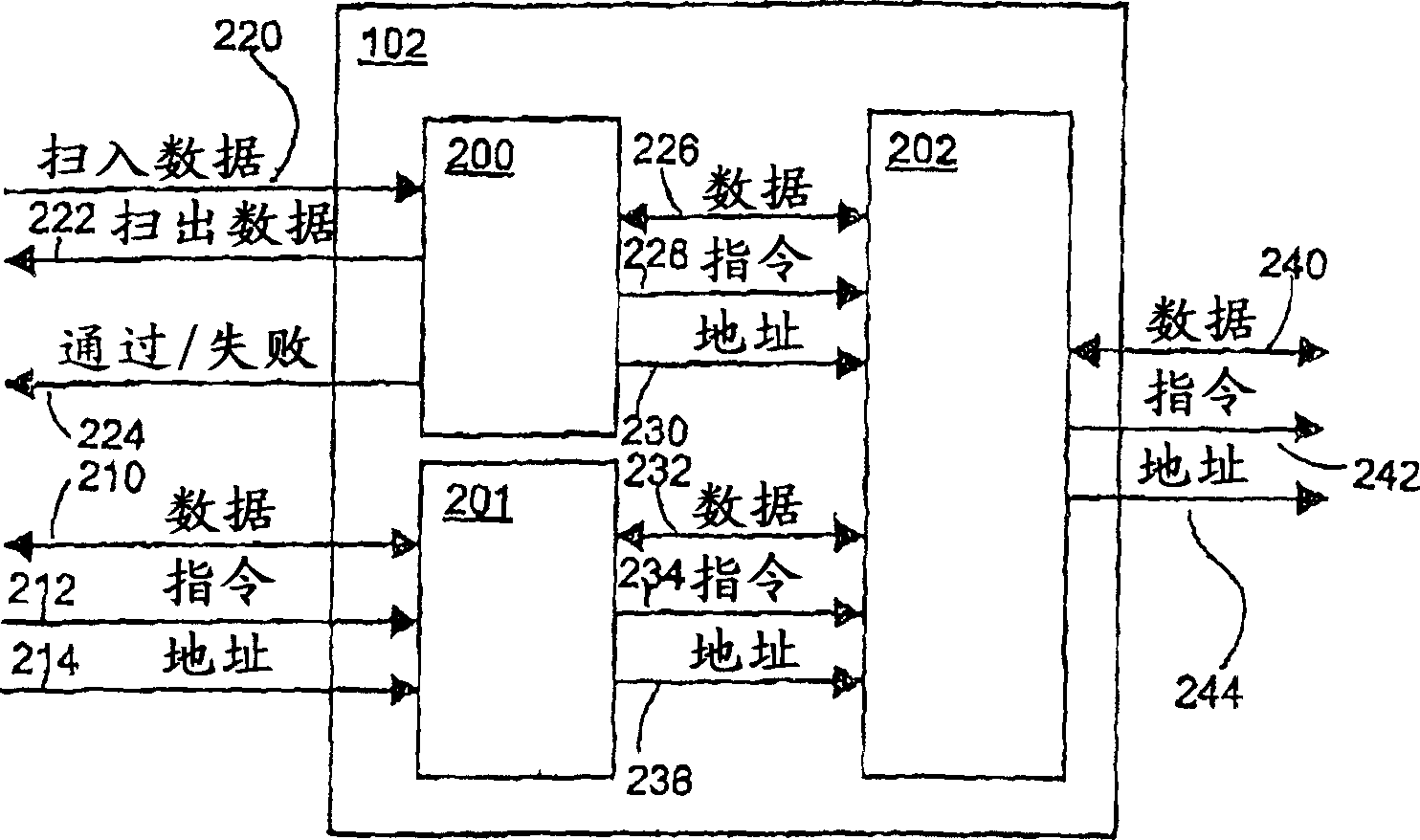

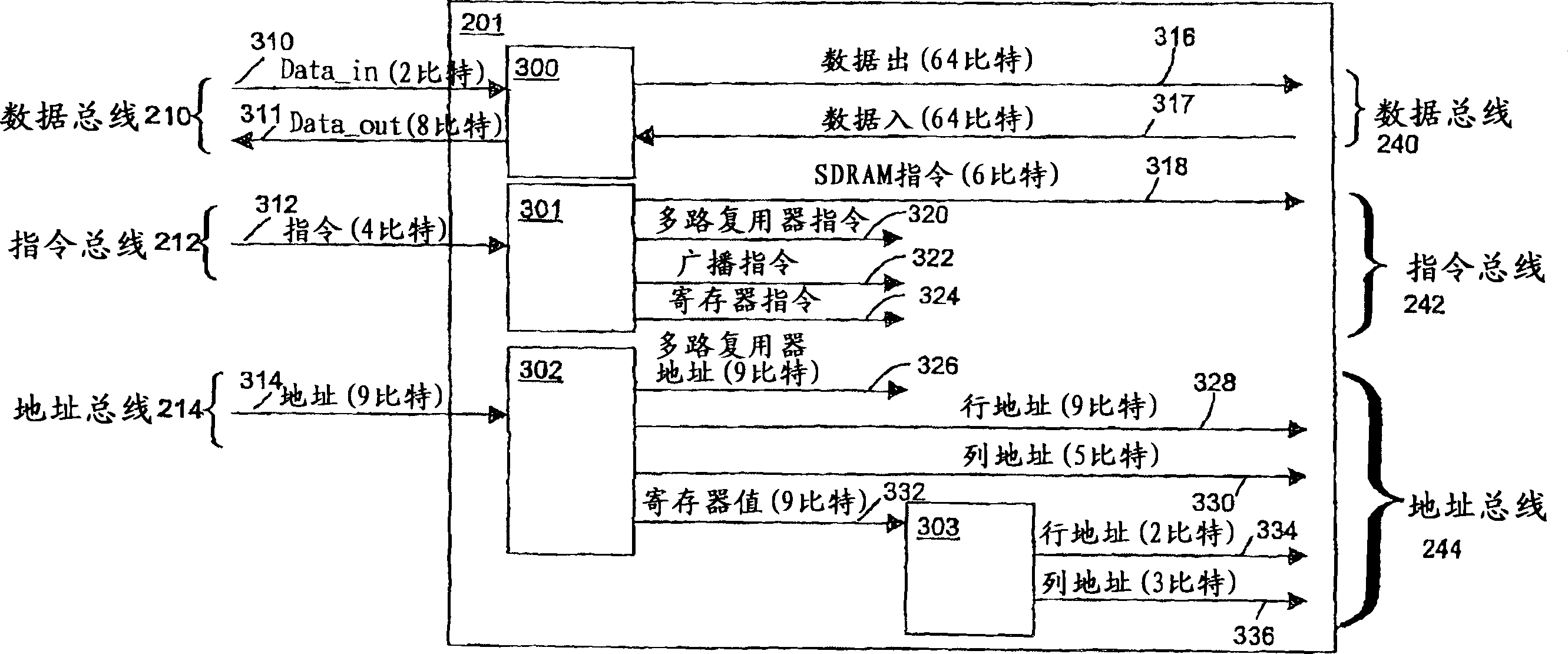

[0031] The present invention provides a circuit and method for testing an embedded DRAM (eDRAM) circuit through a test controller with direct access mode (DA mode) logic. figure 1 is a block diagram illustrating a test system including a memory device, such as an eDRAM, including a test controller with direct access mode logic, in accordance with the present invention. see figure 1, a memory or logic tester 101 is coupled to an ASIC (Application Specific Integrated Circuit) 101 , which includes a test controller 102 and at least one embedded DRAM (eDRAM) 103 . The eDRAM 103 includes a plurality of word lines disposed at intersections of the word lines and bit lines. The test controller 102 further includes...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com